Les contenus liés au tag DDR4

Afficher sous forme de : Titre | FluxLe JEDEC évoque la DDR4

Hynix produit ses premières DDR4

Samsung premier sur la DDR4

La DDR4 se dévoile

Le JEDEC évoque la DDR4

![]() Le comité de standardisation dédié à la mémoire, le JEDEC, vient de publier quelques détails sur les pistes de travail empruntées pour le futur standard mémoire DDR4. La spécification est toujours en cours d'élaboration et le JEDEC annonce qu'elle devrait être terminée d'ici à mi-2012 (ce qui n'empêche pas des guerres d'annonces entre Samsung et Hynix

). C'est en soit un retard de plus puisque l'on attendait la finalisation de la spécification avant la fin de l'année. Si le nouveau délai est tenu, cela marquera sept années entre la publication des standards DDR3 et DDR4, là où quatre années séparaient les publications des standards DDR, DDR2 et DDR3.

Le comité de standardisation dédié à la mémoire, le JEDEC, vient de publier quelques détails sur les pistes de travail empruntées pour le futur standard mémoire DDR4. La spécification est toujours en cours d'élaboration et le JEDEC annonce qu'elle devrait être terminée d'ici à mi-2012 (ce qui n'empêche pas des guerres d'annonces entre Samsung et Hynix

). C'est en soit un retard de plus puisque l'on attendait la finalisation de la spécification avant la fin de l'année. Si le nouveau délai est tenu, cela marquera sept années entre la publication des standards DDR3 et DDR4, là où quatre années séparaient les publications des standards DDR, DDR2 et DDR3.

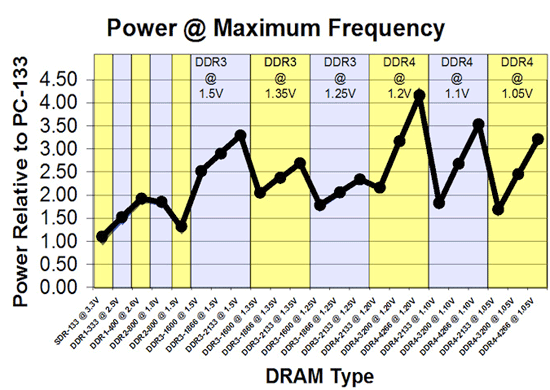

Si la tension d'alimentation principale de la mémoire devrait varier avec le temps (de 1.2 à 1.05V, de la même manière que la DDR3 aura évolué de 1.5 à 1.2V), la DDR4 imposera une tension pour les I/O (VDDQ) qui restera fixe quoiqu'il arrive, de 1.2V. Le but étant de simplifier les designs et d'assurer la compatibilité future plus facilement. La VDDQ jouera également un rôle dans le nouveau système de terminaison.

Afin de réduire la consommation et de limiter le bruit sur le bus, la DDR4 implémentera pour la première fois le concept du DBI (Data Bus Inversion). L'idée est de limiter au maximum les inversions complètes, par exemple passer d'une transmission de 1111 à 0000 puis de nouveau 1111. Via un bit supplémentaire, le DBI permet d'indiquer que la valeur du milieu doit être comprise comme inversée. En pratique ce sont donc des valeurs de 1111, 1111 et 1111 qui seront transmises. Le système avait déjà été intégré à la GDDR4 et 5, il évite dans tous les cas que plus de la moitié des valeurs changent entre deux transferts successifs.

Autre nouveauté notable, la largeur des transferts redevient variable. Si la DDR3 se limitait à des transferts d'une largeur de 64 bits (x8), la DDR4 rajoute un peu plus de flexibilité avec trois largeurs (32, 64, 128 bits).

La question de l'intégrité des transferts, généralement réglée de manière globale avec l'ECC se verra affublée d'un système supplémentaire de CRC qui pourra être utilisé ponctuellement, par exemple uniquement sur certaines opérations d'écritures. Un mécanisme de détection de la parité au niveau des puces est également prévu.

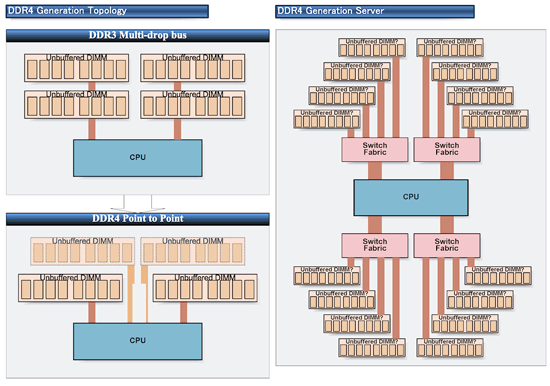

En ce qui concerne la gestion des canaux et les performances, le communiqué ne s'avance que très peu. La DDR4 à toujours pour objectif de doubler les transferts par broche par rapport à la DDR3 (de 0.8/1.86 GT à 1.6/3.2 GT). En ce qui concerne la topologie, s'il semblait acquis que le concept de canaux gérant plusieurs barrettes disparaisse au profit d'un modèle point à point (l'équivalent de multiples canaux ne gérant qu'une barrette à la fois, voir cette actualité), aucune précision supplémentaire n'a été apportée.

La prochaine réunion de travail du JEDEC se tiendra le 12 septembre.

Hynix produit ses premières DDR4

3 mois après Samsung, c'est au tour de Hynix d'annoncer ses premières puces de DDR4. Gravées en 3xnm, ces puces de 256 Mo sont utilisées pour commencer sur une barrette de 2 Go ECC au format SODIMM.

Il s'agit de puces DDR4-2400, alors que Samsung s'était limité au mode DDR4-2133 et que la DDR4 devrait monter officiellement jusqu'en DDR4-3200, soit le double de bande passante que la DDR3-1600. A cette vitesse, Hynix conserve la tension de 1.2v qui sera la norme en matière de DDR4.

Il faut toutefois préciser que la DDR4 n'en est qu'a ses balbutiements puisque ce standard ne devrait être finalisé qu'au second semestre par le JEDEC. Hynix indique d'ailleurs qu'il prévoit de débuter la production en volume dans plus d'un an, au second semestre 2012 ! Selon iSuppli, la DDR4 devrait représenter 5% du marché de la DRAM en 2013 et 50% en 2015, contre 71% pour la DDR3 en 2012 et 49% en 2014.

Samsung premier sur la DDR4

Alors que le standard nest pas encore finalisé par le JEDEC, Samsung annonce quil a terminé le mois le dernier le développement du premier module de DDR4. Fonctionnant en DDR4-2133 à seulement 1.2v, ces barrettes utilisent des puces gravées en 30nm.

Samsung indique que ses puces de DDR4 atteindront des débits de données de 1.6 à 3.2 Gbps, soit le double de ses puces DDR3. Les modules 2 Go DDR4 Samsung ont déjà été échantillonnés à fabricant de contrôleur mémoire pour test, et Samsung annonce travailler activement avec le JEDEC afin de finaliser le standard DDR4 avec le JEDEC durant le second semestre.

Samsung était déjà le premier sur la DDR en 1997, sur la DDR2 en 2001 et sur la DDR3 en 2005.

La DDR4 se dévoile

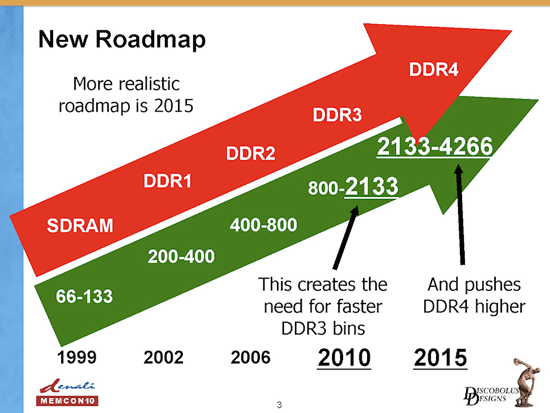

PC Watch publie un ensemble de documents liés à la DDR4 publiés à loccasion du MemCon10, une conférence dédiée à la mémoire qui a eu lieu fin juillet. Pour le moment, la norme DDR4 nest pas finalisée, ce devrait être le cas courant 2011, pour une introduction en 2012, sa démocratisation nétant pas prévue avant

2015 ! On a donc le temps de voir venir.

Comme à chaque génération de DDR, la DDR4 devrait doubler la bande passante disponible à une fréquence de cellule mémoire identique. Leur organisation interne sera donc modifiée de manière à pouvoir doubler la bande passante afin datteindre les modes DDR4-1600, DDR4-2133, DDR4-2666, DDR4-3200 et même DDR4-4266 ! Côté tension, alors que la DDR3 fonctionne en 1.5V, avec des versions basse tension à 1.35V, il est question de 1.2V par défaut avec la possibilité de descendre jusquà 1.05V, ce qui permettra de ne pas faire exploser la consommation malgré cette hausse de débit.

Autre changement important, le bus utilisé devrait être de type point à point, ce afin de supporter la hausse de la fréquence du bus mémoire externe. De fait, il ne sera plus possible dutiliser plus dune barrette mémoire sur un même canal, à moins dutiliser des puces supplémentaires faisant office de switch et qui devraient être intégrées sur les plates-formes serveur.

Voilà qui poussera les fabricants de mémoire à concevoir des barrettes de plus en plus denses, ce qui devrait être possible avec larrivée des die mémoire de 4 Gb et 8 Gb prévus pour 2011/2012 et 2014/2015 et qui devrait démocratiser les barrettes de 8 et 16 Go.