Les contenus liés aux tags GlobalFoundries et 7nm

Afficher sous forme de : Titre | FluxNouvel accord WSA entre AMD/GlobalFoundries

Premières puces en 7nm pour IBM !

12nm et EUV à 7nm pour TSMC

TSMC a publié hier ses résultats financiers pour le dernier trimestre 2016. Le fondeur taiwannais a annoncé pour ce trimestre un revenu brut de près de 7.8 milliards d'euros, en hausse de 28.8% par rapport à la même période sur l'année précédente. Sur la totalité de l'année 2016, TSMC aura augmenté son revenu de 12.4% par rapport à 2015.

Pour 2017, TSMC s'attend à voir ses revenus progresser de "seulement" 5 à 10% (ce qui n'a pas manqué de décevoir les analystes financiers). Lors de la présentation des résultats, quelques informations supplémentaires ont été données.

Morris Chang, Chairman de TSMC s'est lancé dans quelques prédictions pour le marché 2017, s'attendant à voir le marché des smartphones grimper de 6% en unités, et celui du PC se contracter de 5% en unités également (il envisage également un déclin de 7% sur les tablettes tout en voyant le marché Internet of Things progresser de 34%).

Sur le 16/14nm, Morris Chang estime que la part de marché de TSMC est entre 65 et 70%, en dessous de ses attentes (TSMC dispose encore de 80% du marché sur le 28nm par exemple). Toujours poétique, le Chairman voit dans le 10 et le 7nm un "ciel bleu" par rapport à la compétition.

Quelques détails plus techniques ont été donnés, notamment par rapport à un "12nm" qui avait été évoqué ici ou là dans la presse. En pratique, TSMC travaille sur une nouvelle version de son process 16nm (une quatrième après les 16FF, 16FF+ et 16FFC) qui incorpore des améliorations importantes de densité. L'appellation commerciale exacte n'a pas été donnée, et on ne sait pas exactement quand elle sera disponible. On s'attendra dans quelques semaines à une annonce officielle, même si TSMC à confirmé aujourd'hui l'existence de ce "12nm".

Pour le 10nm, si le début de production est bien en cours, le gros du volume se situera sur la seconde partie de l'année (coïncidant avec le lancement des prochains iPhones dont le SoC utilisera le 10nm TSMC).

Sur le 7nm, plus de 20 sociétés travailleraient déjà sur des designs pour l'année prochaine, un chiffre qui devrait doubler dans l'année. Sur la question du 7nm en lui même, nous nous étions interrogés sur la manière dont le constructeur augmenterait la densité. Pour rappel, TSMC s'engage à lancer la production du 7nm dès la fin de l'année, il s'agira du node qu'utiliseront la majorité de ses clients, le 10nm devrait avoir une durée de vie courte et être réservé à quelques gros clients.

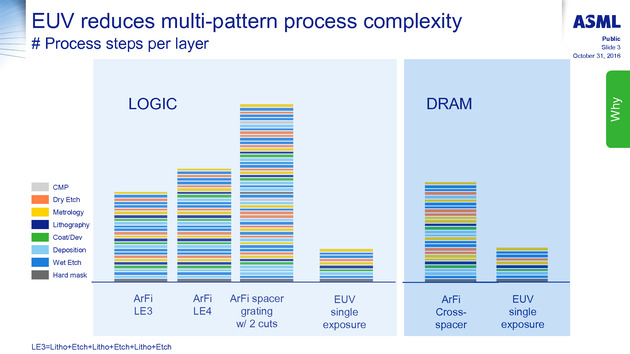

Le 10nm rappelle d'une certaine manière le 20nm de TSMC, lui aussi utilisé par des gros clients uniquement avant un passage rapide au 16nm. Cependant, avec une augmentation de la densité de 1.63x entre le 10 et le 7nm, la recette utilisée est plus complexe que pour le passage 20/16nm (qui ne proposait qu'une augmentation de densité de 1.15x). Nos confrères de SemiWiki, très au fait des détails, ont confirmé il y a quelques jours que des changements sur les tailles minimales des cellules sont en grande partie à l'origine des gains de densité et que pour réduire les coûts, TSMC évitera au maximum de généraliser le quadruple patterning (SAQP). Le 10 et le 7nm auront donc bel et bien des similarités techniques.

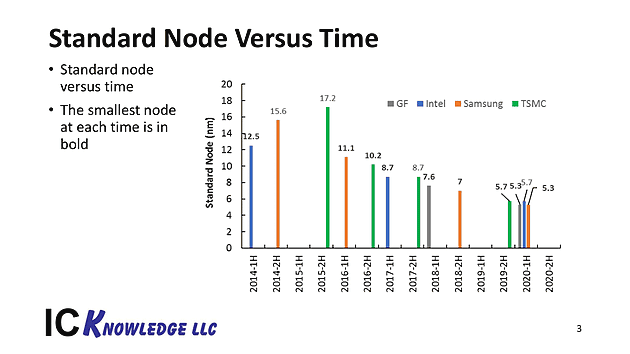

Pour essayer d'y voir un peu plus clair, et étant donné que plus aucun constructeur ne suit de règles équivalentes pour parler de densité, SemiWiki a publié ce graphique intéressant qui montre une "estimation" de la densité comparée de tous les fondeurs :

D'après SemiWiki, le 10nm d'Intel et le 7nm de TSMC auraient, après ajustement, une densité comparable. Il s'agit bien entendu d'estimations qui valent ce qu'elles valent, vous pouvez retrouver l'explication de la formule utilisée ici , mais elles donnent un bon ordre d'idée de ce à quoi il faut s'attendre (un seul bémol à cette analyse : les prévisions concernant GlobalFoundries nous semblent excessivement optimistes, en grande partie à cause des annonces de GlobalFoundries qui nous paraissent déconnectées de leur capacité d'exécution ces dernières années).

En pratique le 10nm de TSMC disposera tout de même d'une meilleure densité que l'actuel 14nm d'Intel, TSMC pourra donc se targuer d'avoir dépassé Intel côté process lorsque les premiers produits 10nm seront disponibles plus tard dans l'année. Et si Intel reprendra l'avantage avec "son" 10nm, TSMC sera effectivement - et pour la première fois - à parité dès la fin de l'année en lançant la production de son 7nm. Une situation qui durera un moment, et pour la première fois les constructeurs "fabless" pourront disposer d'un process équivalent en densité à celui d'Intel.

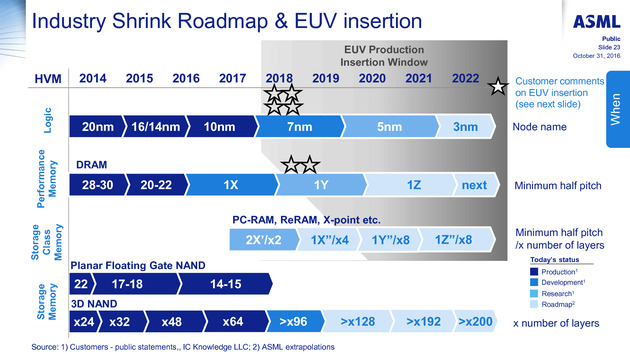

On notera enfin, concernant le 7nm, que TSMC a confirmé qu'ils inséreront l'EUV au bout d'un an de production à 7nm (soit fin 2018) pour créer une nouvelle version du 7nm (à l'image des multiples 16nm). Des propos plutôt optimistes concernant la lithographie EUV qui sera, Mark Liu le rappelle, indispensable à 5nm. Et un timing qui coïncide exactement avec le lancement de la production du 7nm de Samsung qui utilisera elle, dès le début, l'EUV !

ASML investit dans Carl Zeiss SMT pour l'EUV

ASML a annoncé hier qu'il comptait s'offrir un quart de Carl Zeiss SMT (24.9%) pour un montant de près de un milliard d'euros. Zeiss SMT est la filiale "Semiconductor Manufacturing Technology" du groupe allemand Zeiss spécialisé dans l'optique.

ASML indique dans son communiqué qu'il s'agit de renforcer la collaboration entre les deux sociétés, Zeiss SMT fournissant les systèmes optiques utilisés notamment dans les machines de lithographie EUV.

ASML investira en prime 220 millions d'euros dans le centre de recherche et développement de Zeiss SMT, et financera 540 millions d'investissements sur les 6 prochaines années.

L'enjeu de l'investissement, selon ASML, concerne les futures générations d'EUV avec la possibilité d'étendre la durée de vie de la technologie. Car si certains fabricants de semiconducteurs comme Samsung disent désormais (enfin !) qu'ils utiliseront l'EUV à 7nm, les très nombreux retards de la technologie font qu'elle court le risque de voir sa fenêtre d'utilisation réduite, au risque d'être remplacée par d'autres technologies.

Des systèmes optiques plus complexes avec une ouverture numérique de 0.5 (contre 0.33 pour les premières générations d'EUV) est ce que vise ASML dans cet investissement, qui ne devrait porter ses fruits que d'ici 2024. Il permettrait cependant d'étendre la durée de vie de l'EUV sous les 5nm et pour "plusieurs générations". On sait - en parallèle - qu'autour de 5nm, on atteindra les limites du silicium et l'utilisation d'autres matériaux deviendra nécessaire.

L'intérêt de la lithographie EUV est pour rappel de remplacer la source lumineuse utilisée actuellement par les scanners (elle est générée par des lasers à exciplexe Argon/Fluor avec une longueur d'onde de 193nm) par une source dont la longueur d'onde n'est que de 13.5nm, améliorant fortement les possibilités et réduisant le nombre d'étapes nécessaires pour arriver a fabriquer les puces en évitant la généralisation du multi-patterning.

ASML aurait réitéré à nos confrères d'EEtimes que quatre fabricants de puces, et deux fabricants de mémoires, se sont engagés à faire entrer l'EUV en production en 2018, quelque chose que la firme avait également indiqué dans une présentation aux investisseurs (qui évoquait 2018/2019). Une affirmation qui nous parait bien optimiste !

Aujourd'hui, seuls Samsung et GlobalFoundries se sont engagés publiquement à 7nm, pour des dates qui coïncident. En ce qui concerne TSMC, il faudra attendre le 5nm pour le voir arriver de manière extensive, sa production risque est prévue pour 2019 uniquement. Intel avait annoncé de son côté qu'il n'utiliserait pas l'EUV à 10nm, et qu'au mieux l'EUV était "une option" pour le 7nm. Le 7nm d'Intel utilisera une solution de lithographie a immersion classique. Et côté dates, 2019 semble extrêmement optimiste considérant l'exécution d'Intel ces dernières années (retards massifs sur le 14nm, introduction de Kaby Lake pour retarder le 10nm, lancement du 10nm repoussé à fin 2017 et uniquement sur des références mobiles, sans parler de l'introduction dans la roadmap de Coffee Lake en 2018... et en 14nm !).

En ce qui concerne les fabricants mémoire, Samsung avait évoqué la possibilité sans pour autant s'engager fermement. SK Hynix évoquait l'utilisation de l'EUV vers 2019.

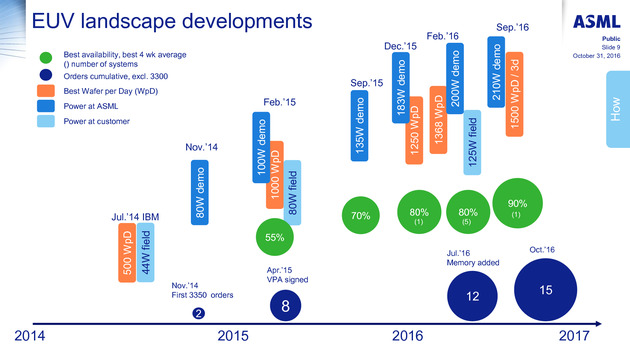

Les machines qui seront utilisées en production, les NXE:3400B, atteindraient d'après ASML un débit de 125 wafers/heure, un progrès notable par rapport à mars 2015 ou ASML se félicitait de 42 wafers/heure (entre 50 et 100 wafers/heure étaient considérés comme le minimum pour éventuellement utiliser la technologie d'après Mark Bohr d'Intel). Pour arriver à ce chiffre, ASML devra augmenter fortement la puissance de la source lumineuse. Le constructeur aurait livré des sources 125W à ses clients cette année qui ont permis d'atteindre 85 wafers/heure.

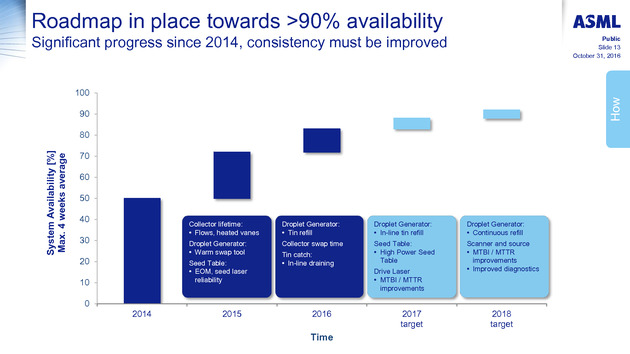

La question de la disponibilité des machines semble également être meilleure, de seulement 55% à l'époque, ASML atteint aujourd'hui entre 70 et 80%, avec l'objectif d'être a 90% en 2018.

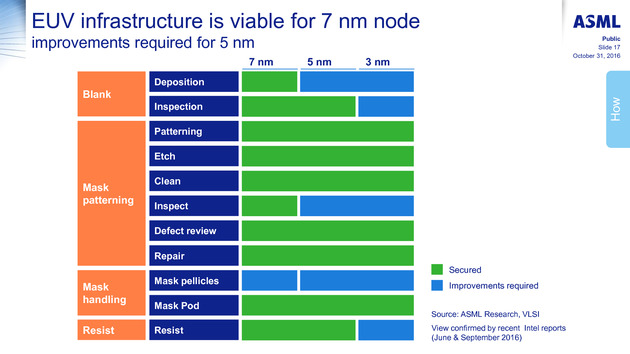

L'enthousiasme d'ASML - le seul à se lancer dans l'EUV - est forcément élevé pour sa technologie mais il faut une fois de plus rappeler que les scanners ne sont qu'une partie de la chaîne de fabrication. Les progrès réalisés, bien qu'importants, ne veulent pas dire que l'EUV est "prêt", loin de là.

La question des masques (la plaque transparente qui contient l'image de la puce à graver) et de l'inspection de leurs éventuels défauts n'a pas encore été résolue. Et si là aussi ASML tente d'apporter sa propre réponse, en pratique le problème reste complexe a solutionner avec des conséquences massives sur la viabilité de la technologie en production (plus de détails dans cet excellent article ).

Samsung annonce de futurs process 14 et 10nm

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Comme souvent, ces "variantes" de process sont des itérations autour d'une même technologie. Elles sont l'occasion d'annoncer des gains obtenus par l'optimisation de l'exploitation des process. Dans le cas de la version U, Samsung annonce des performances "plus élevées" à consommation égale, avec des règles de design identiques à son process 14LPC. Pour Samsung, le 14LPU est adapté aux utilisations "hautes performances" qui requièrent "beaucoup de calculs".

Un appel du pied à peine voilé aux fabricants de GPU et de SoC haut de gamme. Si Samsung a réussi a obtenir la fabrication de quelques GPU Nvidia (notamment les GP107 des GTX 1050), il s'agit de puces plus petites avec des niveaux de performances moindres par rapport au haut de gamme, qui reste toujours fabriqué chez TSMC. De la même manière, si AMD a fabriqué Polaris chez GlobalFoundries (sur un process techniquement identique à celui utilisé par Samsung, GlobalFoundries utilisant le process de Samsung sous licence), il ne s'agit pas non plus du haut de gamme (les raisons d'AMD étant beaucoup plus complexes).

La compétition avec TSMC est excessivement rude pour Samsung, qui tente avec cette quatrième version de s'attirer de nouveaux marchés. Le dernier "gros coup" du fondeur avait été la co-fabrication des SoC A9 d'Apple, un marché obtenu grâce au retard annoncé de TSMC. Un retard comblé en dernière minute par le fondeur Taiwanais. Les comparaisons directes sont toujours à double tranchant, et si Samsung avait bel et bien un avantage de densité sur son concurrent, sur le plan des performances TSMC restait, malgré la précipitation, en tête.

Cette version 14LPU tentera de combler ce déficit d'image même si selon toutes vraisemblances, TSMC gardera une main mise sur le haut de gamme sur ce node.

En parallèle, Samsung annonce également un 10LPU, qui sera cette fois la troisième version du 10nm de Samsung. Contrairement au 14LPU, le 10LPU augmentera la densité par rapport aux 10LPE/LPP, et Samsung le présente comme le 10nm proposant le cout le plus faible "de l'industrie". Le nom de 10LPC aurait probablement été plus adapté pour décrire ce process mais peu importe !

Dans les deux cas, il s'agit d'annonces puisque les kits de développement (PDK) pour le 14LPU et le 10LPU ne seront disponibles qu'au second trimestre 2017 ! On ne s'attendra donc pas a voir des produits les exploiter rapidement, le 10LPP entrera en production en volume pour rappel mi-2017.

On notera enfin que Samsung confirme une fois de plus sa volonté d'utiliser la lithographie EUV à 7nm, pour au moins une partie des couches de la puce. On rappellera que le 7nm de Samsung devrait arriver plus tard que le celui de son concurrent, la société ayant sous entendu à plusieurs reprises ces dernières semaines que le 10nm aurait une durée de vie plus longue qu'annoncée par certains.

TSMC tente en effet de lancer la production 7nm volume avec un an de décalage par rapport au 10nm (soit respectivement Q4 2016 pour le 10nm, et Q4 2017 pour le 7nm). Un rythme infernal qui ne sera suivi par personne d'autre (et largement financé, faut-il le rappeler, par Apple), mais sur lequel TSMC semble extrêmement confiant.

7nm fin 2018 pour GlobalFoundries ?

GlobalFoundries a publié un communiqué de presse annonçant officiellement son prochain process FinFet, qui sera en 7nm. On rapellera que le process 14 FinFET actuel de GlobalFoundries, le 14LPP, a été développé par Samsung suite aux problèmes de développement du 14XM (la version interne du 14nm de GlobalFoundries, abandonnée).

Comme nous vous l'avions indiqué, GlobalFoundries ne proposera pas de 10nm, son prochain process sera donc un 7nm, baptisé tout simplement 7nm FinFET. Comme souvent, le communiqué du fondeur est particulièrement flou, indiquant à la fois que ce 7nm FinFET profitera des "années d'expérience d'IBM", tout en se "construisant sur le succès du 14LPP".

Le fondeur donne deux chiffres, tout d'abord une densité double par rapport "aux process 16/14", et un gain de performances de 30%. On notera avec circonspection que chez TSMC par exemple, le 10nm est annoncé comme 2.1x plus dense que son 16nm, et que son 7nm sera 1.63x plus dense que son 10nm. Autant dire que le 2x annoncé par GlobalFoundries ne semble pas vraiment au niveau d'un "7nm".

Techniquement le fondeur confirme qu'il s'agira d'un process FinFET optique, avec éventuellement la possibilité d'utiliser de l'EUV si disponible sur quelques couches.

Côté délais, GlobalFoundries annonce une production "risque" début 2018. A titre de comparaison, le 7nm de TSMC est annoncé en production risque début 2017, avec une production volume démarrant en Q1 2018.

Sur le papier donc, ce communiqué de presse de GlobalFoundries est tout simplement inquiétant, dévoilant un 7nm dont les caractéristiques techniques semblent assez lointaines de ce que proposera un TSMC ou un Samsung. Et qui sera disponible qui plus est avec un retard d'au moins 6 mois, et possiblement plus, par rapport au planning - certes incroyablement agressif - de TSMC.

Si la CEO d'AMD, Lisa Su, se satisfait dans le communiqué des développements "à long terme" de GlobalFoundries, cette annonce assez peu flatteuse du fondeur explique probablement pourquoi il a accepté de lâcher du lest auprès d'AMD. Nous vous en parlions en détail en début de mois, AMD et GlobalFoundries ont renégocié leur Wafer Supply Agreement avec pour résultat la levée de multiples clauses d'exclusivités qui liaient les deux sociétés.

12nm FD-SOI pour GlobalFoundries

GlobalFoundries vient de publier un communiqué de presse indiquant l'arrivée d'un nouveau process FD-SOI sur sa roadmap, le 12FDX. Il s'agira d'une troisième version de FD-SOI proposée par le fondeur, après un 28nm offert en partenariat avec STMicroElectronics, et un 22nm fabriqué dans l'usine de Dresde.

Ce 12nm FD-SOI sera lui aussi fabriqué dans l'usine de Dresde et visera principalement les applications mobiles et les usages basse consommation, à l'image du positionnement du 22FDX. Il sera également possible de l'utiliser pour des puces radio (RF).

GlobalFoundries décrit ce process comme équivalent à un 10 FinFET côté performances, avec une meilleure consommation et un cout inférieur au 16 FinFET actuel. La société estime qu'il proposera 15% de performances en plus et 50% de consommation en moins que les process FinFET 14/16 actuels.

Si l'on pourrait croire que ce 12FDX viendra combler le creux dans la roadmap FinFET de GlobalFoundries, qui passera pour rappel d'un 14nm sous licence Samsung directement à un 7nm développé en interne, en pratique il n'en sera rien. A l'image du 22FDX qui n'a été lancé que l'année dernière, le communiqué évoque 2019 pour les premiers tape-out (soit encore plus loin pour les volumes commerciaux).

A titre de comparaison, TSMC, Samsung et Intel devraient produire en volume le 10 FinFET l'année prochaine.