Les derniers contenus liés aux tags AMD et 7nm

10/7nm en avance pour TSMC, EUV pour le 5nm

7nm fin 2018 pour GlobalFoundries ?

Nouvel accord WSA entre AMD/GlobalFoundries

AMD Vega 7nm en labo, Zen 2 échantillonné en 2018

AMD utilisera le 12nm de GloFo en 2018

Epyc, ThreadRipper, AMD détaille sa roadmap CPU

Des détails sur le 7nm à l'ISSCC 2017

Samsung annonce de futurs process 14 et 10nm

AMD Vega 7nm en labo, Zen 2 échantillonné en 2018

Déjà évoqué par AMD lors du CES par exemple, la version 7nm de Vega tourne actuellement sous forme de prototype dans les laboratoires d'AMD. C'est Lisa Su, CEO d'AMD, qui vient de l'indiquer lors de l'annonce des résultats.

Il ne s'agit pas d'une avance sur le planning, le constructeur se limitant à évoquer un échantillonnage en version "Instinct" (gamme destinée aux calculs type AI) "plus tard dans l'année", sans parler de production en volume et encore moins de version Radeon. AMD précise au passage que c'est TSMC qui grave ce GPU.

Concernant Zen 2 en 7nm, AMD précise que les déclinaisons serveurs devraient également être échantillonnées cette année, pour une arrivée qui reste prévue en 2019, sans plus de précision, côté desktop également.

AMD utilisera le 12nm de GloFo en 2018

GlobalFoundries vient d'annoncer par un communiqué de presse le lancement à venir d'un nouveau process, baptisé 12LP.

Il s'agit d'une variante de l'actuel 14LPP FinFET du constructeur qui permettra d'améliorer la densité de 15% et d'augmenter les performances de 10%. Il s'agit bien entendu de la réponse de GlobalFoundries au "12nm" de TSMC et au tout frais "11LPP" de Samsung.

La société ne donne pas de date ferme sur la disponibilité, mais le communiqué inclut une citation de Mark Papermaster, CTO d'AMD qui déclare qu'AMD "introduira de nouveaux produits clients et graphiques basés sur le 12nm de GlobalFoundries en 2018".

Les roadmaps d'AMD mentionnaient en effet une version de Zen en "14nm+" avant Zen 2 prévu en 7nm. Côté graphique, les roadmaps d'AMD incluaient aussi une version 14nm+ de Vega (avant Navi en 7nm). Dans tous les cas, AMD dispose désormais de l'option d'utiliser d'autres fondeurs s'il le souhaite pour certains produits, même si la société ne semble pas l'avoir utilisée jusque maintenant.

Pour rappel, le 7nm de GlobalFoundries, assez ambitieux, est prévu au mieux pour fin 2018.

Epyc, ThreadRipper, AMD détaille sa roadmap CPU

AMD tenait ce soir son "Financial Analyst Day", l'occasion de quelques annonces pour le constructeur.

La première concerne le nom commercial de Naples, la déclinaison serveur de Zen. AMD ne réutilisera pas la marque Opteron, la société opposera donc aux Xeon d'Intel des... Epyc. AMD semble avoir prix goût à la stylisation de ses marques à coup de Y ! Certains y verront par contre une référence - probablement non voulue - à l'Itanium d'Intel ...

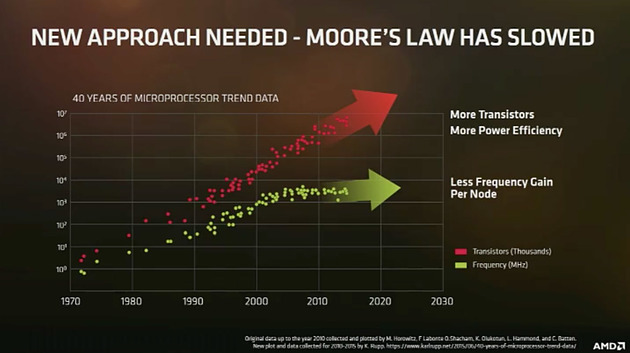

AMD est revenu également sur le ralentissement de la loi de Moore, ou plus exactement le ralentissement des gains apportés par chaque nouveau node. La situation n'est pas nouvelle, ni liée à AMD et ses partenaires fondeurs (Intel a également livré une vision plutôt pessimiste de son 10nm !). AMD reconnaît que les gains de densité et de performances apportés par les nodes vont se réduire, en plus des plafonds de fréquences qui eux ne sont pas nouveaux.

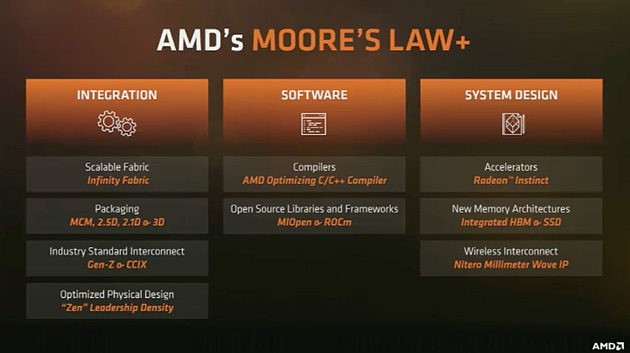

Pour compenser cela AMD met en avant ses initiatives, insistant par exemple son data fabric pour relier des blocs (sur un même die, comme pour Ryzen) ou des dies entre eux (sous le nom Infinity Fabric). Nous admettrons avoir toussé devant le slide ou il était écrit "low latency". Pour le reste AMD mise sur le logiciel, comme sur un nouveau compilateur "optimisé" pour Zen. Baptisé AMD Optimizing C/C++ Compiler (AOCC pour faire court), il s'agit en pratique d'une version "optimisée" de Clang/LLVM 4.0 disponible pour Linux et visant plus spécifiquement la plateforme serveur. Nous n'avons pour le moment pas plus de détails sur les changements effectués par AMD, ni à savoir si ces modifications seront portées dans LLVM (ce qui serait probablement plus utile). La version 1.0 est disponible sur cette page .

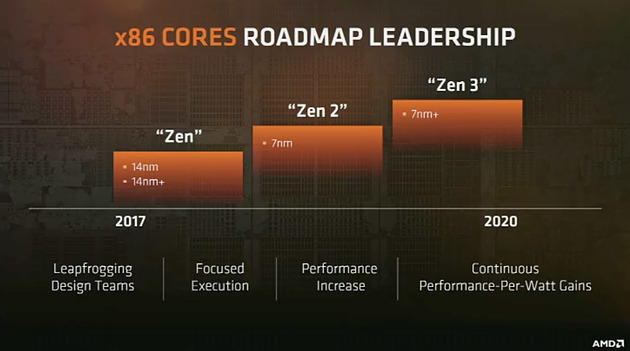

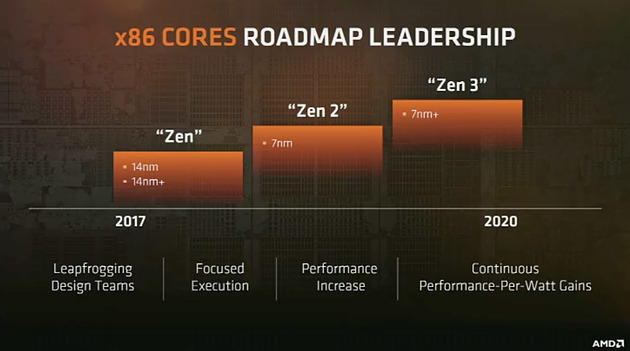

En ce qui concerne la roadmap, AMD ne s'est pas trop avancé avec ce slide assez flou au niveau des dates. On note qu'une version "14nm+" de Zen est prévue ce qui est assez curieux. Officiellement GlobalFoundries propose son 14LPP (Low Power Plus) et bien qu'AMD ne l'ait pas confirmé, on pouvait penser que c'est cette version (et non le 14LPE, E pour Early) qui était utilisée pour Zen étant donné qu'elle l'était déjà pour Polaris. Difficile donc de savoir ce qu'AMD entend par "14+", on pense à une version optimisée du 14LPP à venir (une sorte d'équivalent du 14LPC chez Samsung, même si les deux sociétés ont depuis divergé sur leurs process).

L'autre point à noter est l'absence de 10nm. Là encore ce n'est pas une totale surprise, Global Foundries ne proposera pas de 10nm et si TSMC en proposera un, il sera réservé aux clients gros volume (Apple en particulier). Si AMD reste chez Global Foundries pour Zen2, il faudra attendre fin 2018 si la société tient ses délais. AMD s'est cependant ouvert la possibilité de produire des CPU chez d'autres fondeurs en renégociant le wafer supply agreement qui les lie à Global Foundries. Malheureusement aucune information supplémentaire n'a été donnée sur les timings ou les changements à venir.

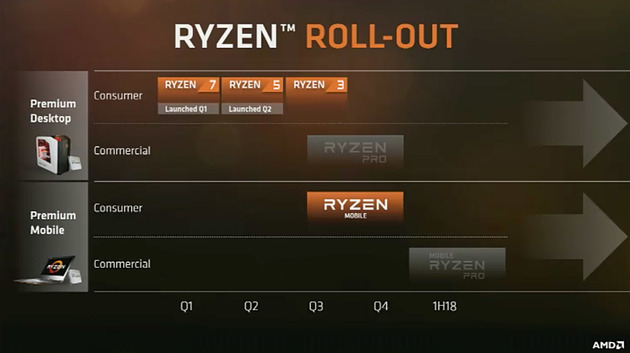

On passera très rapidement sur l'arrivée des versions "Pro" de Ryzen, qui seront simplement des versions destinées à l'entreprise (avec on l'imagine des fonctionnalités manageability comme celles d'Intel) et sur lesquelles aucun détail n'a été donné.

Le constructeur confirme par contre l'arrivée des versions mobiles pour le troisième trimestre. AMD confirme qu'il s'agira bien d'APU basées à la fois sur Zen côté CPU, et sur Vega pour le GPU. Sur le papier l'architecture Zen devrait pouvoir être très compétitive sur ce segment et il sera intéressant de voir si AMD est capable de proposer des produits qui séduiront les OEM.

AMD a enfin confirmé l'existence de Threadripper dont nous vous parlions il y a peu. A l'image d'Intel, AMD utilisera ses puces serveurs pour créer des plateformes desktop haut de gamme. Sur le serveur, AMD proposera avec Naples des puces qui relient quatre dies Zeppelin (le die utilisé pour Ryzen) pour proposer jusqu'a 32 coeurs. Des versions double Zeppelin sont également au programme et c'est celles-ci qui seront utilisées pour la plateforme desktop haut de gamme d'AMD que l'on connaissait sous le nom de code Threadripper. AMD a confirmé le nom de code mais n'en aura pas dit plus. Ces puces utiliseront le monstrueux socket SP3r2 (4094 contacts !). Le lancement interviendra cet été selon AMD et le nom commercial utilisera la marque Ryzen (et non Epyc).

En bref

Cette conférence aux investisseurs, pour la partie CPU, n'a pas été très riche en surprises. AMD est concentré sur le lancement des versions mobiles de Ryzen et est beaucoup moins prolixe sur les évolutions à venir qu'il a pu l'être ces dernières années où communiquer était essentiel pour faire oublier la dette technique accumulée par les FX. On restera curieux d'une éventuelle version de "Zen 1" dans un process 14nm optimisé (que ce soit sous la forme de nouveaux SKU, ou plus simplement pour les APU), même si les gros changements n'interviendront pas avant le 7nm qui, chez Global Foundries, n'est prévu que fin 2018.

La confirmation de ThreadRipper reste une annonce qui embarrassera, au moins sur le papier, son concurrent qui ne pourra plus se vanter du titre - certes un peu futile - du plus grand nombre de coeurs dans un CPU desktop. On retiendra au final surtout la confirmation de l'utilisation de l'architecture graphique Vega sur les APU qui pourrait permettre à AMD, pour le coup, de proposer des produits réellement embarrassants pour son concurrent dont les iGP restent assez modestes, particulièrement depuis qu'Intel semble abandonner ses versions les plus haut de gamme, les GT4e.

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

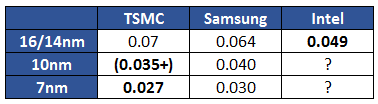

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

Samsung annonce de futurs process 14 et 10nm

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Samsung vient d'indiquer par un communiqué de presse qu'il proposera une quatrième version de son process 14nm. Baptisée 14PLU, elle fait suite au 14LPE (Low Power Early, la première version dispo lorsque les yields étaient faibles), 14LPP (Low Power Plus, version un peu plus optimisée lorsque les yields étaient stabilisés), 14LPC (possiblement Low Power Compact, la version réduit les couts et fait écho au 16FFC de TSMC, tout en ajoutant la possibilité de pouvoir fabriquer des radios, indispensable pour la fabrication de modems par exemple).

Comme souvent, ces "variantes" de process sont des itérations autour d'une même technologie. Elles sont l'occasion d'annoncer des gains obtenus par l'optimisation de l'exploitation des process. Dans le cas de la version U, Samsung annonce des performances "plus élevées" à consommation égale, avec des règles de design identiques à son process 14LPC. Pour Samsung, le 14LPU est adapté aux utilisations "hautes performances" qui requièrent "beaucoup de calculs".

Un appel du pied à peine voilé aux fabricants de GPU et de SoC haut de gamme. Si Samsung a réussi a obtenir la fabrication de quelques GPU Nvidia (notamment les GP107 des GTX 1050), il s'agit de puces plus petites avec des niveaux de performances moindres par rapport au haut de gamme, qui reste toujours fabriqué chez TSMC. De la même manière, si AMD a fabriqué Polaris chez GlobalFoundries (sur un process techniquement identique à celui utilisé par Samsung, GlobalFoundries utilisant le process de Samsung sous licence), il ne s'agit pas non plus du haut de gamme (les raisons d'AMD étant beaucoup plus complexes).

La compétition avec TSMC est excessivement rude pour Samsung, qui tente avec cette quatrième version de s'attirer de nouveaux marchés. Le dernier "gros coup" du fondeur avait été la co-fabrication des SoC A9 d'Apple, un marché obtenu grâce au retard annoncé de TSMC. Un retard comblé en dernière minute par le fondeur Taiwanais. Les comparaisons directes sont toujours à double tranchant, et si Samsung avait bel et bien un avantage de densité sur son concurrent, sur le plan des performances TSMC restait, malgré la précipitation, en tête.

Cette version 14LPU tentera de combler ce déficit d'image même si selon toutes vraisemblances, TSMC gardera une main mise sur le haut de gamme sur ce node.

En parallèle, Samsung annonce également un 10LPU, qui sera cette fois la troisième version du 10nm de Samsung. Contrairement au 14LPU, le 10LPU augmentera la densité par rapport aux 10LPE/LPP, et Samsung le présente comme le 10nm proposant le cout le plus faible "de l'industrie". Le nom de 10LPC aurait probablement été plus adapté pour décrire ce process mais peu importe !

Dans les deux cas, il s'agit d'annonces puisque les kits de développement (PDK) pour le 14LPU et le 10LPU ne seront disponibles qu'au second trimestre 2017 ! On ne s'attendra donc pas a voir des produits les exploiter rapidement, le 10LPP entrera en production en volume pour rappel mi-2017.

On notera enfin que Samsung confirme une fois de plus sa volonté d'utiliser la lithographie EUV à 7nm, pour au moins une partie des couches de la puce. On rappellera que le 7nm de Samsung devrait arriver plus tard que le celui de son concurrent, la société ayant sous entendu à plusieurs reprises ces dernières semaines que le 10nm aurait une durée de vie plus longue qu'annoncée par certains.

TSMC tente en effet de lancer la production 7nm volume avec un an de décalage par rapport au 10nm (soit respectivement Q4 2016 pour le 10nm, et Q4 2017 pour le 7nm). Un rythme infernal qui ne sera suivi par personne d'autre (et largement financé, faut-il le rappeler, par Apple), mais sur lequel TSMC semble extrêmement confiant.