Les derniers contenus liés aux tags Micron et TLC

Des détails sur le 7nm à l'ISSCC 2017

V-NAND Gen4 et Z-NAND pour Samsung

Seagate montre un SSD de 60 To !

16 Go en TLC 20nm chez Micron : 146mm²

MLC 3BPC en 25nm chez IMFT

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

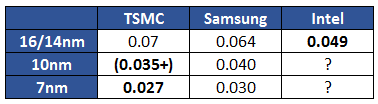

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

V-NAND Gen4 et Z-NAND pour Samsung

Samsung est lui aussi bien évidemment présent au Flash Memory Summit et en profite pour annoncer sa quatrième génération de mémoire NAND 3D (connue sous le nom marketing V-NAND). L'année dernière, Samsung annonçait sa troisième génération qui faisait passer à 48 couches pour obtenir jusque 32 Go par die.

Cette année, Samsung annonce 64 couches pour une densité maximale de 512 Gbit en TLC, soit 64 Go par die. De quoi permettre d'atteindre pas moins de 1 To par package (en superposant 16 dies). Samsung proposera donc un SSD BGA de 1 To avec 1500 Mo/s en lecture et 900 Mo/s en écriture.

Le PM1643 de 32 To, photo The SSD Review

Le SSD PM1633a de 16 To (qui avait été annoncé lors du Flash Memory Summit 2015 il y a un an, mais seulement commercialisé ces dernières semaines sera remplacé à terme par un modèle 32 To, le PM1643.

Une version 32 To en NVMe est également annoncée sous la référence PM1735 et un modèle M.2 de 4 To est également au programme en taille standard, et Samsung compte proposer en 2017 un "nouveau" format de M.2 dédié aux serveurs, le M.2 32114 (32mm de large pour 114 de long) avec une capacité pouvant atteindre 8 To, ce qui permettra d'atteindre 256 To de stockage dans un rack 1U.

Bien évidemment, et le lancement ces derniers jours du PM1633a le prouve, les annonces de Samsung se traduiront au fur et a mesure dans les mois à venir, le communiqué de presse du constructeur évoque le quatrième trimestre pour les premières disponibilités de produits basés sur la V-NAND de quatrième génération. Le PM1643 est quand à lui annoncé pour 2017 sans plus de précision.

On notera enfin une dernière annonce très floue de la part de Samsung avec la Z-NAND, un "nouveau type de mémoire" qui partage "la même structure fondamentale que la V-NAND" en utilisant un "design de circuit et un contrôleur unique". Si cela ne nous dit pas grand chose sur la manière dont fonctionne la technologie, il faut y voir la réponse de Samsung à la PRAM 3D XPoint d'Intel/Micron, le constructeur ne s'en cache en reprenant les mêmes arguments, une mémoire qui vient s'intercaler entre la DRAM (volatile, très rapide) et la NAND (non volatile, moins rapide).

La Z-NAND aurait une latence similaire à la PRAM, des performances séquentielles 20% supérieures, et une efficacité énergétique significativement meilleure. Bien entendu ces chiffres sont assez creux sachant que Samsung ne précise pas à quelle PRAM il se compare, mais on voit bien qu'Intel et Micron sont visés par cette annonce. Plus de détails devraient être disponibles d'ici quelques mois, Samsung annonçant une disponibilité en 2017.

Seagate montre un SSD de 60 To !

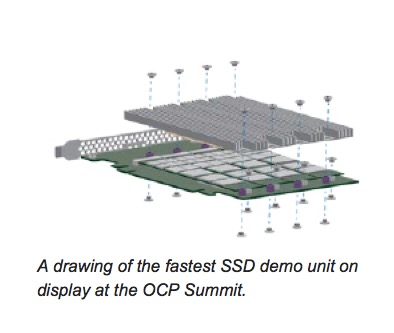

Le Flash Memory Summit est l'occasion de voir les différents acteurs du marché présenter leurs dernières innovations, mais aussi leurs nouveaux produits. Chez Seagate on a d'abord le droit à un SSD PCIe 10 Go/s, quelque chose qui avait été montré un peu plus tôt cette année lors de l'OCP Summit.

Le produit à désormais un nom, le Nytro XP7200 NVMe SSD et il s'agit comme nous le devinions a l'époque de l'assemblage de quatre SSD Nytro XM1440 M.2. Si l'on en croit nos confrères d'Anandtech cependant, il y a une subtilité : la carte n'inclut pas de switch PCIe pour muxer les lignes, Seagate exploiterait les 16 lignes PCIe comme quatre groupes x4 indépendants. En clair, le système (pour peu que le BIOS le supporte correctement) verra quatre disques indépendants sur lesquels il faudra ajouter un RAID logiciel côté système d'exploitation.

Pour ce qui est des performances, Seagate annonce 10 Go/s en lecture et 3.6 Go/s en écriture séquentielle, et respectivement 940k et 160k IOPS en lecture/écriture aléatoires pour une consommation de 26 watts en charge. Des modèles 4 To et 8 To sont au programme et la disponibilité est attendue au quatrième trimestre.

L'autre "gros morceau" de Seagate est un SSD SAS double port d'une capacité de 60 To. Le disque est au format 3.5 pouces et il utilise de la 3D NAND TLC en provenance de chez Micron. Des ponts ONFI sont utilisés pour multiplexer les canaux vers le contrôleur, ce qui aura bien évidemment un impact sur les performances en fonction des données auxquelles on accède.

Les spécifications finales et le prix seront connus un peu plus tard, ce SSD restant une démonstration technologique. Seagate annonce cependant qu'il lancera une version de ce SSD 60 To courant 2017.

16 Go en TLC 20nm chez Micron : 146mm²

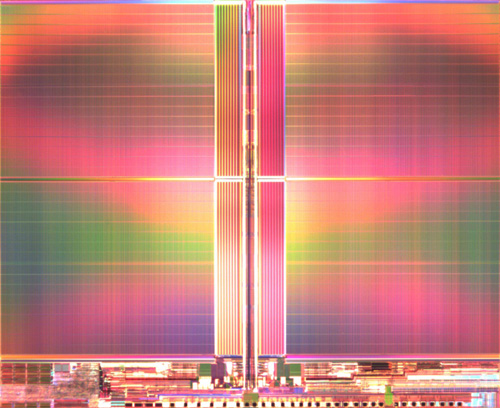

Micron avait déjà annoncé une puce de NAND de 16 Go gravée en 20nm, c'était en décembre 2011, et cette mémoire utilisait la technologie MLC (2 bits par cellule). Aujourd'hui le fondeur annonce une puce de 16 Go (128 Gb) qui utilise la TLC (3 bits par cellule). Elle ne mesure que 146mm², soit une baisse de la surface supérieure à 25% par rapport à la même puce en 20nm MLC.

A titre de comparaison une puce 8 Go en MLC et 25nm est à 167mm², la densité augmente donc par un facteur de 2,29 ce qui devrait permettre de faire sensiblement baisser le coût au Go. Actuellement en cours d'échantillonnage, cette puce sera produite en volume à compter du second trimestre.

Il faut noter qu'elle combine deux désavantages en terme de performances et de longévité : d'une part, du fait de la technologie TLC par rapport au MLC, Micron ne communiquant d'ailleurs pas sur son endurance, d'autre part parce que les puces de 16 Go utilisent des pages de 16 Ko, contre 8 et 4 Ko pour les puces de 8 et 4 Go. Pour rappel une page est la plus petite unité lisible et programmable d'une puce Flash.

Pour le moment il n'est pas question d'une utilisation dans les SSD, Micron la destinant au stockage amovible (cartes mémoires et clés USB), un marché qui devrait tout de même monopoliser 35% de la Flash en 2013.

MLC 3BPC en 25nm chez IMFT

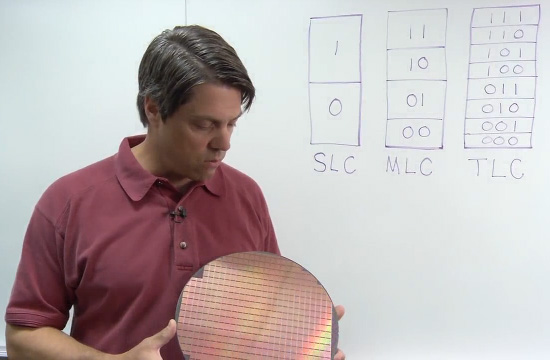

Après avoir annoncé une première puce Flash NAND MLC capable de stocker 3 bits par cellule (MLC 3BPC) en octobre 2009, la joint-venture Intel / Micron, IMFT (IM Flash Technologies), revient à la charge avec une nouvelle puce de ce type. La finesse de gravure passe de 34nm à 25nm, et la capacité de 4 à 8 Go.

Ce type de mémoire, également appelé TLC pour triple-level cell, permet de réduire notablement la taille du die pour une capacité identique, puisqu'elle ne mesure que 131mm², contre 167mm² pour une puce en 2 bits par cellule. A titre de comparaison, la puce TLC de 4 Go en 34nm mesurait 126mm².

Cette puce est actuellement en cours d'échantillonnage, alors que la MLC 25nm classique échantillonnée dès février est en production depuis mai. Elle devrait entrer en production d'ici à la fin de l'année. Il faut préciser que pour le moment, ce type de mémoire reste réservé aux clefs USB, aux lecteurs MP3 et aux cartes mémoires.

En effet, comme le passage de SLC (1 bit par cellule) à la MLC (2 bits par cellule), le passage de la MLC à la TLC (3 bits par cellule) abaisse les performances en écriture ainsi que l'endurance des cellules. Si aucun chiffre n'a été publié pour cette puce, Micron parlait début 2009 de performances divisées par 2 et d'endurance divisée par 10 ... voilà qui interdit donc leur utilisation au sein de SSD, à moins que la recette miracle d'Anobit fonctionne en pratique !