MLC 3 bits / cellule pour Micron/Intel

![]() La joint-venture d'Intel et Micron dans le domaine de la Flash, IM Flash Technologies (IMFT), vient d'annoncer avoir échantillonné une nouvelle puce de mémoire de 4 Go de Flash NAND MLC stockant 3 bits par cellule (MLC 3BPC). Il s'agit de la première MLC 3 bit par cellule d'IMFT, ce qui lui permet combiné à une gravure en 34nm d'afficher une taille de seulement 126mm². Cette puce est actuellement en cours d'échantillonnage et devrait être produite en volume au 4ème trimestre.

La joint-venture d'Intel et Micron dans le domaine de la Flash, IM Flash Technologies (IMFT), vient d'annoncer avoir échantillonné une nouvelle puce de mémoire de 4 Go de Flash NAND MLC stockant 3 bits par cellule (MLC 3BPC). Il s'agit de la première MLC 3 bit par cellule d'IMFT, ce qui lui permet combiné à une gravure en 34nm d'afficher une taille de seulement 126mm². Cette puce est actuellement en cours d'échantillonnage et devrait être produite en volume au 4ème trimestre.

Si Samsung et Hynix travaille également sur ce type de Flash NAND MLC, seule l'alliance Sandisk et Toshiba avait annoncée de telles puces : une première fois l'an passée sur un process en 56nm, puis une nouvelle fois en février dernier. Il s'agissait alors d'une puce 4 Go fabriquée en 32nm affichant une taille de 113mm², soit moins qu'une puce de 2 Go en MLC classique (2 bits par cellule) gravée en 43nm. Sa production devrait débuter au cours de ce second semestre.

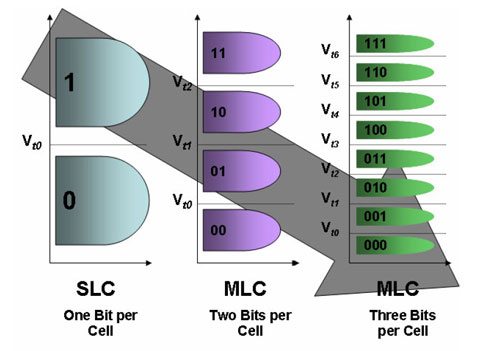

Pour rappel, la mémoire Flash SLC ne gère qu'un bit par cellule, contre 2 pour ma MLC classique utilisée jusqu'alors dans les SSD. En SLC, on doit pouvoir gérer 2 niveaux de tension distincts au sein de la cellule, 4 en MLC 2 bits, et 8 en MLC 3 bits. Cela a un impact négatif sur la vitesse d'écriture mais aussi sur l'endurance de ces dernières : une puce SLC est ainsi 10 fois plus endurante et 3 fois plus rapide qu'une MLC 2 bits. Le passage en 3 bits a un impact négatif sur ces deux facteurs, sans que les constructeurs communiquent exactement sur l'ampleur de cet impact.

Il est toutefois suffisant pour que Micron indique que sa nouvelle mémoire est destinée aux clés USB et aux cartes mémoires, mais pas pour les SSD. A ce propos, il y'a 6 mois un billet au sujet de ce type de MLC avait été posté sur le Blog officiel de Micron . L'auteur indiquait alors que Micron développait une telle puce mais que pour le moment la technologie n'était pas vraiment satisfaisante, avec des performances en écriture divisées par 2 en écriture et une endurance 10 fois moindre, ce qui la porterait à 1 000 cycles d'écritures ! De fait, l'auteur concluait que pour le moment le meilleur moyen d'abaisser les coûts tout en conservant un bon niveau de performance et de fiabilité était de réduire la finesse de gravure sur les actuels MLC/SLC ... malheureusement et Micron l'admet d'ailleurs dans une vidéo postée sur ce même blog, cela va devenir de plus en plus difficile d'abaisser la finesse de gravure. Ainsi, si le rythme se ralenti, le seul moyen d'augmenter la densité sera alors de passer à la MLC 3BPC, puis à la MLC 4BPC mise au point par Sandisk / Toshiba ...

Contenus relatifs

- [+] 15/06: La V-NAND Gen4 de Samsung produite ...

- [+] 17/01: Nouveau contrôleur SSD SATA chez Ma...

- [+] 10/01: Le Plextor M8Se (NVMe TLC) arrive e...

- [+] 09/01: Le contrôleur Phison PS5008-E8 arri...

- [+] 15/11: Des détails sur le 7nm à l'ISSCC 20...

- [+] 07/11: Deuxième génération de NAND 3D Inte...

- [+] 27/10: Intel P3100, SSD M.2 pour serveurs

- [+] 11/10: Western Digital lance ses SSD WD Bl...

- [+] 28/09: OCZ TL100 par Toshiba pour l'entrée...

- [+] 21/09: Samsung 960 Pro et Evo au format M....