Les derniers contenus liés aux tags Western Digital et 3D NAND

NAND 3D 32 Go TLC 64 couches chez Toshiba / Western

Nouvelle usine NAND 3D Toshiba / Western

3D NAND 96 couches chez Toshiba et Western

Toshiba et WD bientôt au point sur la NAND 3D

La NAND 3D 64 couches arrive aussi chez WD

Des détails sur le 7nm à l'ISSCC 2017

Nouvelle usine NAND 3D pour Toshiba

3D NAND 96 couches chez Toshiba et Western

Même si ils sont en conflit ouvert côté juridique, Western Digital et Toshiba continuent de travailler en pratique au sein de leur joint-venture sur la NAND et viennent d'annoncer qu'ils avaient fini de développer avec succès leur nouvelle génération de NAND 3D 96 couches. L'échantillonnage aux clients doit commencer au cours de ce semestre, la production en volume étant prévue pour 2018. Dans un premier temps c'est une puce 32 Go qui sera produite, avant de passer à des capacités supérieures pouvant atteindre 128 Go. Des versions TLC comme QLC sont à l'ordre du jour.

Toshiba et Western Digital annoncent à cette occasion que la montée en puissance de leur 3è génération de NAND 3D 64 couches continue, confirmant l'objectif qui est que 75% de la production utilise cette technologie cette année. Les deux associés estiment même que leur joint-venture sera l'entité qui produira le plus de NAND 3D 64 couches cette année, devant Samsung ou IMFT (Intel / Micron).

Toshiba et WD bientôt au point sur la NAND 3D

En février dernier, Western Digital et Toshiba annonçaient la production d'échantillon de puces 64 Go de NAND 3D 64 couches TLC, en attendant le lancement de la production en volume au cours du second trimestre. Cette nouvelle NAND 3D devait être la bonne, puisqu'au contraire de Samsung et plus récemment Micron leur NAND 3D n'avait pas été vraiment intégrée en volume dans des produits tels que des SSD, Western qualifiant même la seconde génération 48 couches de learning platform.

Alors que les deux constructeurs se livrent bataille quant à l'avenir de leur joint-venture dédiée à la Flash, le sujet avance. Il y a une quinzaine de jours, Toshiba a en effet fait la démonstration d'un prototype de SSD NVMe de 1 To basé sur cette mémoire. De son côté HGST, filiale de Western Digital, vient d'annoncer l'Ultrastar SS3300 utilisant cette mémoire en version MLC 48 Go ou TLC 64 Go. En MLC les SSD supportent selon la gamme 3 ou 10 écritures complètes par jour pendant 5 ans, contre 0.5 ou 1 côté TLC.

WD a précisé lors de ses résultats financiers qu'il lui était déjà moins couteux de produire une puce 64 Go de NAND 3D 64 couches TLC que la capacité équivalente en NAND 2D en 15nm, et qu'il prévoyait de produire 75% de sa NAND 3D cette année en version 64 couches.

La NAND 3D 64 couches arrive aussi chez WD

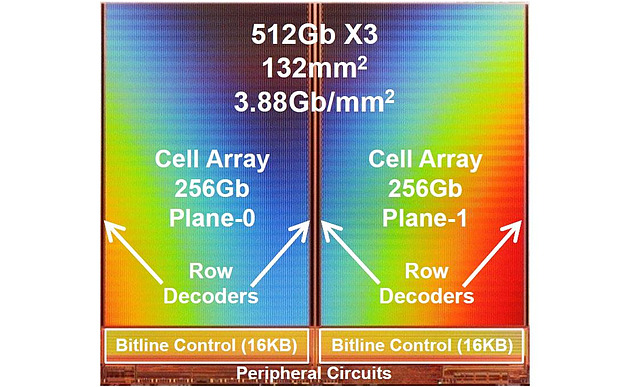

En juillet dernier, Western Digital évoquait l'arrivée d'un die de 512 Gb de NAND 3D 64 couches en TLC. Le constructeur confirme ses dires, puisque la production d'échantillons a débuté.

Western Digital et Toshiba, via la joint-venture Flash Forward, sont donc les premiers à mettre en production un tel die, alors même que la concurrence s'active en la matière : Micron a tout récemment annoncé prendre la même direction, tout comme Samsung.

C'est toujours la structure de type BiCS (Bit Cost Scalable) qui est de mise, et après les 48 couches en 2015, Western Digital/Toshiba était parvenu à une première réussite en 64 couches sur un die de 256 Gb en juillet dernier.

Le constructeur a décidé de passer directement à une densité de données plus importante encore avec ce die de 512 Gb, qui devrait passer en production de masse au cours du second semestre de cette année dans l'usine de Yokkaichi au Japon, usine qu'elle partage avec Toshiba.

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

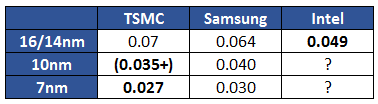

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

Nouvelle usine NAND 3D pour Toshiba

Après avoir inauguré en juillet dernier sa nouvelle usine de mémoire flash au Japon, Toshiba vient d'annoncer qu'il s'engage à en construire une nouvelle.

Elle se situera toujours sur le même site japonais de Yokkaichi situé dans la ville de Mie, et sera dédiée à la production de la 3D NAND BiCS de Toshiba.

Le début de la construction est prévu pour 2017 et la société s'attend à ce que la première "phase" (l'usine sera construite en deux temps) soit opérationnelle à l'été 2018. Toshiba construira également un nouveau building dédié spécifiquement au R&D, où il centralisera des équipes qui étaient jusque là éparpillées.

L'annonce est faite par Toshiba qui n'est pas très clair sur le rôle que jouera Western Digital dans le financement. On rappellera que Toshiba et Sandisk collaboraient au sein d'une Joint Venture (Flash Forward). Le rachat de Sandisk par Western Digital avait lié les deux entreprises qui sont en compétition sur le marché des disques durs.

Le communiqué précise simplement que selon leurs "discussions" avec Western Digital, ils s'attendent à ce que ce dernier continue à participer aux investissements et aux opérations de cette usine. L'absence de communiqué commun chez WD laisse penser que les relations sont possiblement tendues entre les deux sociétés.