16-FinFET plus et 10nm chez TSMC

Lors de sa conférence concernant ses résultats financiers, TSMC a donné quelques détails sur ses process de fabrication courants et à venir.

Pour le 20nm tout d'abord, TSMC a confirmé que la production du 20-SoC a bel et bien commencé en janvier. La société a cependant indiqué que le ramp up du process aura été le plus rapide de son histoire sous entendant des yields un peu en avance sur les prévisions, sans plus de détails. La question du coût des wafers est toujours un point important pour les clients du fabricant, le 20nm engendrant une augmentation assez importante de par l'usage du double patterning. Les estimations du cout des wafers chez TSMC parlent d'environ 2200-2600$ pour le 28nm, le 20nm ajoutant un surcout de plus de 20% par wafer (sans prendre en compte les différences de yields qui augmentent significativement la différence sur le cout final par puce fonctionnelle). Pour l'instant, le 20nm n'entre pas encore dans les revenus financiers de TSMC mais devrait entrer pour une petite partie au prochain trimestre.

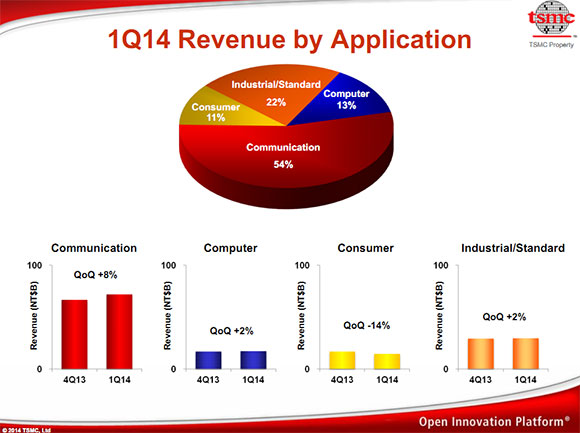

L'importance des SoC/modems pour smartphones dans les revenus de TSMC (colonne « Communication ») est assez facilement illustrée par ce graphique, par rapport aux revenus informatiques et GPU que l'on retrouve dans la colonne « Computer ».

Concernant le 16nm, le constructeur a annoncé une seconde version de son process. En sus du 16-FinFET déjà annoncé et censé entrer en production en février prochain, TSMC annonce une version « plus » de son process. Il s'agira en quelque sorte d'une version optimisée du 16nm basé sur des optimisations non dévoilées, les règles de design restant les mêmes entre le 16-FinFET et le 16-FinFET plus. La stratégie n'est pas très différente de ce que proposeront Samsung et GlobalFoundries sur ce point avec le 14LPE et le 14LPP qui sera proposé dans un second temps.

Contrairement à Samsung, TSMC livre quelques chiffres sur son process 16-FinFET plus qui apportera, par rapport à la première version, un gain au choix de 15% de vitesse à consommation égale, ou de 30% de gain de consommation à vitesse égale. Des gains qui sont loin d'être négligeables. Côté timing, le constructeur évoque une qualification de son process en septembre de cette année suivis de quelques « tape-outs » (15 en 2014) et une production en volume « courant » 2015.

TSMC a également parlé de son process 10nm, baptisé 10-FinFET, indiquant qu'il est en cours de développement. Le 10-FinFET est qualifié de troisième génération de FinFET par la société sans plus de détails. Quelques chiffres ont été livrés comparant au 16-FinFET plus avec une amélioration de la densité de 2.2x, et 25% de vitesse à consommation égale, ou 45% de gain de consommation à vitesse égale. D'un point de vue implémentation technique, le seul détail donné concerne l'EUV (une source lumineuse avec une longueur d'onde de 13nm, contrairement aux actuelles sources 193nm) qui, sans trop de surprise, ne sera toujours pas prêt pour le 10nm. TSMC laisse la porte ouverte pour l'utilisation de l'EUV plus tard dans la vie du process. TSMC devrait donc utiliser d'une manière plus forte le multiple patterning, augmentant potentiellement les couts. Un point sur lequel il est pour l'instant un peu trop tôt pour se prononcer.

Contenus relatifs

- [+] 27/04: Le 10nm d'Intel (encore) retardé, l...

- [+] 30/01: TSMC confiant sur l'EUV en volume p...

- [+] 30/01: L'activité d'Intel poussée par le s...

- [+] 29/11: Samsung lance la production en volu...

- [+] 19/10: Samsung annonce la qualification de...

- [+] 03/07: Apple premier en 10nm chez TSMC

- [+] 29/05: ARM annonce les Cortex-A75, A55 et ...

- [+] 29/05: Samsung détaille sa roadmap jusqu'a...

- [+] 29/03: Intel Technology and Manufacturing ...

- [+] 10/02: Intel : Core 8è gen, 10nm et 7nm