Samsung détaille sa roadmap jusqu'au 4nm

Samsung a donné quelques détails sur les prochaines versions de ses process de fabrication, annonçant pas moins de cinq nouveaux process baptisés 8LPP, 7LPP, 6LPP, 5LPP et... 4LPP. Quelques informations sont données sur les différences. Ainsi, le 8LPP sera une variante du process 10nm de Samsung qui profitera de gains de performances ainsi que de gains de densité, possiblement par l'utilisation de nouvelles bibliothèques (les blocs de base qui servent à créer les puces).

Le 7LPP sera le prochain "vrai" node de Samsung. Prévu pour la fin 2018, il s'agira du premier node à introduire la lithgraphie EUV. Le constructeur indique dans son communiqué de presse avoir co-développé avec ASML une source lumineuse 250W pour cette mise en production (pour rappel, tous les fabricants ont collaboré avec ASML sur l'EUV, TSMC évoquait également 250W fin 2018 pour la mise en production de l'EUV).

Le 6LPP sera une variante optimisée du 7LPP qui utilisera ce que le marketing appelle du "Smart Scaling", diverses techniques permettant d'améliorer la densité. Il s'agira surtout pour Samsung de profiter de l'apprentissage de son premier process EUV pour optimiser légèrement les choses.

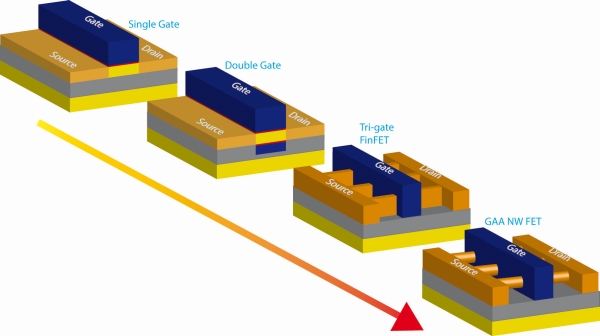

Le 5LPP sera vraisemblablement le "node" suivant au sens traditionnel du terme, il servira à préparer le terrain pour le suivant. Car c'est au niveau du 4LPP qu'un gros changement arrivera avec un passage à un nouveau type de structure de transistor. Samsung utilisera des transistors dit Gate All Around (GAAFET) qui sont une variante des FinFET où la Gate entoure le canal. La version de Samsung sera baptisée MBCFET (Multi Bridge Channel FET) et utilisera une nanosheet sur laquelle aucun détail n'est donné pour l'instant.

Les différences entre les types de transistors (source )

Ces nodes et ces variantes devraient apparaître progressivement dans les années à venir, Samsung évoquant simplement son 4LPP pour 2020 pour ne pas s'engager plus fortement sur le timing. On ne leur en tiendra pas rigueur, il est assez rare que les fondeurs partagent publiquement, et avec tant de visibilité leur roadmap.

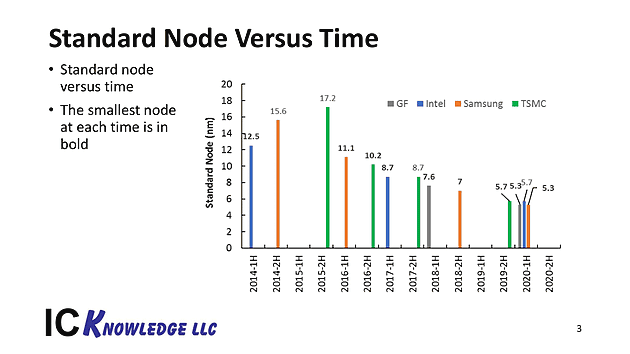

On pourra bien entendu s'interroger sur les nomenclatures choisies par Samsung, mais au-delà de cela, la tendance reste commune chez tous les fondeurs qui multiplient les variantes d'un même process. TSMC en est à sa quatrième version de "16nm", baptisée pour le coup 12FFC, tandis qu'Intel annonçait fin mars pour la première fois trois versions de 14nm et de 10nm.

Derrière ces annonces, on retrouve des constatations communes, il est de plus en plus difficile de réduire la taille des puces, et les gains de performances et de densités apportés ne sont plus forcément aussi importants qu'auparavant (même si les fondeurs, Intel en tête, continuent d'innover sur les formules mathématiques pour ne pas dire que la loi de Moore ralentit).

Le passage au 5nm chez tous les fondeurs est attendu autour de 2020 en production risque, même si chez Intel on parlerait logiquement de "7nm", cf cette roadmap basée sur des estimations publiées sur le blog SemiWiki

Mais au-delà du marketing derrière les variantes, le rythme annoncé par Samsung reste assez soutenu laissant penser à un écart de deux ans entre le 7nm et le 5nm, ce qui est très agressif et aligné sur ce que devrait proposer TSMC (qui lancera son 7nm d'abord sans EUV, le 8LPP lui étant opposé par Samsung). TSMC a confirmé qu'il lancera le début de sa production en 7nm ce trimestre (la production en volume est attendue l'année prochaine). Le 5nm démarrera ses essais de production en 2019 pour une production volume en 2020 chez le fondeur taiwanais.

La confiance de Samsung sur l'EUV est également un point que l'on ne négligera pas, la lithographie à immersion touche aujourd'hui ses limites et si les problèmes de l'EUV ne sont pas tous résolus, la technologie devrait donner un peu de marge aux fondeurs.

Contenus relatifs

- [+] 27/04: Le 10nm d'Intel (encore) retardé, l...

- [+] 27/04: AMD Vega 7nm en labo, Zen 2 échanti...

- [+] 08/03: GlobalFoundries : 12nm, 7nm et EUV

- [+] 30/01: TSMC confiant sur l'EUV en volume p...

- [+] 30/01: L'activité d'Intel poussée par le s...

- [+] 09/01: CES: Silence sur l'après Pascal che...

- [+] 29/11: Samsung lance la production en volu...

- [+] 19/10: Samsung annonce la qualification de...

- [+] 21/09: AMD utilisera le 12nm de GloFo en 2...

- [+] 11/09: Un nouveau 14nm chez Samsung