Actualités divers

64 Go de DDR3-2400 chez G.Skill

L'USB à l'attaque de la vidéo ?

Panther Point certifié USB 3.0

Xilence Interceptor Pro, boitier extrême à 299

IBM va produire l'Hybrid Memory Cube

CES: PRISM et DirectTouch pour Tegra 3

Décidemment, le SoC quadcore Kal-El commercialisé sous la marque Tegra 3 est plein de surprises. Après l'annonce d'un 5ème core destiné à réduire la consommation en prenant le relais des 4 cores principaux lorsque la charge est faible, ce sont deux nouvelles technologies que Nvidia vient de dévoiler lors de ce CES.

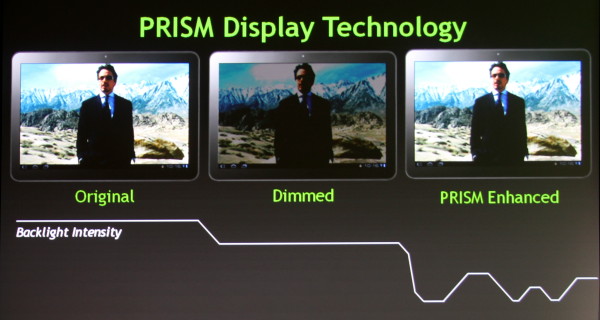

La première se nomme PRISM et permet selon Nvidia de réduire considérablement la consommation liée à l'écran sans réduire la luminosité perçue. Pour cela le contrôleur en charge de l'affichage du SoC Tegra va séparer les informations de couleur et d'intensité lumineuse du rétroéclairage de manière à les optimiser pour réduire la consommation.

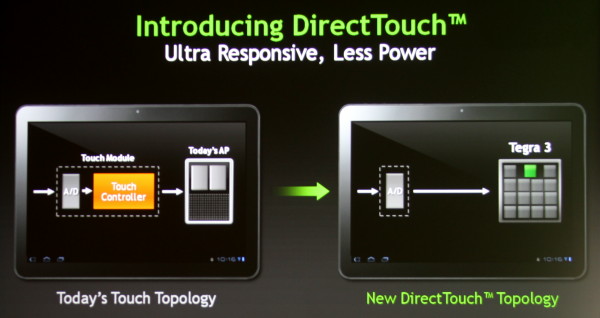

La seconde, DirectTouch, consiste à se passer d'un contrôleur dédié aux écrans tactiles, à renvoyer les informations de la dalle vers le SoC Tegra 3 et à les traiter d'une manière logicielle. Grâce au 5ème core très peu gourmand, cela peut, toujours selon Nvidia, se faire sans réduire l'efficacité énergétique de la plateforme. Autre avantage, cette approche permet de profiter si nécessaire de la puissance du SoC pour démultiplier le nombre d'impulsions prises en charge par seconde. Une démo mettait en évidence un gain à ce niveau de près de 3x, qui peut être exploité pour rendre les interfaces plus réactives.

Nous ne savons pas par contre si ces technologies sont exploitées par les premiers périphériques Tegra 3 tels que la Transformer Prime d'Asus ou même sur la future tablette 7" du fabricant basée sur la même plateforme et qui sera commercialisée au prix plutôt agressif de 249$.

Jerry Chen, le CEO d'Asus et Jen Hsun Huang, le CEO de Nvidia, dévoilent une future tablette 7".

Thermaltake Frio Extreme

La marque taïwanaise Thermaltake vient de lancer un nouveau modèle de radiateur processeur, le Frio Extreme. Annoncé avec une capacité de refroidissement de 250 watts, ce modèle est composé de six caloducs qui traversent deux tours séparées, un design à l'image des Noctua NH-D14 et Thermalright Silver Arrow que nous avions testés précédemment.

Il est livré avec deux ventilateurs 14 cm compatibles PWM, Thermaltake livrant en sus un adaptateur permettant de faire varier la vitesse entre 1200 et 1800 RPMs. L'adaptateur peut aussi fonctionner en mode régulation de tension si l'on le souhaite. Côté compatibilité, on retrouve tous les sockets allant du 775 au 2011 chez Intel ainsi que du FM1 à l'AM3+ chez AMD. Le prix de ce nouveau modèle haut de gamme n'est pas encore indiqué.

Rapprochement Elpida-Nanya ?

Le quotidien Nikkei Business Daily rapporte aujourd'hui (via Reuters ) que le fabricant de mémoire japonais Elpida (le dernier acteur japonais du marché) envisagerait un rapprochement stratégique avec son concurrent taïwanais Nanya. Dans un marché particulièrement concurrentiel et dominé par Samsung et Hynix (respectivement 45 et 21.5%), Elpida reste aujourd'hui à la troisième place avec 12.1% de parts (au coude à coude avec Micron) pour le troisième trimestre 2011.

Ayant déjà profité d'un plan de refinancement de la part du gouvernement japonais, Elpida reste à la tête de 5 milliards de dollars de dettes. Le rapprochement, sous la forme d'une joint venture avec Nanya (faisant partie du Formosa Plastics Group, également maison mère de VIA) serait évoqué comme l'un des scénarios possibles avec une transition de la production sur Taiwan. Nanya a démenti être en pour parlers, indiquant que la seule relation en cours entre les deux sociétés concerne un procès en cours autour de brevets détenus par Elpida.

Micron 3DS au JEDEC ?

Micron a publié la semaine dernière sur l'un de ses blogs un billet intéressant sur un nouveau type de die stacking en développement baptisé 3DS et dédié spécifiquement à la mémoire.

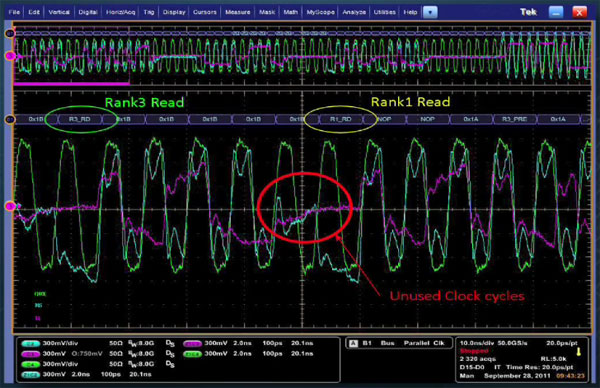

Dans le cas ou l'on superpose les puces mémoires, une approche traditionnelle est de connecter directement les puces au contrôleur mémoire. Pour 3DS, Micron propose d'utiliser un système maitre/esclave entre les puces. Seule la puce inférieure étant connectée directement au contrôleur mémoire, les puces supplémentaires étant simplement connectées à la puce directement en dessous d'eux.

L'introduction d'un système maitre/esclave permet de réduire la partie logique des puces mémoires, chaque pile de puces partageant une seule DLL et une seule interface externe. L'existence d'une interface intermédiaire peut cependant créer une latence lors d'accès successifs entre les deux puces. Estimée à un cycle normalement, Micron indique que sa technologie permet de supprimer cette latence par une innovation (non précisée) au niveau de la gestion des commandes de lectures.

La marque a publié une vidéo Youtube mettant en avant une barrette mémoire registered de 32 Go via 36 stacks de 8 Gb, chacune d'entre elle utilisant une puce maitre de 4 Gb et une puce esclave de 4 Gb également. Micron indique travailler avec le reste du JEDEC sur l'adoption du die stacking, le 3DS étant l'une des technologies considérées par le consortium de standardisation dédié à la mémoire.

Cortex-A9 en 28 et 20nm pour GloFo

GlobalFoundries vient d'effectuer deux annonces liées indirectement aux processeurs ARM. La société à tout d'abord annoncé l'arrivée d'un processeur ARM Cortex-A9 gravé en 28nm qui aura atteint la fréquence de 2.5 GHz. Contrairement à l'annonce de tapeout en 28nm précédente, il ne s'agit pas ici du process 28nm-SLP dédié à la mobilité mais le HPP, dédié aux applications filaires/réseau (NAS, routeurs, etc).

L'annonce confirme la roadmap précédemment communiquée par GlobalFoundries qui indiquait une disponibilité du process avant la fin de l'année. La version "hautes performances", le 28nm-SHP reste toujours attendu pour 2012 sans plus de précisions. C'est cette version qui pourra éventuellement être utilisée par AMD pour de futurs CPU, les AMD FX utilisant le 32nm-SHP.

La deuxième partie de l'annonce concerne le tapeout d'un Cortex-A9 en 20nm sur la plateforme de qualification, il ne s'agit cette fois ci que d'une puce de test, le process 20nm de GlobalFoundries n'étant pas prévu avant 2013 en version SLP et HPP. Sans préciser quelle version du process 20nm est utilisée, GlobalFoundries indique espérer une augmentation des performances des transistors de 35% et une division par deux de la consommation par rapport au 28nm.