Micron 3DS au JEDEC ?

Publié le 20/12/2011 à 13:35 par Guillaume Louel

Micron a publié la semaine dernière sur l'un de ses blogs un billet intéressant sur un nouveau type de die stacking en développement baptisé 3DS et dédié spécifiquement à la mémoire.

Dans le cas ou l'on superpose les puces mémoires, une approche traditionnelle est de connecter directement les puces au contrôleur mémoire. Pour 3DS, Micron propose d'utiliser un système maitre/esclave entre les puces. Seule la puce inférieure étant connectée directement au contrôleur mémoire, les puces supplémentaires étant simplement connectées à la puce directement en dessous d'eux.

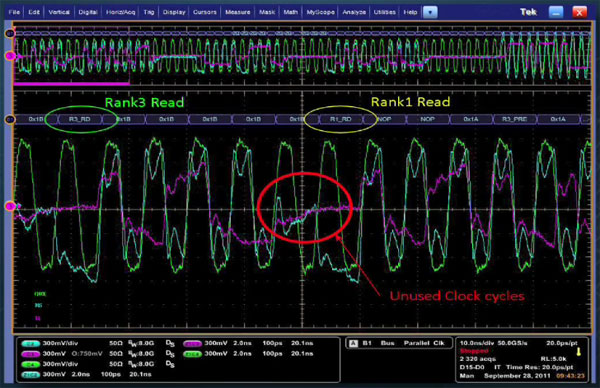

L'introduction d'un système maitre/esclave permet de réduire la partie logique des puces mémoires, chaque pile de puces partageant une seule DLL et une seule interface externe. L'existence d'une interface intermédiaire peut cependant créer une latence lors d'accès successifs entre les deux puces. Estimée à un cycle normalement, Micron indique que sa technologie permet de supprimer cette latence par une innovation (non précisée) au niveau de la gestion des commandes de lectures.

La marque a publié une vidéo Youtube mettant en avant une barrette mémoire registered de 32 Go via 36 stacks de 8 Gb, chacune d'entre elle utilisant une puce maitre de 4 Gb et une puce esclave de 4 Gb également. Micron indique travailler avec le reste du JEDEC sur l'adoption du die stacking, le 3DS étant l'une des technologies considérées par le consortium de standardisation dédié à la mémoire.

Vos réactions

Contenus relatifs

- [+] 04/05: Cadence et Micron pour la DDR5-4400

- [+] 19/01: SK Hynix va aussi lancer une HBM à ...

- [+] 19/01: La GDDR6 annoncée disponible chez S...

- [+] 15/01: Samsung atteint 2.4 Gbps en HBM2

- [+] 22/12: Samsung grave de la DRAM en ''1ynm'...

- [+] 24/11: Le prix de la RAM pousse les ventes...

- [+] 04/10: La DDR4 toujours en hausse, pénurie...

- [+] 21/09: Toshiba choisi Bain Capital pour se...

- [+] 14/09: Les prix de la DDR4 ont doublé en u...

- [+] 14/09: Toshiba rejette une fois de plus We...