Actualités mémoires

Nouvelle étape pour la PRAM !

Computex: Plus de Go et de MHz chez G.Skill

Computex: Modules 8 Go en approche chez ADATA

8 Go en DDR3-2400 pour Corsair

8 Go DDR3-2300 chez G.Skill

Prix de la DDR3 au plancher ? 25nm à la rescousse

Après être passé au 30nm en début d'année, Elpida poursuit sur sa lancée et est le premier à annoncer l'échantillonnage de mémoire DDR3-SDRAM gravée en 25nm, la production en volume ayant également débuté. Cette finesse accrue permet de produire environ 30% de plus de puces par wafer qu'en 30nm, un point essentiel à l'heure où le prix de vente des puces est si bas qu'il semble être sous le coût de production.

Une puce de 256 Mo de DDR3-1333 se négocie en effet 1.15$ seulement, contre 1.48$ début juillet, 2.10$ début avril et 3.0$ en novembre. Ceci permet aux kits de 8 Go (2x4 Go) DDR-1333 de commencer à se trouver sous les 40 ! Cette situation parait difficilement tenable sur la durée pour les fabricants et elle ne devrait donc pas perdurer des mois, car à défaut d'une demande plus importante, les constructeurs devraient ajuster leur capacité de production (n'hésitez pas à vous équiper !).

L'abaissement de la finesse de gravure reste essentiel pour soutenir cette guerre des prix et Elpida a donc une longueur d'avance dans ce domaine. Ces nouvelles puces de 256 Mo sont en sus moins énergivores puisque nécessitant une intensité inférieure de 15% en charge et 20% au repos par rapport aux versions 30nm. Côté performances, Elpida parle d'un fonctionnement en DDR3-1866 et plus en 1.5v et en DDR3-1600 à 1.35v.

DDR3-2133 1.5V chez Corsair

Corsair annonce un nouveau kit mémoire 8 Go (2x4 Go) DDR3-2133 9-11-9 ayant l'originalité de fonctionner à 1.5v, une première. En effet, jusqu'à présent les kits DDR3-2133 9-11-9 étaient à 1.65v, voir 1.5v à condition de se contenter de latences de 11-11-11.

Livrées avec un ventilateur optionnel, ce kit Dominator GT CMT8GX3M2A2133C9 qualifié sur les plates-formes P67 et P55 ne sera disponible que sur le site de Corsair et au tarif élevé de 499$.

Voilà qui est très cher payé pour 0.15v sachant qu'un kit tel que le F3-17000CL9D-8GBXLD de G.Skill (DDR3-2133 9-11-9 à 1.65v, également fournit avec ventilateur) est trois fois moins onéreux alors qu'il est lui-même déjà au moins deux fois plus cher que les kits 8 Go DDR3-1600 9-9-9 1.5v plus classiques.

Hynix et Toshiba s'associent pour la MRAM

Le sud-coréen Hynix et le japonais Toshiba viennent d'annoncer leur collaboration pour le développement de la MRAM. Une fois le développement terminé, les deux compagnies entendent également coopérer au sein d'une joint-venture pour la production de la dite mémoire. Hynix et Toshiba indiquent qu'ils ont également étendus leur accord de licence croisé et de sous-traitance.

Cette alliance est assez étonnante puisque Hynix et Samsung avaient annoncés en 2008 la création d'une joint-venture 100% sud-coréenne vouée au co-développement et la standardisation de la MRAM. Ce projet est semble-t-il tombé à l'eau, alors que l'accord Hynix Toshiba intervient une semaine après la publication d'une nouvelle avancée de Toshiba dans le domaine de la MRAM.

Ce type d'alliance est assez habituel dans le secteur de la mémoire puisqu'il permet de réduire les risques liés au développement d'une nouvelle technologie et d'en accélérer la mise au point. Dans le domaine de la mémoire Flash NAND par exemple, Toshiba et SanDisk collaborent au sein de Flash Forward, alors qu'Intel et Micron sont regroupés sous IM Flash.

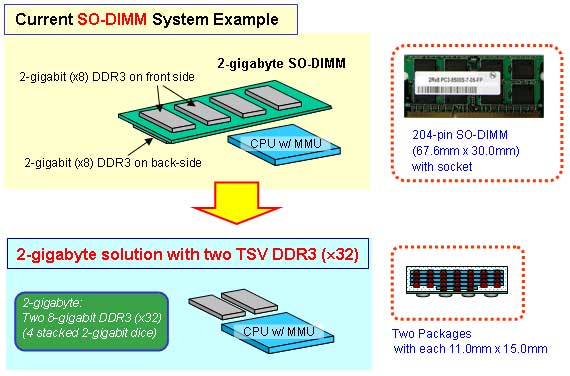

1 Go DDR3 TSV pour Elpida

Elpida a commencé à livrer les échantillons d'une mémoire de 1 Go DDR3 utilisant la technologie TSV (Through Silicon Via). Cette technologie permet de relier plusieurs die entre eux via des connexions verticales qui passent donc au travers même des die. Cette verticalité permet de réduire drastiquement la longueur des connexions, ce qui permet entre autre d'améliorer la vitesse, d'abaisser la consommation et de réduire la taille du packaging. Attention, si certains parlent de "Puces 3D" pour cette technologie, elle n'est pas à confondre avec les transistors Tri-Gate ou "3D" mis au point notamment par Intel.

La puce de 1 Go DDR3 TSV mise au point par Elpida combine 4 die 256 Mo capables de fonctionner en DDR3-1600 à 1.5v et en 1333/1066 à 1.35v. L'utilisation de deux puces de ce type en lieu et place d'une barrette SO-DIMM de 2 Go classique permet selon Elpida d'abaisser de 50% la consommation en charge et 20% la consommation au repos. Elpida suggère d'ailleurs que ceci peut permettre de se passer de SO-DIMM pour intégrer la mémoire directement sur le PCB, mais ceci se fait alors au dépends des possibilités de mises à jour.

Elpida travaille sur la technologie TSV depuis 2004, et avait annoncé en 2009 être le premier à avoir développé une puce mémoire DDR3 de 1 Go. Après le stade du développement, Elpida passe donc désormais à l'échantillonnage sur cette nouvelle puce, mais n'indique pas de date pour la disponibilité en volume.

Le fabricant n'est toutefois pas le seul sur cette technologie et tous les fondeurs travaillent dessus. Samsung a par exemple annoncé en décembre dernier avoir développé une barrette RDIMM de 8 Go à base de puces mémoire DDR3 40nm TSV qui était jusqu'à 40% plus économe qu'une barrette RDIMM conventionnelle. Samsung précisait alors que la technologie TSV devrait commencer à se democratiser à partir de 2012.

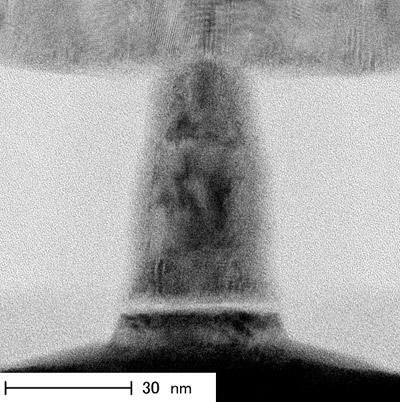

Nouvelle étape pour la MRAM !

Après la PRAM, c'est autour d'une autre arlésienne, la MRAM, de franchir une étape significative dans son développement. Pour rappel, cette mémoire non volatile n'utilise pas une charge électrique pour stocker les bits contrairement à la DRAM, mais une charge magnétique, à l'instar les disques durs. Depuis ses débuts, elle est présentée comme la mémoire idéale, capable de remplacer la DRAM, la SRAM et la NAND.

La lecture des données utilise le principe de la magnétorésistance à effet de tunnel, en mesurant la différence de potentiel entre deux couches ferromagnétiques. L'écriture se fait en modifiant le spin des électrons dans une des ces deux couches.

L'avancée présentée par Toshiba se situe au niveau de l'élément de base d'une mémoire STT-MRAM (spin torque transfert MRAM) qui intègre ces deux couches ferromagnétiques, le MTJ (magnetic tunnel junction). Ce nouveau MTJ nécessite en effet une intensité 6 fois plus faible pour l'écriture, alors que l'écart de résistance entre les états correspondants aux bits 0 et 1 passe de 15 à 200%, ce qui permet de fiabiliser la lecture.

Toshiba annonce ainsi qu'il a pu réduire l'intensité nécessaire pour écrire un MTJ de 50nm à 9µA, et qu'un MTJ de 30nm devrait être parfaitement fonctionnel. Selon le constructeur, les prévisions de l'ITRS (International Technology Roadmap for Semiconductors) sur la STT-MRAM ne tablaient pas sur de telles performances avant 2024.

Cette avancée ouvre la voie à la commercialisation d'ici 3 à 4 ans de puces STT-MRAM offrant des densités de l'ordre d'un Gigabit. Toshiba vise une production en volume dans un processus de fabrication antérieur d'une génération par rapport à celui utilisé sur la DRAM, ce qui ne l'empêche pas d'indiquer que les coûts de production des STT-MRAM et DRAM devraient être proches. Rendez-vous en 2015 pour voir si la promesse est tenue !