Actualités mémoires

Micron et Elpida, c'est fait

DDR3-3100 pour ADATA

La DDR3 de plus en plus chère

Computex: Toujours plus de MHz pour la DDR3

Hynix signe un accord de licence avec Rambus

Mémoire en hausse suite à un incendie chez SK Hynix

Mercredi dernier, une usine de SK Hynix située à Wuxi en Chine a été victime d'un incendie qui n'a heureusement pas fait de victimes graves. Cette usine produit environ 40% de la mémoire de SK Hynix, qui est avec 30% de parts de marché sur le second trimestre le numéro 2 du secteur derrière Samsung (32,7%) et devant Micron / Elpida (28,1%).

SK Hynix a indiqué le jour même qu'il évaluait toujours l'étendue des dégâts, mais que les équipements de productions dans la salle blanche n'étaient pas touchés et qu'il s'attendait à reprendre la production dans un délai limité, sans impact sur la production globale. Il faut dire que les lignes de production de DRAM sont loin d'être surchargées et SK Hynix comme ses concurrents ont la possibilité d'augmenter, au moins temporairement, la cadence sur d'autres lignes de production.

Certaines sources sont toutefois moins optimistes sur la durée de l'arrêt de l'usine, parlant de un mois pour certains et six mois pour d'autres. Comme on pouvait s'y attendre, dès le lendemain le prix des puces mémoires a bondi, mais la hausse est restée contenue ce vendredi (+1-2%) ce qui tend à aller dans le sens d'une résolution rapide de la situation.

En attendant, il fallait compter 1,576$ et 3,143$ pour des puces de 256 et 512 Mo de DDR3-1600 en début de semaine, les prix sont passés à 1,941$ et 3,505$ cette fin de semaine soit 23,2 et 11,5% de hausse.

On revient en fait au plus haut de l'année atteint début juillet pour les puces 256 Mo, alors qu'on reste encore en dessous des 3,71$ d'alors pour les 512 Mo. Fin novembre 2012, les prix étaient au plus bas, respectivement à 0,82 et 2,01$.

L'Hybrid Memory Cube en production en 2014

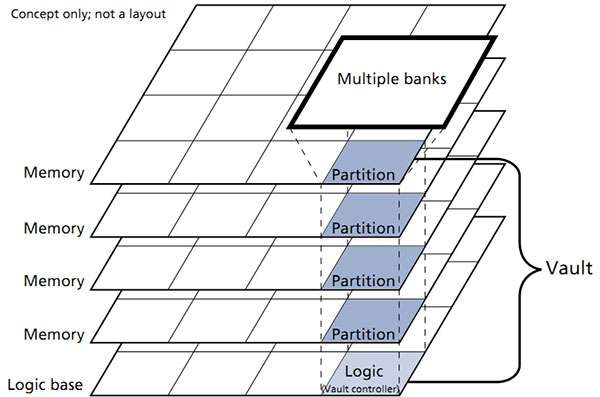

Nous vous avions parlé en 2011 du concept de l'Hybrid Memory Cube. Sur le papier il s'agit d'un concept simple, superposer une couche logique de contrôleurs mémoires avec de multiples dies de mémoire DRAM reliés les uns aux autres par des TSV (Through Silicon Vias, littéralement des fils qui passent au travers des différents dies, à l'opposée de la solution "classique" ou l'on fait passer les fils par le côté).

Chaque colonne sur le schéma représente un "vault" qui dispose en bas dans la couche logique de son propre contrôleur mémoire indépendant. L'avantage du système est d'être capable d'atteindre des bandes passantes très élevées, on parlait déjà en 2011 de 128 Go/s sur une seule puce !

Sur cet autre schéma, on peut voir le principe un peu plus en détail avec une puce qui superpose neuf dies (8 mémoires, un logique). On retrouve ici 16 vaults, chaque contrôleur est relié à un switch puis à quatre liens point à point vers l'extérieur de la puce. Ces nombres étant bien entendu modulables. Notez également que les cubes sont chainables entre eux.

Micron et d'autres sociétés (notamment ARM, HP, Hynix, IBM et Samsung) se sont alliés pour mettre en place un consortium dans le but de développer un standard commun. On notera avec un étonnement certain l'absence d'Intel dans ce consortium, alors que la société avait pourtant effectué les démonstrations lors de l'IDF 2011. La spécification (PDF) a été publiée en avril avec des débits très prometteurs allant de 160 à 240 Go/s pour les modèles à quatre liens (en fonction de la vitesse individuelle des liens), et 320 Go/s pour le modèle huit liens.

Micron avait indiqué en 2011 que c'est IBM qui produirait dans son process 32nm HKMG. Aujourd'hui, dans un communiqué qui parle de l'intérêt de l'intégration avec des FPGA, Micron s'engage un peu plus sur les dates en annonçant la livraison d'échantillons avant la fin de l'année, et surtout une production en volume pour 2014. On ne sait pas s'il s'agira toujours d'un process 32 HKMG. En déportant les contrôleurs mémoires directement dans les puces mémoires, l'Hybrid Memory Cube propose en plus d'un bond net de bande passante la possibilité de repenser les sous systèmes mémoires des processeurs. Reste à voir dans quel cadre elle pourra être utilisée. Le consortium indique viser très clairement les CPU et les GPU. Auprès de ces puces, l'HMC jouerait alors un rôle hybride à mi chemin entre ce que propose l'eDRAM et la mémoire traditionnelle.

Samsung produit de la DDR4 en volume

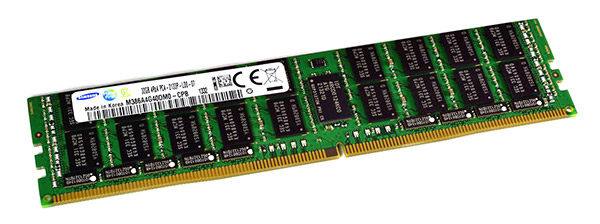

Samsung vient d'annoncer qu'il avait débuté la production en volume de puces DDR4 de 512 Mo. Gravées avec un process de "classe 20nm" (entre 20 et 29 donc), ces puces fonctionnent au mieux en mode DDR4-2667, soit 25% de mieux que la DDR3 "officielle" qui plafonne à la DDR3-2133 et pour une consommation en baisse de plus de 30%.

Le géant de la mémoire a notamment intégré ces puces sur un module ECC Registered de 32 Go, limité au mode DDR4-2133, qui devrait faire le bonheur de futurs serveurs. Rappelons toutefois qu'il faudra attendre 2014 pour que la DDR4 soit gérée sur ce type de plate-forme chez Intel (Ivy Bridge-EX et Haswell-E) ... c'est donc un peu tôt pour une production en volume !

GDDR5M 4 Gbps en SO-DIMM pour Kaveri ?

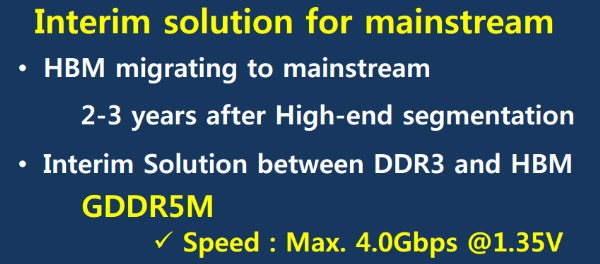

Malgré l'effervescence du net, certaines informations parviennent étrangement à passer relativement inaperçues. C'est le cas de la mémoire GDDR5M visiblement destinée à cohabiter avec la DDR4 tout en permettant de profiter d'une bande passante largement supérieure, et ainsi patienter en attendant l'arrivée des mémoires de type Wide I/O2, HBM ou encore HMC.

La GDDR5M, dont les spécifications principales ont été fixées par le JEDEC l'an passé, est une variante de la technologie GDDR5 adaptée au format "barrette mémoire" et plus précisément au SO-DIMM. Pour cela, deux modifications principales étaient nécessaires. Ainsi, par rapport à des modules soudés directement sur le PCB comme, c'est le cas sur les cartes graphiques ou sur la PS4, les contraintes sont plus importantes au niveau de l'intégrité des signaux électrique, ce qui impose de limiter la fréquence.

Ensuite, les modules GDDR5 sont interfacés en 32-bit avec une possibilité de les associer par paires (mode "clamshell") pour doubler la quantité de mémoire. Une interface relativement large qui limite l'espace mémoire maximal d'une barrette. Le format SO-DIMM, comme le DIMM classique, prévoit un canal de données large de 64-bit, qui peut donc accommoder au mieux 4 modules GDDR5 en mode clamshell, soit 2 Go par barrette si nous nous basons sur la densité maximale qui vient tout juste d'entrer en production (4 Gbits). Tout comme la GDDR5 la plus récente, la GDDR5M est prévue avec une densité de 4 Gbits mais cette fois interfacée en 16-bit ce qui permet au passage de réduire le nombre de pins de 170 à 96, comme c'est le cas pour la DDR3 destinée aux GPU. De quoi pouvoir monter à 4 Go par module SO-DIMM.

Hynix semble être le premier acteur, voire l'unique, sur ce type de mémoire. Le fabricant prévoit des modules cadencés à 1 GHz en 1.5V, à 900 MHz en 1.5V ou 1.35V et enfin à 800 MHz en 1.35V. De quoi représenter des débits par pin de 3.2 à 4.0 Gbps, ce qui peut sembler faible par rapport au débit de 7.0 Gbps de la GDDR5 la plus rapide (GeForce GTX 770). Il faut cependant placer la GDDR5M dans le contexte SO-DIMM et elle se montre alors sous un meilleur jour face au débit maximal de 1.6 Gbps pour la DDR3 et aux débits actuellement prévus de 1.6 à 2.4 Gbps pour la DDR4.

De quoi proposer un gain substantiel par rapport à cette dernière, d'autant plus que l'arrivée commerciale de la GDDR5M pourrait intervenir plus tôt. D'après ce document qui date du début de l'année, c'est en ce moment qu'Hynix commence à fournir les premiers échantillons de tests à ses clients, pour une production en volume qui devrait logiquement intervenir au premier semestre 2014.

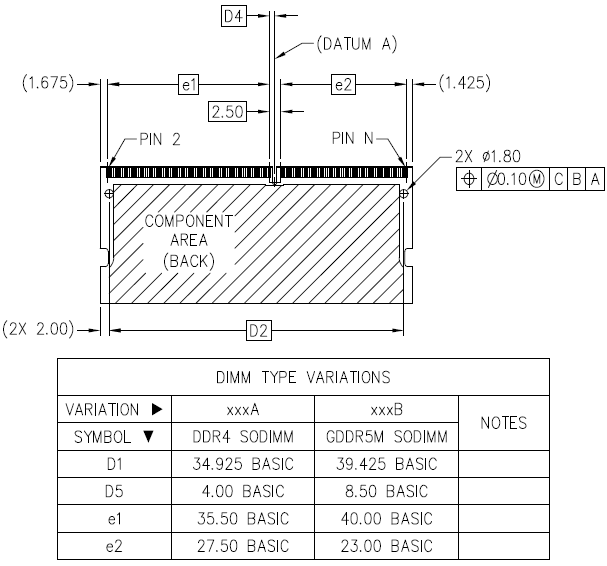

Physiquement, un module SO-DIMM GDDR5M sera très proche d'un module SO-DIMM DDR4, tous deux partageant le même format 256 pins. Seule la position du détrompeur, un petit peu plus excentré pour la première, permettra de les différencier. Notez que tout semble indiquer qu'il ne sera pas possible de prévoir un connecteur compatible avec les deux types de mémoire.

Quelle utilité pour cette GDDR5M dont le support n'a à ce jour été annoncé officiellement par personne ? De toute évidence, Intel qui a l'habitude de dévoiler ses plans largement à l'avance, n'a pas prévu d'exploiter ce type de mémoire. C'est plutôt du côté d'AMD qu'il faut chercher, d'autant plus que le président du comité JEDEC en charge des mémoires DRAM n'est autre que Joe Macri, Chief Technology Officer en charge des plateformes grand public chez AMD. Par ailleurs, en produisant un APU ou SoC équipé d'un contrôleur mémoire GDDR5 pour la PS4 de Sony, AMD a déjà fait un pas vers l'utilisation de ce type de mémoire.

Prévu pour début 2014, l'APU Kaveri a tout du suspect parfait et pourrait ainsi supporter la GDDR5M de manière à offrir plus de bande passante à son GPU. Une manière en quelque sorte de répondre à l'eDRAM embarquée par Intel sur les CPU Haswell équipés de la variante GT3e du GPU intégré (Iris Pro 5200).

Le fait que seul un module SO-DIMM ait été prévu à l'heure actuelle laisse penser que cette mémoire est avant tout destinée aux portables, ce qui est logique. Ils sont en effet les plus à mêmes de trouver de la valeur dans un GPU intégré aux performances en hausse à travers l'utilisation d'une mémoire qui sera bien entendu plus chère. Ceci dit, si Kaveri s'avérait bel et bien compatible avec cette mémoire GDDR5M, rien n'empêcherait le design d'une carte-mère desktop équipée de slots SO-DIMM 256 pins.

Un nouvel acteur dans la Resistive RAM

Une startup a cherché (et réussi) à faire parler d'elle ces derniers jours en annonçant avoir développé un prototype de Resistive RAM (ou RRAM). Cette technologie mémoire dérivée du Memristor, prédit en 1971 et implémenté par Hewlett Packard pour la première fois en 2008, est censée cumuler les avantages de la NAND et de la DRAM, à savoir l'aspect non volatile de la NAND (les données ne s'effacent pas quand la mémoire n'est plus alimentée, contrairement à la RAM) et la rapidité d'accès aléatoire de la DRAM.

Ce n'est bien entendu pas le premier prototype du genre puisque l'on se souvient par exemple que Elpida (avec Sharp), mais aussi Hewlett Packard (avec Hynix), Samsung ou Panasonic ont annoncé respectivement des prototypes, et même Rambus s'intéresse au sujet, tout comme divers instituts de recherche comme l'ITRI ou l'IMEC .

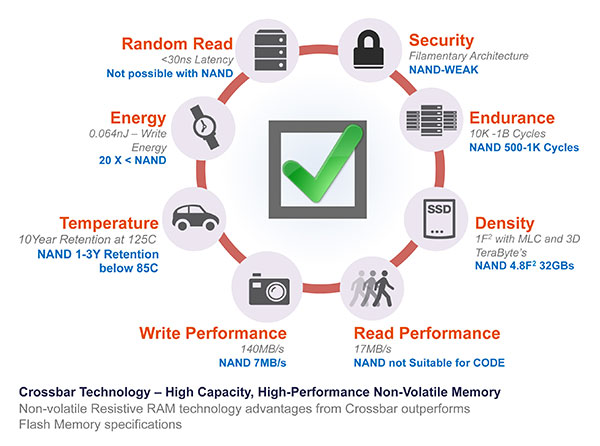

Le communiqué avance de gros chiffres : 20x plus rapide en écriture, une consommation 20x inférieure, et 10x l'endurance pour la moitié de la surface comparé à la meilleure NAND disponible actuellement. Le tout illustré par ce schéma :

On ne manquera pas de relever plusieurs grossières approximations sur le schéma, si le chiffre de 140 Mo/s en écriture est tout à fait remarquable, dire que la meilleure NAND peut seulement écrire à 7 Mo/s est un large raccourci. De même le graphique fait le choix de comparer les performances en lecture en aléatoire (bit par bit) à la NAND, alors que cette dernière ne s'accède pas de la sorte. Crossbar ne donne pas de chiffre pour sa RRAM en accès séquentiels, se contentant d'un 17 Mo /s en aléatoire alors qu'en séquentiel une puce de NAND classique se situe autour de 100 Mo /s.

A noter que si Crossbar indique sur ce schéma que le mode aléatoire n'est pas applicable à la flash, ce n'est pas le cas de ce white paper (PDF) , ou est indiqué 0.04 Mo/s (sic) pour la NAND avec le commentaire "RRAM will provide faster NAND-like products". En fait comme la flash de type NOR, la RRAM a l'avantage de disposer d'un accès pleinement aléatoire (les cellules sont connectées en parallèle et accessibles individuellement, et non pas en série comme sur la NAND) ce qui permet d'exécuter directement un programme sans devoir le charger en DRAM. Certaines valeurs de ce white paper, qui date pourtant de cette année, ne correspondent pas à l'illustration. Il parlait de 20 ans pour la rétention (contre 10 pour ce qu'on pense être la version finale) et de 1 million de cycles d'écriture (contre 10000 à 1 milliard, un grand écart, pour la version finale) ce qui laisse penser que le prototype ne se comporte peut être pas aussi bien qu'espéré.

Vous noterez enfin que le nombre de cycles d'écritures accordés à la NAND, de 500 à 1000 est particulièrement faible. 3000 cycles serait un peu plus réaliste.

Au-delà de tout ce méli-mélo de marketing, et dans l'absence de vraies données techniques (on ne sait pas par exemple en quel finesse de gravure a été produit le prototype, une des difficultés de la RRAM étant d'utiliser les finesses de gravures les plus faibles) difficile de juger ce qu'a réellement produit cette startup, probablement en recherche de capitaux ou d'un rachat. On suivra avec attention d'éventuelles évolutions sur le sujet assez crucial, dans cette startup ou dans d'autres acteurs du marché.