Intel Core i9-7900X et Core i7-7740X en test : déjà-vus ?

Un Kaby Lake-X... pas très X

Commençons cet article en évoquant le cas le plus simple, celui de Kaby Lake-X. Lorsque l'on regarde les caractéristiques annoncées du Core i7-7740X, on retrouve des choses connues :

- 4 Coeurs/8 threads

- 8 Mo de cache L3

- 2 canaux mémoires DDR4

- 16 lignes PCIe

Pas la peine de faire durer le suspense, c'est effectivement les mêmes caractéristiques que les Kaby Lake classiques. En pratique Kaby Lake-X reprend le die des Kaby Lake... en désactivant l'IGP.

Cela veut dire que l'on s'attend à retrouver exactement le même type de performances que le 7700K, ce qui n'est pas forcément une mauvaise chose, mais aussi les mêmes limites. En effet en réutilisant ce die, Kaby Lake-X ne profite ni des 4 canaux mémoires présents sur les cartes mères (il faudra utiliser uniquement les slots marqués dans le manuel), ni des lignes PCI Express supplémentaires.

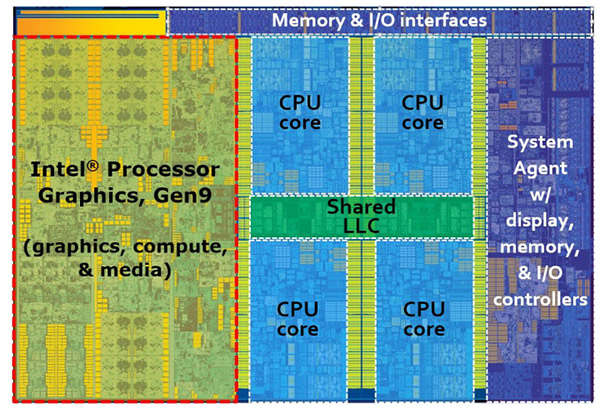

Le die de Skylake/Kaby Lake, la (large) partie gauche en rouge pointillés est désactivée sur le die pour créer Kaby Lake-X

L'idée derrière Kaby Lake-X est simplement de proposer - à moindre coût (pour Intel) - des processeurs 4 coeurs en réutilisant l'existant. Intel profite tout de même du socket plus large pour augmenter le TDP qui monte à 112 watts, et permet d'obtenir une fréquence de base de 4.3 GHz et des coefficients turbo à 4.5 GHz pour le 7740X que nous avons eu entre les mains. A propos de celui-ci, notez que tous ses coefficients turbo sont alignés, ce qui veut dire qu'en charge 4 coeurs, la fréquence restera à 4.5 GHz. Notez enfin que la fréquence Turbo en charge AVX est elle aussi alignée à 4.5 GHz, le TDP large le permettant.

Nous verrons en pratique les performances de cette puce mais nous ne nous attarderons pas plus sur ce qui est, au final, quelque chose d'assez connu. Si vous souhaitez plus de détails sur l'architecture, nous vous renvoyons à notre article sur Skylake premier du nom !

Un Skylake-X très différent !

Celui qui va le plus nous occuper est bien entendu Skylake-X. Et là, nous avons bel et bien droit à un grand nombre de nouveautés. D'abord d'un point de vue des dies, historiquement la plateforme HEDT d'Intel est conçue autour des dies fabriqués pour les Xeon.

Intel produit plusieurs dies pour construire sa gamme, dans les dernières générations on en retrouve trois qui se différencient par le nombre de coeurs qu'ils comportent. En pratique pour cette génération, on retrouve selon nos informations un LCC (Low Core Count) avec jusque 10 coeurs, un MCC (Medium Core Count) allant jusqu'à 18 coeurs, et un HCC (High Core Count) montant à 28. Notez que ces chiffres ne sont pas confirmés par Intel.

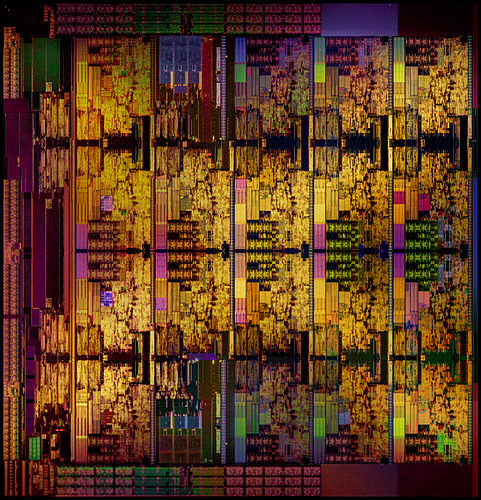

Le constructeur nous a fourni cette photo du die de Skylake-X, sans préciser de quelle version il s'agit. Nous supposons qu'il s'agit du MMC, la version 18 coeurs. On peut noter deux « blocs » légèrement différents en haut et en bas de la deuxième colonne, nous supposons qu'il s'agisse des blocs qui incluent les contrôleurs mémoires qui semblent séparés en deux. Skylake-SP inclut 6 canaux mémoires même si Skylake-X n'en exploite que quatre. Nous supposons que chaque bloc en contient trois.

Jusque Broadwell-E, Intel ne s'est servi que des dies LCC ce qui nous limitait à 10 coeurs dans la gamme. Dans un premier temps, les roadmaps avaient évoqué un modèle 12 coeurs qui laissait penser que le nombre de coeurs du LCC était peut être finalement de 12. Au final, après l'annonce de ThreadRipper, Intel a revu sa copie et rajouté en dernière minute des SKU montant à 18 coeurs, ce qui veut dire en pratique que ces puces exploiteront le die MCC. Et qui explique aussi leur absence aujourd'hui avec un lancement en deux temps !

Le Core i9-7900X (et les modèles inférieurs lancés en juin) exploitent donc tous le die Skylake-SP/Xeon LCC/10 coeurs.

Une architecture assez proche de Skylake, l'AVX-512 en plus

Dans les grandes lignes, Skylake-X/Skylake-SP change assez peu d'un point de vue micro-architecture du Skylake que l'on connaît et dont vous pourrez retrouver les détails dans cet article.

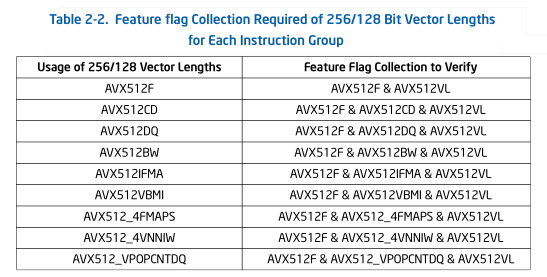

Ce qui change cependant, c'est l'ajout des instructions AVX-512, ou plus exactement d'une partie d'entre elle. Nous avions eu l'occasion d'en parler lorsque le constructeur avait présenté ce jeu d'instructions, il est composé en pratique de multiples jeux d'instructions qui sont disponibles en fonction des modèles, qu'il s'agisse des Xeon Phi ou des Skylake-SP.

Certaines instructions n'apparaitront pas avant Cannonlake

Il y a un socle commun, AVX-512F (Foundation) qui regroupe les instructions de base communes. A celles-ci s'ajoutent des opérations sur la détection de conflit (AVX-512CD) pour tenter d'améliorer la vectorisation automatique.

Xeon Phi a droit à quelques instructions exclusives. Certaines sont liées à son architecture particulières avec des instructions de prefetch dédiées (AVX-512PF), d'autres dédiés aux calculs d'exponentielles et d'inverses (AVX-512ER).

Pour Skylake-SP, on retrouve les extensions BW (instructions sur les entiers 8/16 bits), DQ (entiers/flottants 32/64 bits) et VL (gestion des registres).

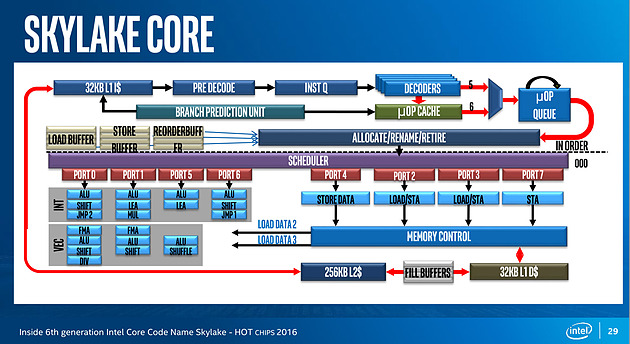

Mais au-delà des instructions, la manière dont elles sont traitées est relativement mystérieuse. L'architecture Skylake contient déjà deux unités (placés sur les ports 0 et 1) capables de traiter les instructions AVX 256 bits. En les cumulant, on peut donc réaliser une instruction AVX 512 bits.

Les unités vectorielles sont regroupées sur les ports d'exécution 0, 1 et 5 dans l'architecture Skylake

Cela n'explique cependant pas la possibilité du 7900X de lancer deux instructions FMA (Fused Multiply Add, par exemple A = A * B + C) par cycle. Cela suppose que d'autres unités AVX soient présentes sur d'autres ports. Des unités FMA supplémentaires pourraient être présentes sur les ports 5 et 6, et désactivées sur les modèles les moins onéreux. Nous attendons une clarification d'Intel également sur ce point.

2 - Kaby Lake-X et Skylake-X, diamétralement opposés

3 - Nouveaux caches et nouvelle... interconnexion ?

4 - Sortie de ring : place au mesh !

5 - X299, Asus Prime X299-A, gamme LGA 2066

6 - Piledriver, Zen, Broadwell-E et Skylake-X à 3 GHz

7 - Impact du SMT/HT

8 - Overclocking en pratique

9 - Consommation, efficacité énergétique

10 - Protocole de test

11 - Compression : 7-Zip et WinRAR

13 - Encodage vidéo : x264 et x265

14 - IA d'échecs : Stockfish et Komodo

15 - Traitement photos : Lightroom et DxO Optics Pro

16 - Rendu 3D : Mental Ray et V-Ray

17 - Jeux 3D : Project Cars et F1 2016

18 - Jeux 3D : Civilization VI et Total War : Warhammer

19 - Jeux 3D : GTA V et Watch Dogs 2

20 - Jeux 3D : Battlefield 1 et The Witcher 3

21 - Indices de performance

22 - Un air de déjà vu...

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 05/04: Pas de MAJ Microcode pour les Gulft...

- [+] 22/12: Samsung grave de la DRAM en ''1ynm'...

- [+] 05/10: Intel Core i7-8700K, Core i5-8600K,...

- [+] 04/10: La DDR4 toujours en hausse, pénurie...

- [+] 14/09: Les prix de la DDR4 ont doublé en u...

- [+] 12/09: Core i7-7820X : Un Skylake-X mieux ...

- [+] 07/09: Les Skylake en fin de vie chez Inte...

- [+] 23/08: Coffee Lake incompatible avec les L...

- [+] 10/08: AMD Threadripper 1950X et 1920X en ...