Reportage : IDF Automne 2007

Publié le 28/09/2007 par Damien Triolet

Tous les 6 mois, Intel convie la presse internationale à l'IDF, grand forum technologique utilisé par le fabricant pour informer et former l'industrie sur les technologies à venir. Cette édition automne 2007 de l'IDF a pris place à San Francisco comme c'était le cas depuis quelques années, l'IDF de février dernier étant l'exception à cette règle puisqu'il s'est tenu en Chine. A l'avenir, Intel devrait alterner Pékin et San Francisco pour les IDFs majeurs, le marché asiatique ayant pris une grande importance.

Par rapport à l'IDF de Pékin, exit les danses locales, la priorité aux membres du parti, les policiers à chaque porte et retour au show à l'américaine. Intel a ainsi perdu moins de temps à se fondre dans la propagande chinoise pour se concentrer sur l'essentiel. Bien entendu, le lieu où s'est tenu l'IDF n'est pas le seul élément qui a entraîné un Intel plus concret, mais le timing en est probablement la composante la plus importante.

A l'approche de la sortie du Penryn et alors que les interrogations sur les processeurs massivement multicores deviennent de plus en plus pressantes, il était logique de s'attendre à plus de concret de la part d'Intel, et nous en avons eu !

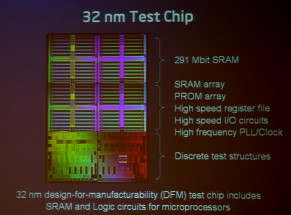

Procédés de fabricationChaque IDF est l'occasion pour Intel de montrer que dans ce domaine ils sont les rois. Celui-ci n'a pas dérogé à la tradition et Intel a présenté pour la première fois un wafer de test qui a bénéficié de la future fabrication en 32 nanomètres. Ce process n'est pas aussi révolutionnaire que ne l'est le 45 nanomètres du fondeur mais permettra malgré tout doubler la densité des transistors, et en d'autres termes de concevoir une puce 2x plus complexe pour une même taille.

Le premier wafer en 32 nanomètres et la puce que l'on y retrouve.

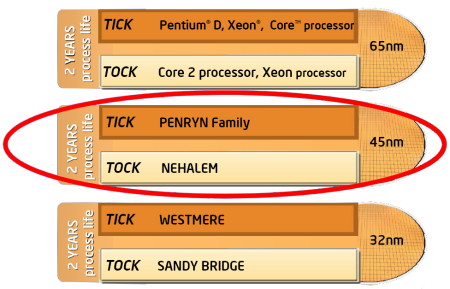

Le premier processeur qui y fera appel sera Westmere, une mise à jour "légère" de l'architecture introduite par Nehalem, qui sera suivie, 1 an plus tard si tout va bien de Sandy Bridge, une nouvelle architecture. Dans l'immédiat, le wafer présenté par Intel consiste en une structure de test classique, c'est-à-dire de la mémoire SRAM et toutes sortes de logiques de test de manière à débuguer et optimiser le process.

Pour rappel, la stratégie d'Intel est d'alterner "Ticks" et "Tocks", d'introduire les nouveaux procédés de fabrication lors des Ticks et les nouvelles architectures lors des Tocks de manière à réduire les risques.

Penryn et SkullTrail

Sommaire

Vos réactions

Contenus relatifs

- [+] 09/12: Guide : Les PC HardWare.fr !

- [+] 14/11: Qualcomm dit non à Broadcom

- [+] 13/11: Thermaltake lance une chaise venti...

- [+] 11/09: Microsoft confirme des problèmes de...

- [+] 30/08: PCI Express 5.0 pour 2019, débit do...

- [+] 01/08: Les taux de retour des composants (...

- [+] 11/07: Le minage consommerait plus que Par...

- [+] 04/07: ASUS XG-C100C, le 10GBASE-T à 120

- [+] 26/06: Computex et le PC : changement et c...

- [+] 24/03: Corsair lance ses PC One avec deux ...