Les contenus liés au tag TLC

Afficher sous forme de : Titre | FluxOCZ : SSD 30% moins cher grâce à la TLC

MLC 3BPC en 25nm chez IMFT

MLC 3 bits / cellule pour Micron/Intel

OCZ : SSD 30% moins cher grâce à la TLC

Storage Review rapporte qu'OCZ a indiqué lors d'une présentation effectuée lors d'une conférence destinée aux investisseurs (Needham 5th Annual HDD & Memory Conference) qu'il allait lancer durant le premier trimestre 2012 des SSD utilisant de la mémoire TLC.

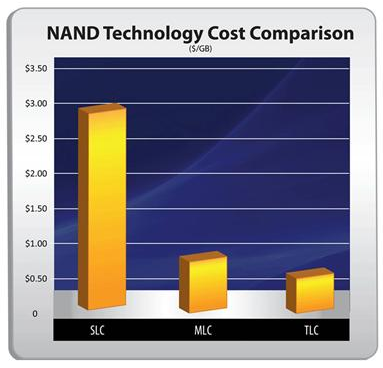

Appelée également MLC 3BPC, la mémoire TLC permet de stocker 3 bits par cellule. Ceci permet d'abaisser nettement le coût de production puisqu'il est question d'une tarification au Go inférieure de 30% à celle de la mémoire MLC. Il faudra attendre le troisième trimestre 2012 pour voir débarquer la TCL sur des SSD OCZ destinés aux entreprises, période à laquelle la technologie Indilinx nDurance 2 combinée à des améliorations sur l'algorithme ECC devrait permettre de doubler la durée de vie des mémoires Flash. Il faut en effet savoir qu'en 2009, Micron parlait d'une endurance divisée par 10 de la TLC par rapport à la MLC.

Le rachat d'Indilinx devrait également continuer de porter ses fruits puisqu'un nouveau contrôleur haute performance pour les SSD clients devrait être lancé en début d'année alors même que l'OCZ Octane n'est pas encore disponible. Côté performances, on sait juste qu'il est question de 70 000 IOPS. Un autre contrôleur destiné aux entreprises cette fois serait prévu pour le second trimestre et serait capable de fournir jusqu'à 100 000 IOPS. Ces deux contrôleurs supporteraient l'interface SATA et PCI-Express.

Ils devraient être à la base de la nouvelle génération de SSD PCI Express d'OCZ qui fourniront jusqu'à 3.2 millions d'IOPS contre 500 000 IOPS pour le Z-Drive R4. Ce nouveau SSD utilisera la norme NVM Express destinée à unifier le support logiciel des SSD PCI Express.

MLC 3BPC en 25nm chez IMFT

Après avoir annoncé une première puce Flash NAND MLC capable de stocker 3 bits par cellule (MLC 3BPC) en octobre 2009, la joint-venture Intel / Micron, IMFT (IM Flash Technologies), revient à la charge avec une nouvelle puce de ce type. La finesse de gravure passe de 34nm à 25nm, et la capacité de 4 à 8 Go.

Ce type de mémoire, également appelé TLC pour triple-level cell, permet de réduire notablement la taille du die pour une capacité identique, puisqu'elle ne mesure que 131mm², contre 167mm² pour une puce en 2 bits par cellule. A titre de comparaison, la puce TLC de 4 Go en 34nm mesurait 126mm².

Cette puce est actuellement en cours d'échantillonnage, alors que la MLC 25nm classique échantillonnée dès février est en production depuis mai. Elle devrait entrer en production d'ici à la fin de l'année. Il faut préciser que pour le moment, ce type de mémoire reste réservé aux clefs USB, aux lecteurs MP3 et aux cartes mémoires.

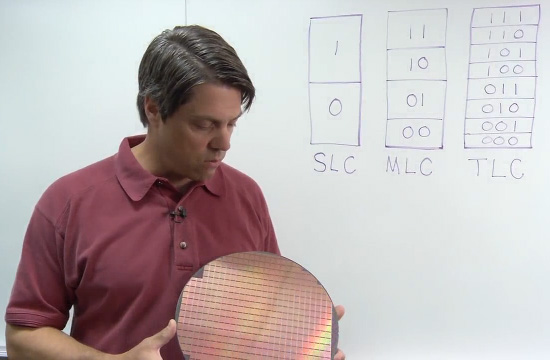

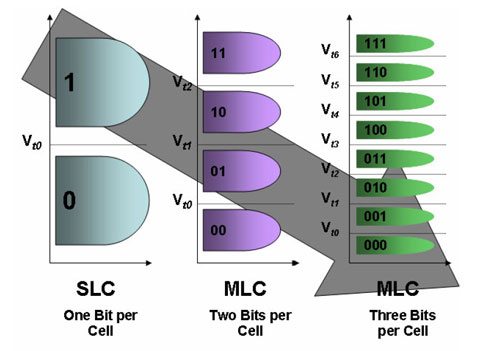

En effet, comme le passage de SLC (1 bit par cellule) à la MLC (2 bits par cellule), le passage de la MLC à la TLC (3 bits par cellule) abaisse les performances en écriture ainsi que l'endurance des cellules. Si aucun chiffre n'a été publié pour cette puce, Micron parlait début 2009 de performances divisées par 2 et d'endurance divisée par 10 ... voilà qui interdit donc leur utilisation au sein de SSD, à moins que la recette miracle d'Anobit fonctionne en pratique !

MLC 3 bits / cellule pour Micron/Intel

![]() La joint-venture d'Intel et Micron dans le domaine de la Flash, IM Flash Technologies (IMFT), vient d'annoncer avoir échantillonné une nouvelle puce de mémoire de 4 Go de Flash NAND MLC stockant 3 bits par cellule (MLC 3BPC). Il s'agit de la première MLC 3 bit par cellule d'IMFT, ce qui lui permet combiné à une gravure en 34nm d'afficher une taille de seulement 126mm². Cette puce est actuellement en cours d'échantillonnage et devrait être produite en volume au 4ème trimestre.

La joint-venture d'Intel et Micron dans le domaine de la Flash, IM Flash Technologies (IMFT), vient d'annoncer avoir échantillonné une nouvelle puce de mémoire de 4 Go de Flash NAND MLC stockant 3 bits par cellule (MLC 3BPC). Il s'agit de la première MLC 3 bit par cellule d'IMFT, ce qui lui permet combiné à une gravure en 34nm d'afficher une taille de seulement 126mm². Cette puce est actuellement en cours d'échantillonnage et devrait être produite en volume au 4ème trimestre.

Si Samsung et Hynix travaille également sur ce type de Flash NAND MLC, seule l'alliance Sandisk et Toshiba avait annoncée de telles puces : une première fois l'an passée sur un process en 56nm, puis une nouvelle fois en février dernier. Il s'agissait alors d'une puce 4 Go fabriquée en 32nm affichant une taille de 113mm², soit moins qu'une puce de 2 Go en MLC classique (2 bits par cellule) gravée en 43nm. Sa production devrait débuter au cours de ce second semestre.

Pour rappel, la mémoire Flash SLC ne gère qu'un bit par cellule, contre 2 pour ma MLC classique utilisée jusqu'alors dans les SSD. En SLC, on doit pouvoir gérer 2 niveaux de tension distincts au sein de la cellule, 4 en MLC 2 bits, et 8 en MLC 3 bits. Cela a un impact négatif sur la vitesse d'écriture mais aussi sur l'endurance de ces dernières : une puce SLC est ainsi 10 fois plus endurante et 3 fois plus rapide qu'une MLC 2 bits. Le passage en 3 bits a un impact négatif sur ces deux facteurs, sans que les constructeurs communiquent exactement sur l'ampleur de cet impact.

Il est toutefois suffisant pour que Micron indique que sa nouvelle mémoire est destinée aux clés USB et aux cartes mémoires, mais pas pour les SSD. A ce propos, il y'a 6 mois un billet au sujet de ce type de MLC avait été posté sur le Blog officiel de Micron . L'auteur indiquait alors que Micron développait une telle puce mais que pour le moment la technologie n'était pas vraiment satisfaisante, avec des performances en écriture divisées par 2 en écriture et une endurance 10 fois moindre, ce qui la porterait à 1 000 cycles d'écritures ! De fait, l'auteur concluait que pour le moment le meilleur moyen d'abaisser les coûts tout en conservant un bon niveau de performance et de fiabilité était de réduire la finesse de gravure sur les actuels MLC/SLC ... malheureusement et Micron l'admet d'ailleurs dans une vidéo postée sur ce même blog, cela va devenir de plus en plus difficile d'abaisser la finesse de gravure. Ainsi, si le rythme se ralenti, le seul moyen d'augmenter la densité sera alors de passer à la MLC 3BPC, puis à la MLC 4BPC mise au point par Sandisk / Toshiba ...