Les contenus liés aux tags Intel et IDF

Afficher sous forme de : Titre | FluxIDF: MAJ: Sandy Bridge-E, DX79SI, RTS2011LC

IDF: La grand-messe Intel ouvre ses portes

Sandy Bridge se dévoile !

IDF: Ivy Bridge pour Ultrabook en 10W

Publié le 11/09/2012 à 22:46 par Guillaume Louel

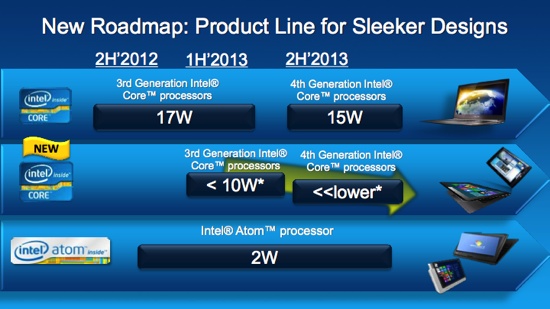

Au milieu d'une présentation sur les Ultrabooks, Intel a révélé une nouvelle déclinaison de processeurs Ivy Bridge avec un TDP inférieur à dix watts.

Prévu pour la première moitié de l'année 2013, ces Ultrabooks devraient se limiter à quelques modèles, Intel nous ayant indiqué que ces puces double coeurs ne seraient disponibles qu'en petites quantités. Une offre qui devrait s'étendre avec Haswell ou Intel lancera en simultanée les versions 15W (au lieu de 17) et moins de 10 watts pour la seconde moitié de l'année.

IDF: Objectif 2W pour 100 Gflops en 2018

Publié le 15/09/2011 à 22:08 par Damien Triolet

Bien que très énergisé par le béret de Mooly Eden, c'est bien d'une réduction drastique de la consommation dont nous a parlé Justin Rattner, Chief Technology Officer chez Intel, lors de la keynote de clôture de l'IDF, traditionnellement tournée vers le futur.

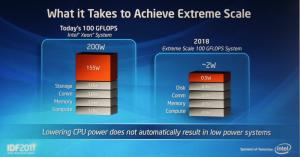

Pour pouvoir assurer l'évolution de ses performances et de ses produits, Intel s'est ainsi fixé plusieurs objectifs à long terme : pouvoir proposer des systèmes d'une puissance de 100 Gflops dans une enveloppe thermique de 2W d'ici à 2018, contre 200W pour un système Xeon équivalent actuel, et des supercalculateurs capables d'atteindre l'exaflops sans dépasser les 20 megawatts.

Pour atteindre ces objectifs, l'évolution des procédés de fabrication restera bien entendu primordiale, tout comme celle de l'architecture des CPUs. Intel indique cependant qu'il faudra s'attaquer au problème de la consommation sur de nombreux fronts : protocoles de communication, stockage, mémoire

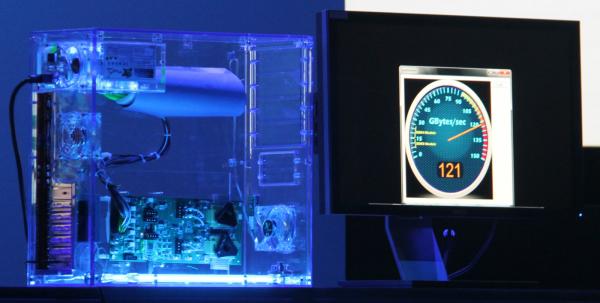

Intel a ainsi présenté un prototype de l'Hybrid Memory Cube développé en collaboration avec Micron et qui consiste à profiter du die stacking pour augmenter la densité de la mémoire mais également son débit. Une concentration qui permet d'améliorer le rendement énergétique d'un facteur 7 selon Intel.

Le prototype présenté consiste en une première couche qui contient la logique (un CPU simplifié probablement) sur laquelle sont empilées 4 couches de DRAM de 1 Gbits, soit 512 Mo au total. Un ensemble qui peut fournir une bande passante record de 128 Go/s, largement supérieure à ce dont sont capables les modules mémoire actuels. A terme, le but sera bien entendu d'empiler ainsi la mémoire sur les CPUs manycores pour profiter d'un accès plus rapide, mais également nettement moins consommateur d'énergie.

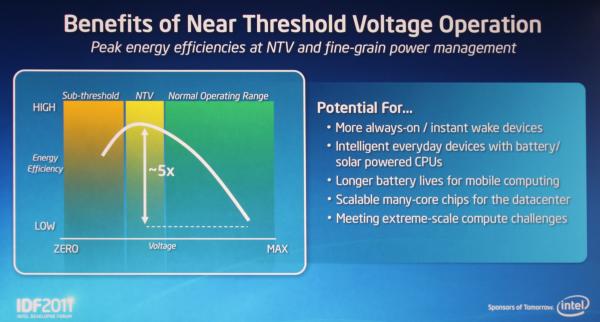

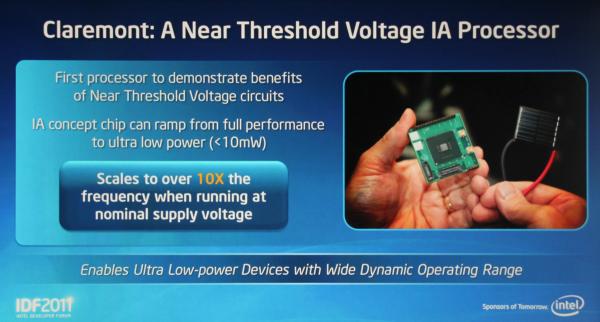

Un autre point sur lequel Intel travaille consiste à pouvoir abaisser la tension du CPU jusqu'au seuil du transistor. Habituellement, la tension est nettement plus importante, dans le but d'obtenir des performances élevées tant au niveau des transistors que de la transmission du signal. Si cette nouvelle approche pourrait permettre de laisser éveillés en permanence certains processeurs grâce à une plage de fonctionnement étendue, pouvoir se rapprocher des limites inverses du transistor pourrait paradoxalement favoriser la mise en place de systèmes très performants.

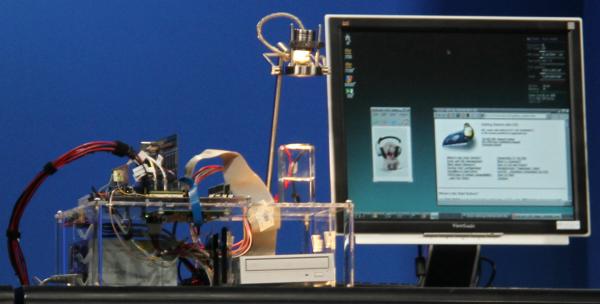

Pour travailler sur ce projet, Intel a mis au point un prototype de CPU, nom de code Claremont, basé sur un core Pentium qui peut abaisser sa consommation jusqu'à moins de 10 mW, de quoi pouvoir être alimenté par une petite cellule photovoltaïque. Certes dans ce mode la fréquence et donc les performances du CPU sont fortement réduites, mais le tout reste suffisant pour qu'un système Windows reste fonctionnel.

Ce CPU était en démonstration lors de différentes keynotes durant l'IDF, accompagné d'une ancienne carte-mère Pentium qui était par contre alimentée d'une manière classique. Pour faire passer la totalité de la plateforme à un niveau de consommation énergétique aussi faible, il y a encore du travail pour les ingénieurs d'Intel !

IDF: SSD 710 Series, Cherryville, Hawley Creek

Publié le 15/09/2011 à 09:13 par Damien Triolet

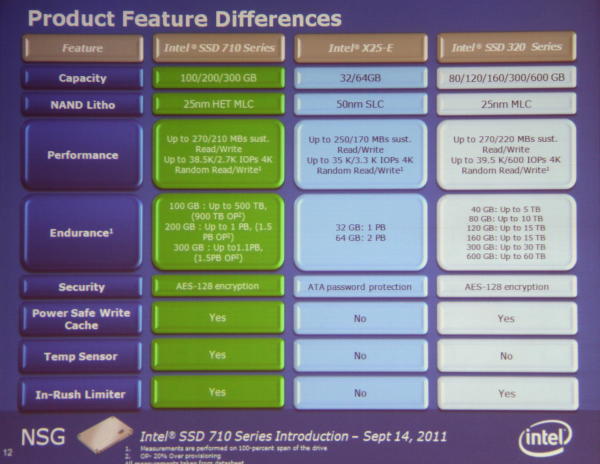

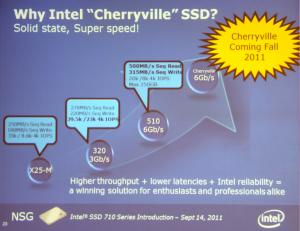

Intel profite de l'IDF pour lancer une nouvelle série de SSDs dédiée principalement aux data centers, les 710 Series. Grossièrement il s'agit d'une variante des 320 Series destinée à remplacer la famille X25-E. Par rapport aux précédentes informations, les taux de transfert n'ont pas évolués, mais le débit d'IOPS est en légère hausse avec 38500 IOPS en lectures aléatoires sur des blocs de 4k. En écritures aléatoires, il varie entre 2000 et 2500 IOPS et pourra monter jusqu'à 2400 à 4000 IOPS avec 20% d'overprovisionning.

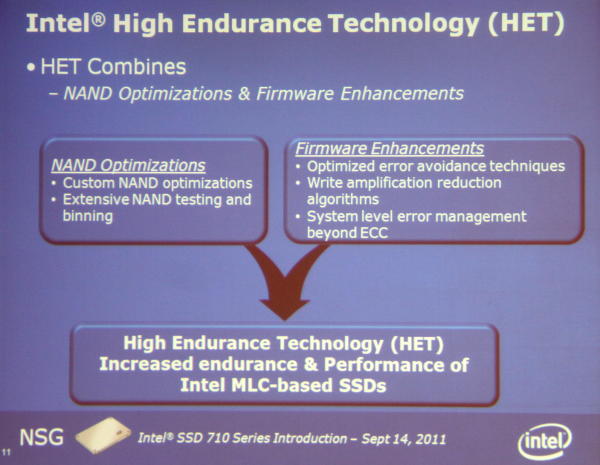

Si ces SSDs proposent une endurance très élevées, ils sont pourtant basés sur de la mémoire MLC 25nm. Ce miracle serait obtenu grâce à la HET (High Endurance Technology) qui repose sur une optimisation de la NAND et une sélection des meilleurs échantillons, ainsi que sur diverses améliorations apportées à travers le firmware. Au final, l'endurance se rapproche de celles des X25-E (1 PB pour la version 32 Go et 2 PB pour la version 64 Go), avec respectivement 0.5 PB, 1PB et 1.1 PB pour les versions 100, 200 et 300 Go des 710 Series. Des chiffres qui pourront également grimper à 0.9 PB, 1.5 PB et 1.5 PB avec 20 d'overprovisionning.

Malgré l'emploi d'une mémoire MLC, certes retravaillée, la tarification est relativement élevée pour ces SSDs qui seront disponibles sous peu pour 649$, 1289$ et 1929$ pour les versions 100, 200 et 300 Go. Ils sont cependant annoncés avec une garantie classique de 3 ans, contre 5 ans pour les 320 Series.

D'ici quelques semaines, Intel devrait dévoiler la série SATA III en 25nm, Cheryville ou 520 Series, et un peu plus tard Hawley Creek, la seconde génération de cache pour la Smart Response Technology. Elle proposera toujours une capacité de 20 Go mais utilisera de la NAND SLC 25nm.

IDF: Haswell fonctionnel, en démo

Publié le 15/09/2011 à 08:16 par Damien Triolet

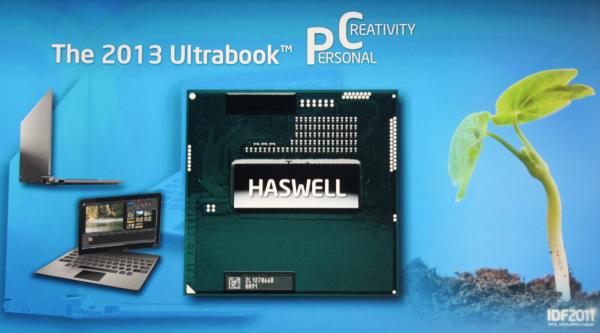

Après Ivy Bridge, Mooly Eden a voulu rassurer par rapport à l'avancement de la mise au point de son successeur, Haswell. Nous avons ainsi pu en apercevoir un prototype sur son packaging, laissant entrevoir un die au format très allongé, d'une taille assez proche de celui d'Ivy Bridge.

Intel a insisté une fois de plus sur le fait qu'Haswell marquerait le point culminant de sa stratégie Ultrabook, grâce à un rendement énergétique très élevé, sans toutefois donner le moindre détail technique sur son architecture ni sur ses déclinaisons plus véloces.

Notez enfin que ce CPU prévu pour 2013 est déjà fonctionnel dans les labos du fondeur, desquels un exemplaire s'était échappé pour nous en apporter la preuve à l'IDF :

IDF: +20% de transistors, 16 EU pour Ivy Bridge

Publié le 15/09/2011 à 08:00 par Damien Triolet

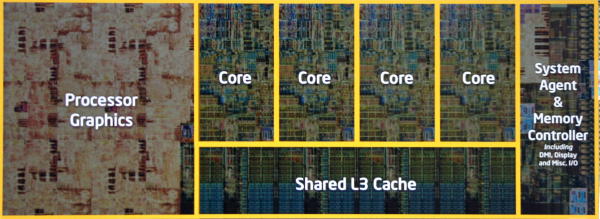

Lors de sa keynote, Mooly Eden, Vice-Président du PC Client Group, a dévoilé quelques petits détails supplémentaires sur Ivy Bridge. Il intègrera ainsi 1.4 milliards de transistors, soit 40% de plus que Sandy Bridge (995 millions) dont une bonne partie servira à mettre à jour le GPU intégré, qui représente la plus grosse évolution liée à cette architecture. Nous pouvons d'ailleurs nous demander si Intel ne va pas mettre à jour son GPU lors des "tick", avec le passage aux nouveaux procédés de fabrication, tout comme les cores CPU sont mis à jour lors des "tock".

Le die d'Ivy Bridge est encore plus allongé que celui de Sandy Bridge, ce qui s'explique par l'intégration du contrôleur mémoire dans le bloc System Agent ainsi que par la surface plus importante occupée par le GPU. Alors qu'elle représente un peu moins de 20% de la surface totale dans Sandy Bridge, cette photo du die indique qu'il s'agira de plus de 30% pour Ivy Bridge.

Comme nous l'expliquions précédemment, ce GPU va gagner en modularité et avec l'intégration des unités de texturing dans les blocs d'unités de calcul (EU) il sera également possible de faire varier leur nombre suivant les déclinaisons. Si Intel se refuse à rentrer dans plus de détails, les bruits de couloir font état de la présence de 16 EU dans Ivy Bridge, contre 12 dans Sandy Bridge. Par ailleurs, nous pouvons observer sur la partie GPU de la photo du die 4 blocs identiques d'une part et 2 autres identiques d'autre part. Il se pourrait donc qu'Ivy Bridge repose sur des blocs contenant 2x 4 EU ainsi que 4 unités de texturing. En plus des nombreuses optimisations (notamment le débit de FMA doublé par EU), Ivy Bridge disposerait ainsi de 33% d'EU de plus et du double d'unités de texturing, de quoi égaler Llano sur les performances graphiques.

Notez cependant que Mooly Eden a étrangement insisté sur le fait que la représentation du die sur cette photo n'est pas correcte. Pourtant elle correspond bien au die du wafer d'Ivy Bridge présenté il y a quelques mois, il ne s'agit donc pas d'un montage. Brouillage de piste ? Intel aurait-il changé ses plans et un die revu serait-il au programme, par exemple avec un GPU encore plus costaud pour affronter Trinity ?

Mise à jour du 16/09

Intel a précisé à Anandtech que la comparaison au niveau du nombre de transistors entre Ivy Bridge et Sandy Bridge n'était pas valide car les deux chiffres ont été obtenus à des étapes différentes du design. Pris à une étape plus avancée, lors de la création du layout, le nombre de transistors de Sandy Bridge passe de 995 millions à 1.16 milliards. Avec 1.4 milliards de transistors, Ivy Bridge repose donc sur 20% de transistors en plus et non 40%.

Reste à savoir pourquoi Intel a décidé de changer de méthode de comptage pour le nombre de transistors officiel et si l'impact entre ces différentes méthodes est similaire pour Ivy Bridge et Sandy Bridge.