Les contenus liés aux tags Intel et IDF

Afficher sous forme de : Titre | FluxIDF: Ivy Bridge pour Ultrabook en 10W

IDF: Objectif 2W pour 100 Gflops en 2018

IDF: SSD 710 Series, Cherryville, Hawley Creek

IDF: Haswell fonctionnel, en démo

IDF: +20% de transistors, 16 EU pour Ivy Bridge

Focus : IDF: Interview de Mark Bohr d'Intel

Notre couverture de l'Intel Developer Forum 2012 a été l'occasion pour nous de rencontrer Mark Bohr. Tenant les titres de Senior Fellow et Directeur des Architectures Processeur et de leur Intégration chez Intel, Mr. Bohr - qui a rejoint Intel en 1978 - est aujourd'hui responsable de l'évaluation des différentes technologies utilisées par le constructeur dans ses procédés de photolithographie.

Une des tâches qui l'occupe actuellement est le choix des technologies qui feront partie du procédé de...

[+] Lire la suite

IDF: Justin Rattner, WiGig et Spring Meadow

Outre le prototype d'Atom intégrant une radio composée principalement de transistors numériques, la keynote de fermeture de l'IDF de Justin Rattner, actuel CTO d'Intel, à été l'occasion de revenir sur plusieurs technologies à venir. Une conférence qui contenait de multiples piques, toutes aussi appuyées et répétées qu'inutiles envers l'ancien CTO d'Intel, Pat Gelsinger qui avait fondé l'IDF à la fin des années 90. Protégé d'Andy Grove, Gelsinger avait quitté Intel en 2009 pour devenir président d'EMC (il a été nommé récemment CEO de VMware).

Justin Rattner est entré sur scène avec des oreilles de chat bougeant en fonction de l'activité de son cerveau...

Un standard développé par un comité indépendant de la WiFi Alliance, la Wireless Gigabit Alliance, qui regroupe la majorité des grands noms de l'industrie (AMD, Broadcom, Cisco, Dell, Intel, Marvell, Microsoft, Nokia, Nvidia et Qualcomm entre autres) avec pour but de proposer des taux de transferts de plusieurs gigabits par secondes sans fil sur des distances plus courtes. En pratique la spécification reprend les bases du WiFi 802.11n et ses deux gammes de fréquences (2.4 GHz et 5 GHz) avec lesquelles le standard est compatible, tout en ajoutant une troisième gamme de fréquence à 60 GHz.

La démonstration tentée sur scène était composée de deux écrans DisplayPort à distance ainsi qu'un disque dur connectés sur un prototype de station d'accueil WiGig. Un Ultrabook se connectait alors à la station, pilotant les écrans et effectuant la lecture d'une vidéo HD à distance (WiGig sera compatible HDCP). Une démonstration qui aura mis plusieurs minutes à fonctionner, malgré la faible distance entre les périphériques (moins de deux mètres). La bande passante maximale attendue par la première version du standard est de 7 Gb/s, même si l'utilisation de la bande de fréquence de 60 GHz devrait limiter la portée à 10 mètres environ, sans cloisons (au-delà les fréquences WiFi N classiques prendraient le relais avec des débits plus limités). La WiGig alliance indique cependant travailler sur des techniques avancées de filtrage spatial pour permettre des transferts au-delà de 10 mètres. De manière surprenante, Intel n'aura pas annoncé l'arrivée de produits basés sur ce standard. L'arrivée commerciale du WiGig semblant encore lointaine.

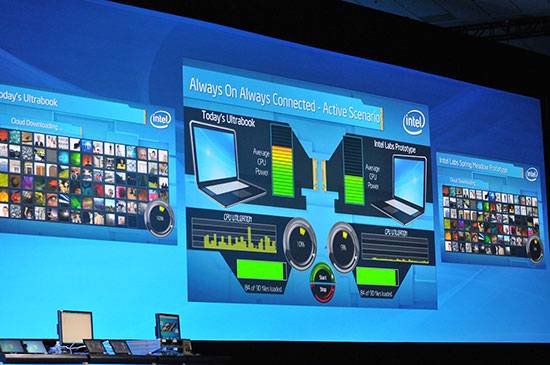

Intel aura présenté de manière un peu plus concrète une évolution de sa technologie Smart Connect. Le principe de Smart Connect est pour rappel de réveiller périodiquement (toutes les 60 minutes en journée par exemple, une durée qui peut être réduite jusqu'à 5 minutes et toutes les deux heures la nuit) un Ultrabook en veille, dans un état basse consommation, afin qu'il aille récupérer les emails via WiFi avant de s'éteindre de nouveau. Pour la prochaine version de cette technologie, Intel indique avoir ajouté une technologie de filtrage de paquets directement à l'intérieur de son contrôleur réseau. L'idée du filtrage est de limiter le type de paquets reçus à traiter.

Smart Connect en pratique réveille la machine et toutes les applications qui, si un WiFi connu est disponible, vont alors se connecter. On imagine même si cela n'a pas été expressément précisé qu'Intel bloque dans son contrôleur réseau un certain nombre de ports et de type de trafic (par exemple des téléchargements) afin de donner la priorité au contenu important (mails, etc). On ne sait pas si l'on pourra choisir le type de trafic filtré dans l'application Smart Connect du constructeur. Une démonstration un peu floue et sur laquelle Intel n'a pas voulu communiquer de date, laissant douter du fait qu'elle soit disponible pour le lancement de Haswell.

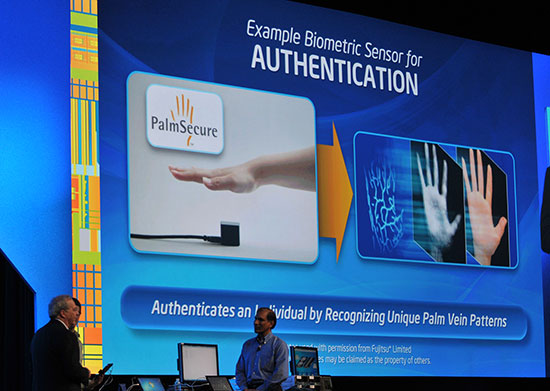

La biométrie est un sujet récurrent dans les conférences de Justin Rattner, et c'est cette fois ci PalmSecure, une technologie de Fujitsu déjà présentée au CES qui a été montrée. Plutôt que d'utiliser une reconnaissance d'empreinte digitale, PalmSecure se base sur une cartographie des veines de la main, plus complexe à falsifier. La démonstration fonctionnait sur une tablette avec un logiciel qui servait d'interface locale d'authentification pour différents services (à l'image des gestionnaires de mots de passes). La particularité de l'implémentation tenait dans le fait que les accéléromètres de la tablette étaient utilisés pour détecter le fait qu'elle soit posée afin de bloquer la session Windows.

IDF: Intel évoque Clover Trail et Clover Trail+

Le lancement de Windows 8 en octobre prochain sera l'occasion du lancement de plusieurs formats de tablettes. Microsoft lui même avait annoncé deux formats distincts avec Surface (voir notre actualité), d'un côté des tablettes ARM, plus fines, fonctionnant sous Windows RT (une version un peu plus bridée de l'OS) et de l'autre des tablettes x86, un peu plus épaisses et reprenant les processeurs des Ultrabooks.

Intel ne devrait pas en rester là puisque le constructeur va en prime mettre en avant ses processeurs Atom afin de proposer également des tablettes comparables physiquement aux modèles ARM, mais qui tourneront sous Windows 8.

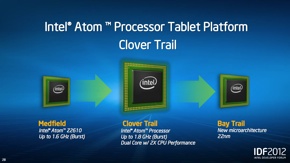

Selon ces slides montrés lors de l'IDF, Intel proposera un nouveau SoC baptisé Clover Trail. Basé sur le SoC Atom Medfield qu'Intel met en avant pour les smartphones, Clover Trail serait un Atom double coeur (Medfield ne dispose que d'un coeur avec Hyperthreading) dont la fréquence peut atteindre 1.8 GHz. La partie graphique n'est pas évoquée, Medfield utilisant pour rappel un PowerVR SGX 543.

Lenovo a déjà annoncé une Thinkpad2 basée sur Clover Trail

Une déclinaison Smartphone de Clover Trail semble également prévue sous le nom de code Clover Trail+. L'Atom Z2580 serait lui aussi basé sur un Atom double coeur est il est annoncé ici également un doublement des performances graphiques par rapport à Medfield. Dans les deux cas, l'arrivée précise de ces nouveaux SoC sur le marché n'est pas précisée même si l'on imagine avec le modèle tablette que le constructeur vise la sortie de Windows 8. La génération suivante, baptisée Bay Trail reposera pour rappel sur une nouvelle architecture OoO comme nous l'avions vu précédemment, en plus d'être fabriqué en 22nm.

IDF: Haswell : retour sur la partie graphique

En plus de ce que nous indiquions ce matin, nous avons glanés quelques détails supplémentaires sur la partie graphique intégrée à Haswell

D'abord au niveau du support des écrans. A l'image d'Ivy Bridge, trois framebuffers distincts sont gérés dans la puce pour piloter jusque trois écrans. Une possibilité qui réclame que deux ports DisplayPort soient présents sur la carte mère (voir notre test d'Ivy Bridge pour plus de détails) et qui n'est en pratique pas exploitée.

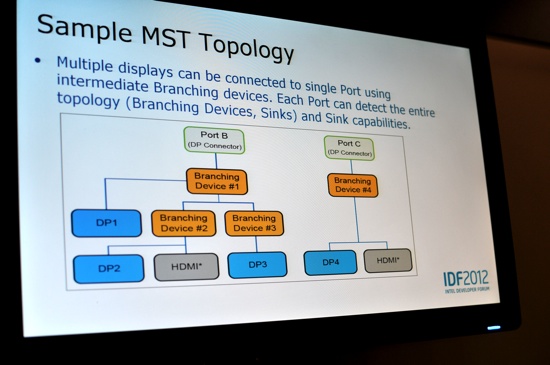

Haswell améliorera un peu la situation en supportant officiellement les hubs Display Port (MST pour Multi Stream Transport). Une démonstration d'Intel nous a montré l'utilisation de trois écrans simultanés connectés via trois hubs 2 ports chainés les uns aux autres (en pratique deux hubs 2 ports auraient suffit, Intel mettait simplement en avant pour sa démonstration sa gestion du chainage).

Sur ce schéma, on peut voir l'exemple d'une carte mère ou six écrans (4 DP et 2 HDMI)sont connectés sur deux ports Display Port. Attention cependant : s'il est possible de connecter plus de trois écrans, en pratique seuls trois images distinctes peuvent être générées côté GPU. Intel met simplement en avant avec ce schéma la possibilité d'effectuer du mirroring. Intel n'est pas le premier a gérer le support des hubs MST, AMD par exemple le propose depuis les HD 6000. Seul problème, ces hubs sont encore aujourd'hui introuvables. Rayon d'espoir sur ce point : selon notre interlocutrice, le modèle utilisé (basé sur un contrôleur ST Micro) pour la démonstration sera réellement disponible avant la fin du mois !

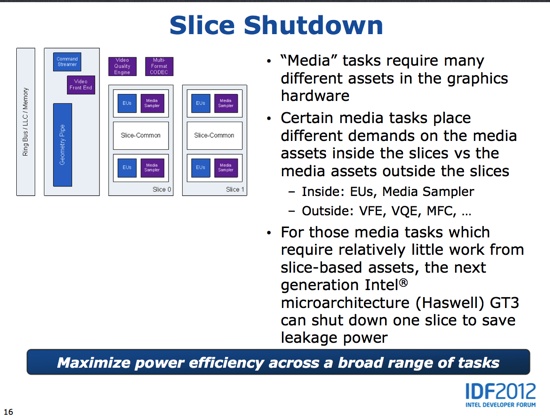

Terminons avec quelques détails supplémentaires sur les coeurs graphiques proprement dits. D'abord, une des particularités de la version GT3 de l'IGP est qu'elle dispose de deux partitions indépendantes, Intel les appelle «slice». L'intérêt de ce découpage est que dans le cas d'une charge graphique «légère», Haswell peut désactiver complètement l'un de ses slices pour limiter la consommation, une fonctionnalité qui a été ajoutée dixit le présentateur de la conférence pour les Ultrabook. Une confirmation du fait que l'on devrait retrouver ce GT3 dans des SKUs mobiles !

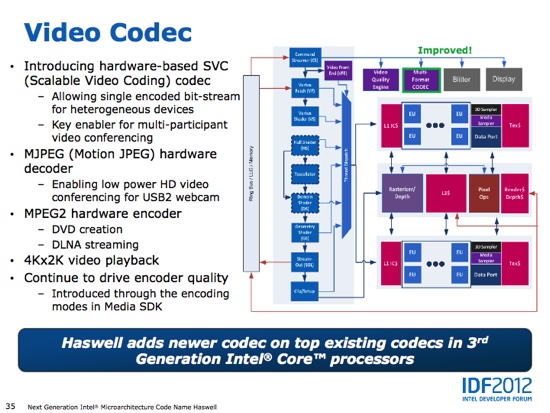

Enfin, Intel a ajouté quelques détails sur la partie codec de son IGP. On trouve quelques ajouts qui visent principalement l'accélération de la vidéo conférence. D'abord, l'encodeur H.264/AVC (connu sous le terme marketing QuickSync, voir ici) gère désormais la version «Scalable» du format. Il s'agit d'une extension du H.264 adaptée à la transmission de vidéo en ligne qui rajoute une notion de robustesse, le format peut en effet continuer a décoder une version dégradée de la vidéo en cas de fluctuation de la bande passante par exemple. Deux autres formats sont également gérés, le MPEG2 en encodage et le MJPEG en décodage. Dans les trois cas, le but est le même : ces formats serviront à accélérer des applications de type vidéo conférence (avec la possibilité d'améliorer le streaming également dans le cas du SVC).

IDF: Haswell : premiers détails !

Si la Keynote n'a pas été l'occasion de grandes annonces, les sessions techniques de l'IDF sont toujours beaucoup plus riches en détails ! Une première session de la matinée était dédiée à l'architecture d'Haswell, celle qui prendra place dans les remplaçants d'Ivy Bridge.

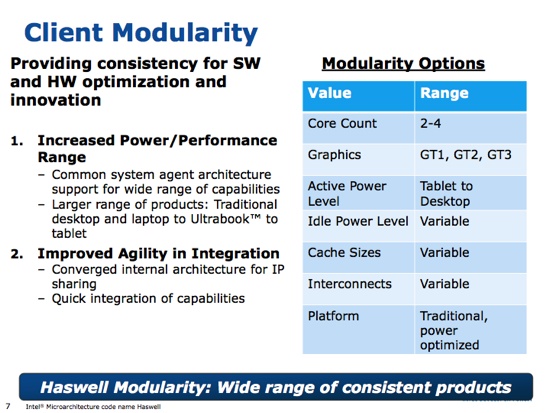

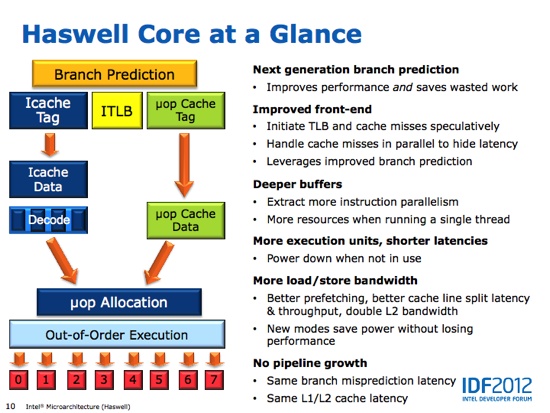

D'abord dans les grandes lignes, trois versions seront disponibles. Outre la version desktop et mobile, une version spécifique deux coeurs dédiée aux ultrabook sera également au programme. Différence principale avec la version mobile, elle intégrera (au sein du package) directement le chipset, pour un TDP de 15 watts (Intel n'ayant pas précisé si la version sous les 10 watts dont nous parlions précédemment intègrera également le chipset).

La modularité est le maitre mot utilisé par Intel pour Haswell. Outre le nombre de cores qui variera de deux à quatre, on trouvera trois coeurs graphiques distincts.

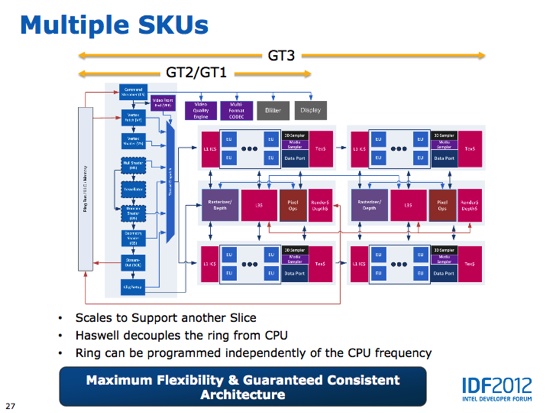

La nouveauté vient de l'arrivée de GT3, une troisième option graphique qui double ce qu'Intel appelle le slice. On trouvera donc deux blocs de rasterisation, de Z, de Stencil et de blending en plus des unités de calculs doublées. La partie en amont du GPU a été redimensionnée en fonction pour pouvoir gérer ces blocs supplémentaires. La présence du bloc mémoire additionnel a été éludée dans la présentation.

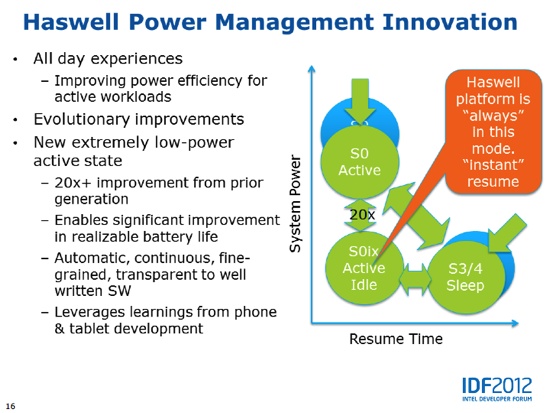

Du côté de la gestion de l'énergie, la plateforme gère les états SOix (1, 2 et 3) notamment supportés par Microsoft pour Windows 8 sous le nom de Connected Standby . L'intérêt de ces états est de proposer une plus grande finesse dans la gestion de l'économie d'énergie avec la possibilité de sortir de ces modes de veille avancés en 100 micro secondes, 3 milli secondes et 300 milli secondes (pour SOi 1, 2 et 3 respectivement).

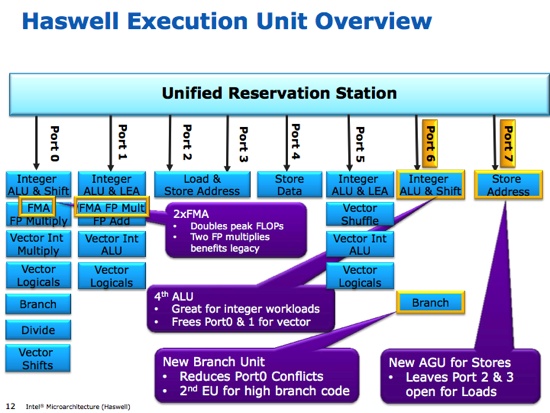

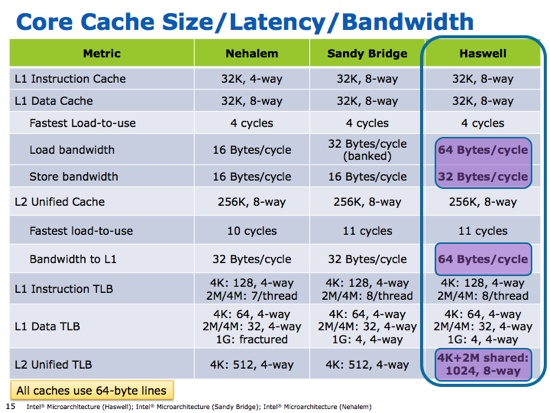

Comme nous l'indiquions précédemment, Intel a effectué quelques changements dans son architecture CPU. D'abord du côté des instructions par cycles, deux ports sont ajoutés ce qui permet au moteur OoO de traiter jusque 8 instructions par cycle. Deux ports peuvent être utilisés pour les instructions FMA (A=A+BxC en virgule flottante), doublant leur capacité théorique de traitement.

Les modifications ne s'arrêtent pas là avec des changements (non documentés) sur l'unité de prédiction de branchements et une augmentation de la taille de multiples buffers.

Intel est revenu sans plus de précisions sur le support de la mémoire transactionnelle, avec TSX. Nous avions pour rappel parlé de cette technologie en détails dans cet article. D'autres détails devraient être dévoilés dans des sessions techniques sur lesquelles nous reviendrons bientôt.

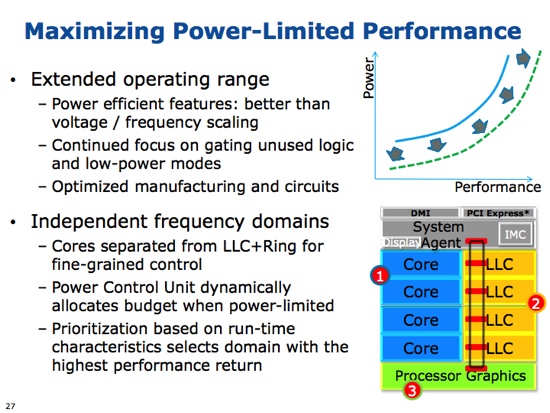

Dernier point notable au niveau de la PCU, Intel indique que le ring bus et la mémoire cache font désormais partie d'un plan d'alimentation complètement séparé.

Des premiers détails plutôt alléchants pour ces puces. Leur arrivée étant toujours prévue pour le second trimestre 2013.