Les contenus liés aux tags Intel et IDF

Afficher sous forme de : Titre | Flux Les 3 contenus de cette page

IDF: MAJ: Sandy Bridge-E, DX79SI, RTS2011LC

IDF: La grand-messe Intel ouvre ses portes

Sandy Bridge se dévoile !

IDF: MAJ: Sandy Bridge-E, DX79SI, RTS2011LC

Publié le 14/09/2011 à 04:29 par Damien Triolet

Alors qu'Intel semble plutôt discret sur la plateforme Sandy Bridge-E dont la sortie se rapproche, ce futur CPU haut de gamme est malgré tout en démonstration dans l'Extreme Zone de l'IDF, accompagné de la carte-mère de référence DX79SI ainsi que du système de refroidissement dédié au(x) modèle(s) Extreme Edition, le système de watercooling RTS2011LC.

La DX79SI est une carte-mère haut de gamme destinée à la plateforme socket 2011. Elle propose ainsi 3 ports PCI Express au format 16x (dont un câblé en 8x) et 2 slots mémoire par canal, soit 8 au total. Pour le reste sa connectique est par contre plutôt limitée, notamment au niveau des ports SATA (4 seulement), mais il est possible que cela change sur la version commerciale de la carte.

Les versions Extreme Edition du Sandy Bridge-E seront livrées avec un système de watercooling tout en un fabriqué par Asetek et dérivé du 570LC.

L'Extreme Tuning Utility sera mis à jour pour la sortie du Sandy Bridge-E, Intel en profitant pour faire la démonstration d'un overclocking à 4.72 GHz, certes loin du récent record d'AMD, mais obtenu avec le kit tel qu'il sera commercialisé et sur un système réellement utilisable.

Mise à jour :

Intel nous a précisé qu'en réalité aucun système de refroidissement ne sera livré avec aucun des Sandy Bridge-E, le fabricant estimant que dans tous les cas les utilisateurs préféreraient se tourner vers un modèle différent de celui de référence.

Le kit de watercooling tout en un RTS2011LC sera cependant commercialisé à part par Intel.

IDF: La grand-messe Intel ouvre ses portes

Publié le 13/09/2011 à 22:48 par Damien Triolet

Comme chaque année, le mois de septembre est l'occasion de se rendre à l'Intel Developer Forum de San Francisco, évènement au cours duquel Intel fait le point sur ses plans autant à court terme qu'à long terme. De quoi en apprendre en peu plus, tout du moins nous l'espérons, sur les Sandy Bridge E et leur plateforme, sur Ivy Bridge et le 22 nanomètre, sur Cedar Trail et les tablettes ou encore sur l'architecture MIC et les successeurs de Larrabee.

La keynote d'ouverture de Paul Otellini, le CEO et Président d'Intel, est cependant restée inhabituellement sobre et vague en annonces, évitant notamment toute référence aux Sandy Bridge E dont la finalisation de la plateforme semblerait poser quelques problèmes de dernière minute.

Paul Otellini a principalement rappelé l'importance de proposer aux utilisateurs un environnement consistant dans lequel pourront circuler de manière transparente les informations entre les différents périphériques connectés qui sont en train de se multiplier à vive allure, ce qui inclut bien entendu la garantie d'une sécurisation suffisante. Le rachat de McAfee commencera d'ailleurs très bientôt à porter ses fruits à ce niveau avec l'arrivée de DeepSAFE tout d'abord réservée au monde professionnel et qui proposera, en combinaison avec les CPU de la marque, une sécurité renforcée contre les rootkits. Une première étape avant la généralisation de l'intégration plus poussée entre le CPU et le logiciel pour renforcer la sécurité sur toutes les plateformes proposées par le fondeur.

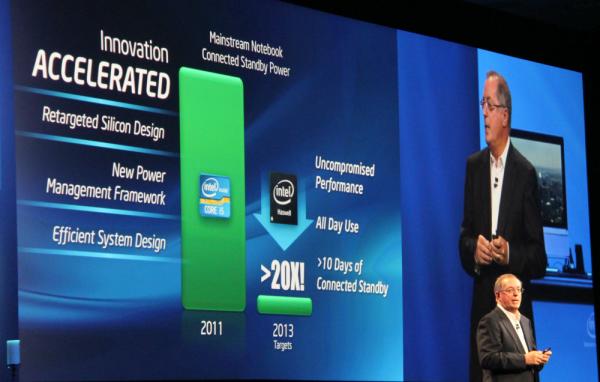

Pour faciliter une connectivité permanente, Paul Otellini indique se reposer sur le travail acharné entrepris par Intel depuis plusieurs années autour de la réduction de la consommation de la plateforme. En plus de faire baisser l'enveloppe thermique en charge de 50%, la plateforme Ultrabook de 2013, bâtie autour du CPU Haswell fabriqué en 22nm, devrait ainsi permettre une réduction de plus de 20X de la consommation en mode veille connectée, de quoi porter l'autonomie dans ce mode à plus de 10 jours ! Pour rappel, ce mode veille connectée permet par exemple d'avoir un accès instantané à ses emails lors du réveil du PC ainsi qu'à toutes autres données qui émergeront des nouveaux modèles d'utilisation ainsi rendus possibles (météo, news, état de remplissage du frigo ).

Paul Otellini et Andy Rubin, Senior Vice President of Mobile, Google.

Enfin, pour conclure ce premier keynote, Paul Otellini a annoncé un partenariat important, attendu depuis longtemps : la coopération renforcée avec Google afin d'optimiser la plateforme Android pour la famille Atom. Intel s'assure ainsi l'accès à un écosystème en pleine explosion et Google à une plateforme x86 qui est loin d'avoir dit ses derniers mots. Pour renforcer l'aspect concret de cette annonce, Paul Otellini a également brièvement montré un smartphone basé sur le SoC Atom Medfield et qui fera office de plateforme de développement pour Android 2.3.

Sandy Bridge se dévoile !

Publié le 14/04/2010 à 11:27 par Marc Prieur

Lors de lIDF qui se déroule actuellement à Pekin, Intel a montré pour la première fois un wafer 32nm de processeurs utilisant la nouvelle architecture "Sandy Bridge". Le fondeur a par la même occasion confirmé que la production de ce processeur démarrerait au 4è trimestre 2010, ce qui laisse penser à un lancement commercial en toute fin dannée voir en début dannée 2011.

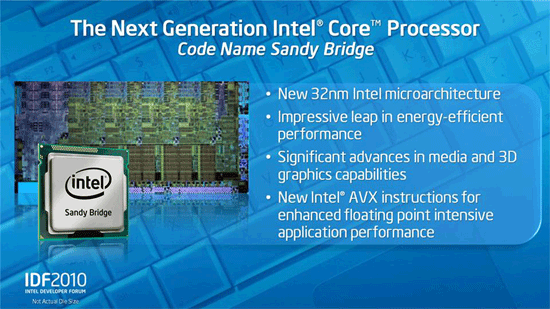

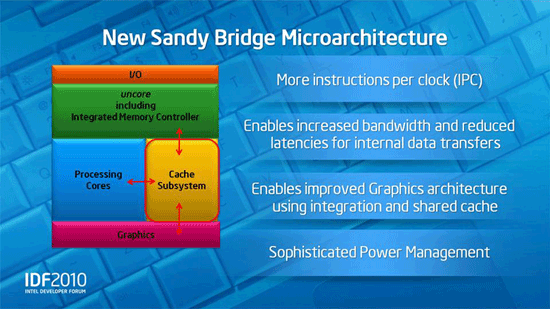

Si on ne voit pas grand chose sur le wafer, lune des vignettes de la présentation est plus parlante puisquelle dévoile le die en lui-même. On peut voir sur ce dernier la partie graphique (à gauche), suivie vers la droite de 4 cores.

On retrouve à droite le contrôleur mémoire et les I/O. Tout est donc inclus sur le die 32nm, alors que les Core i3/i5 actuels disposent dun die séparé en 45nm pour la partie graphique et mémoire, en sus du die 32nm pour le CPU en lui-même. Il ne va pas sans dire que cela augmentera la bande passante et diminuera sensiblement les latences, dautant que la partie graphique partagera le cache du processeur.

Intel annonce par ailleurs un IPC et une gestion de lalimentation amélioré, ce afin de permettre un nouveau saut en terme defficacité énergétique. Pour rappel, Sandy Bridge intégrera lAVX, qui nest ni plus ni moins que le successeur du SSE. Les registres passeront de 128 à 256 bits et permettra de travailler sur 3 opérandes, une idée qui sera également intégrée dans le SSE5 dAMD et qui permettra daller plus loin dans la fusion CPU/GPU.

Les 3 contenus de cette page