Les contenus liés aux tags Intel et 10nm

Afficher sous forme de : Titre | FluxIntel densifie sa SRAM 14nm et parle du 10 et 7nm

Résultats Intel en baisse, perspectives 2013

L'ITRS prépare l'après loi de Moore

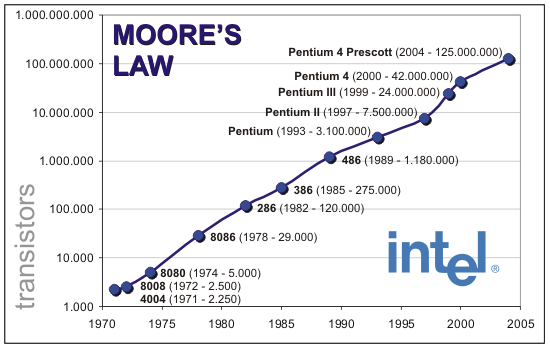

C'est la section actualité de la très sérieuse revue scientifique Nature qui l'affirme : la loi de Moore est arrivée à son terme. Énoncée en 1965 par Gordon Moore, l'un des cofondateurs d'Intel, il s'agit d'une observation par laquelle la quantité de transistors dans les circuits intégrés doublait à peu près tous les ans. Une observation transformée en loi pour prédire que cette cadence pouvait être extrapolée pour les années à venir.

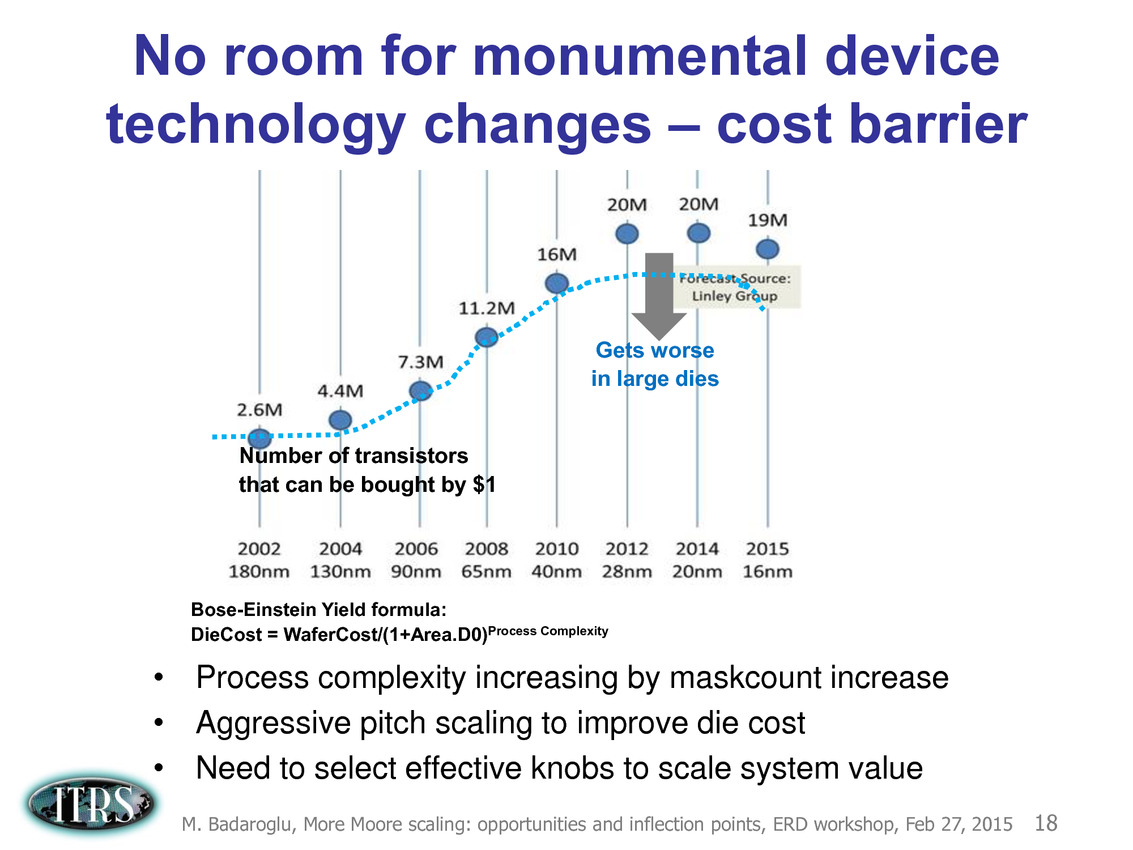

En 1975, la loi avait été révisée pour prendre la forme que l'on connaît actuellement, à savoir un doublement des transistors tous les deux ans. L'importance de la loi de Moore allait cependant au-delà de la simple prédiction puisqu'elle prenait en compte les coûts de fabrication : l'observation se fait sur les puces ayant le coût par transistor le plus faible (tentant donc de prendre en compte les questions de yields et de défauts en fonction de la taille des puces).

Plus qu'une prédiction, la loi de Moore a servie, particulièrement chez Intel, de guide au fil des années, prédisant à l'avance les budgets en nombre de transistors alloués aux ingénieurs, et poussant vers l'avant la nécessité d'investir dans de nouveaux process de fabrications, la fameuse stratégie du Tick-Tock poussée d'abord en interne par Pat Gelsinger au début des années 2000 avant d'être utilisée publiquement pour décrire les générations à venir.

De manière intéressante, au-delà d'Intel, c'est toute l'industrie du semi-conducteur qui s'est mise d'accord autour de la loi de Moore, à savoir non seulement les fondeurs, mais aussi et surtout les fournisseurs d'outils. Le besoin de coordination entre tous les acteurs aura conduit à l'élaboration d'une roadmap, d'abord appelée National Technology Roadmap for Semiconductors dès 1993, avant d'être renommée sous sa forme actuelle, l'International Technology Roadmap for Semiconductors (ITRS).

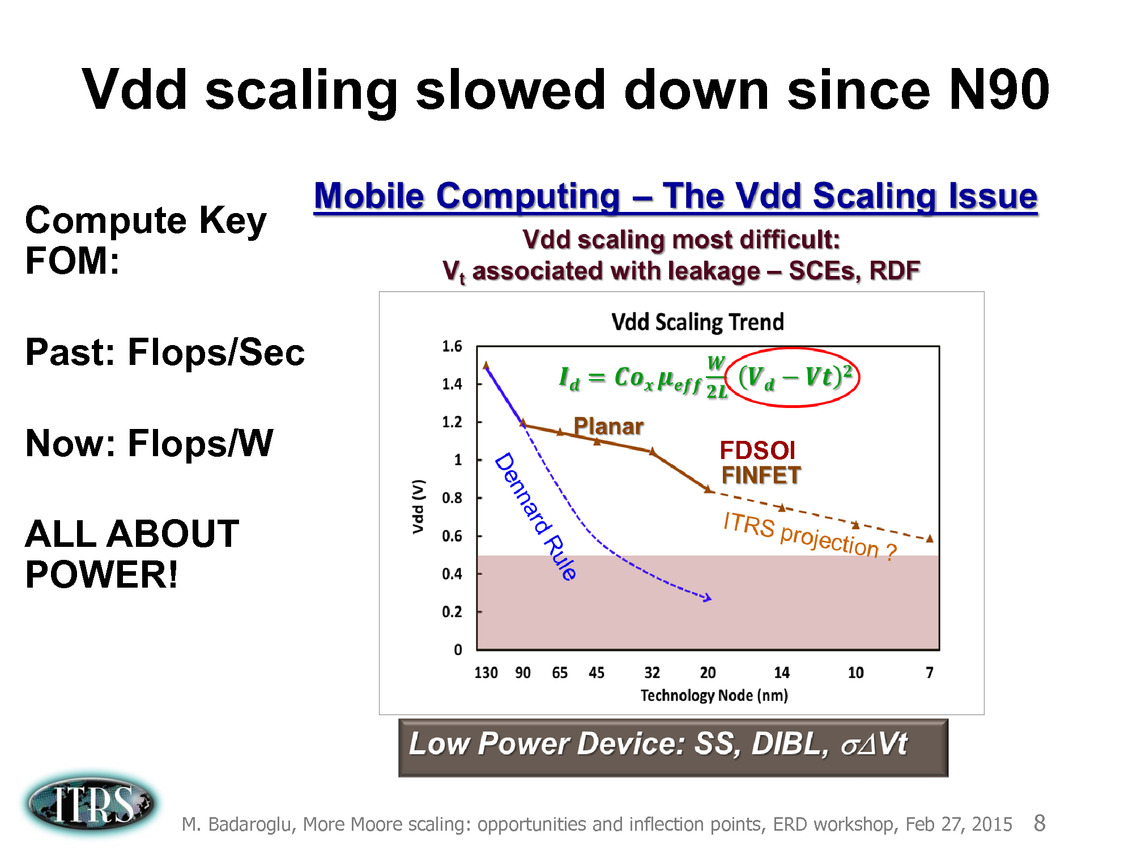

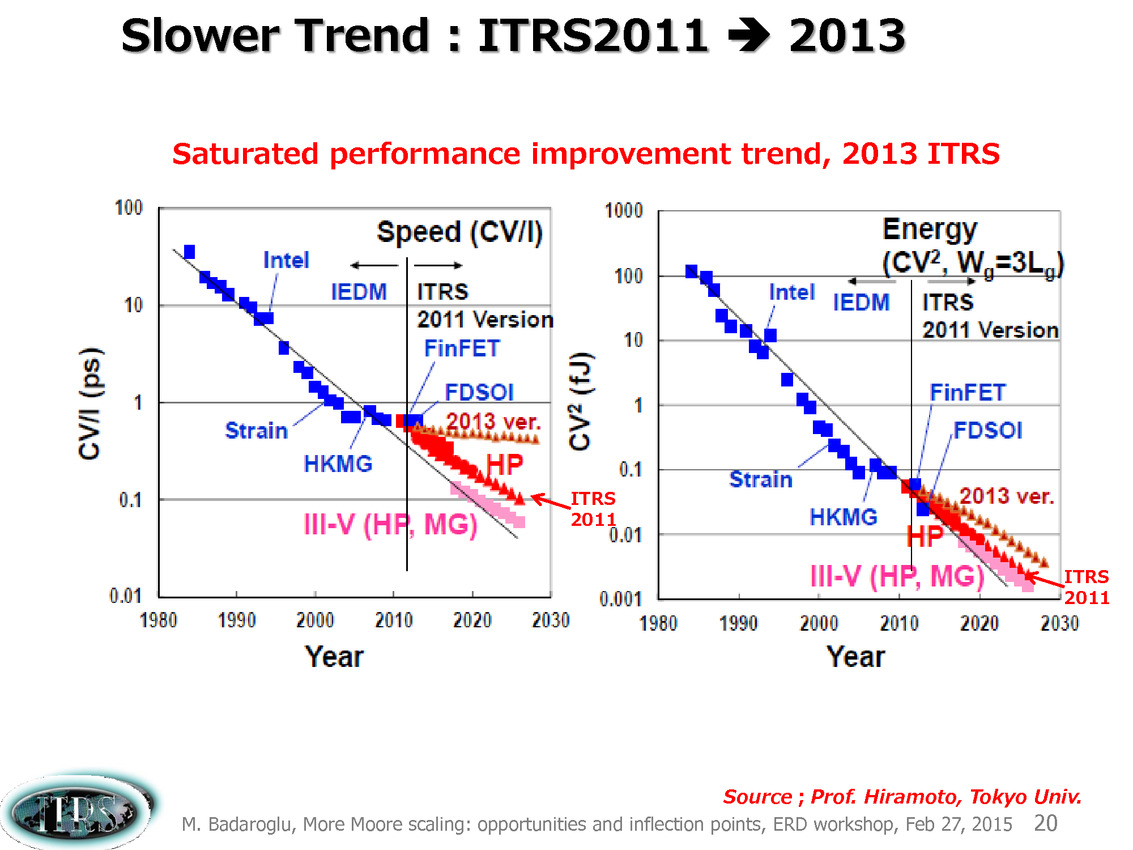

Le rôle joué par cette roadmap, dont la dernière version a été publiée en 2013 aura été particulièrement important ces dernières années où, passé le 90nm, les challenges techniques ont contraint à des changements d'approches importants. L'augmentation des performances par la fréquence, méthode classique aura atteint un plateau à cause de l'augmentation de la consommation, poussant dans le commerce les stratégies de multiplication des coeurs que l'on connaît. Le rôle de la roadmap, au-delà de la concertation, est de s'assurer de trouver des pistes pour continuer la cadence de réduction des coûts/augmentation des transistors de la loi de Moore.

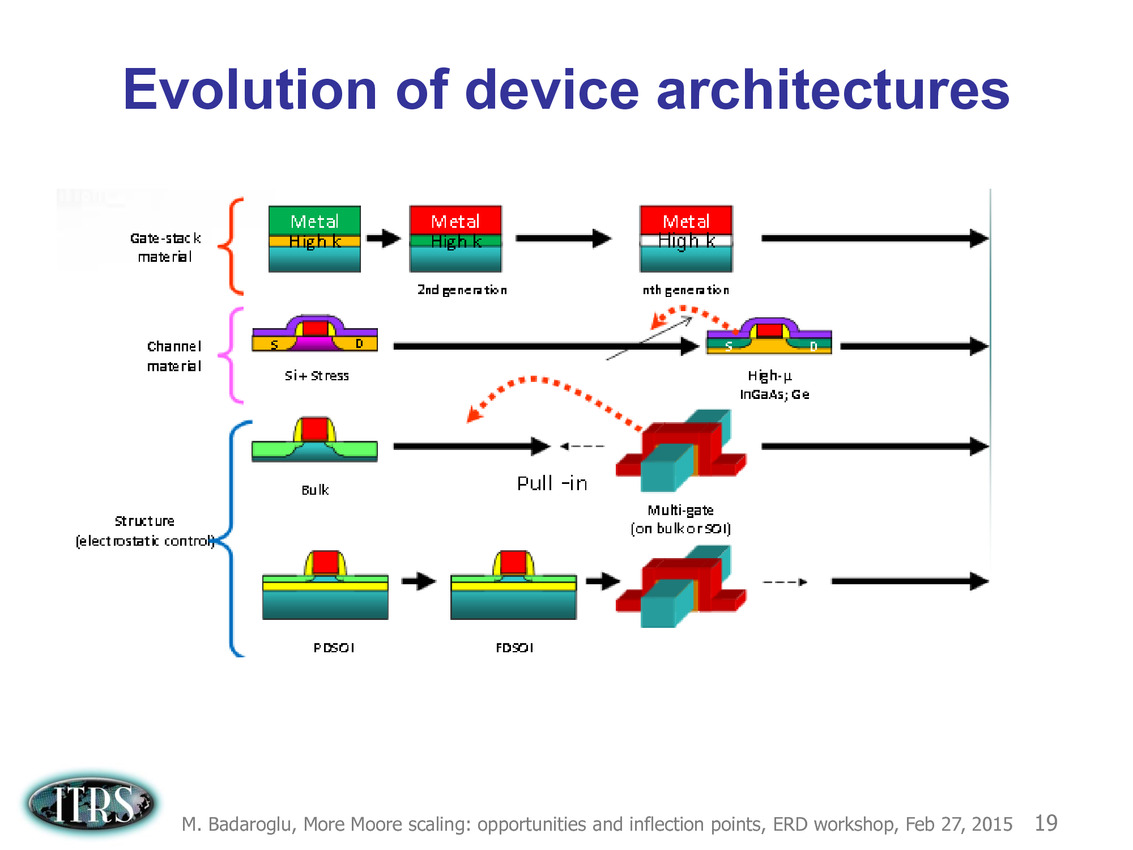

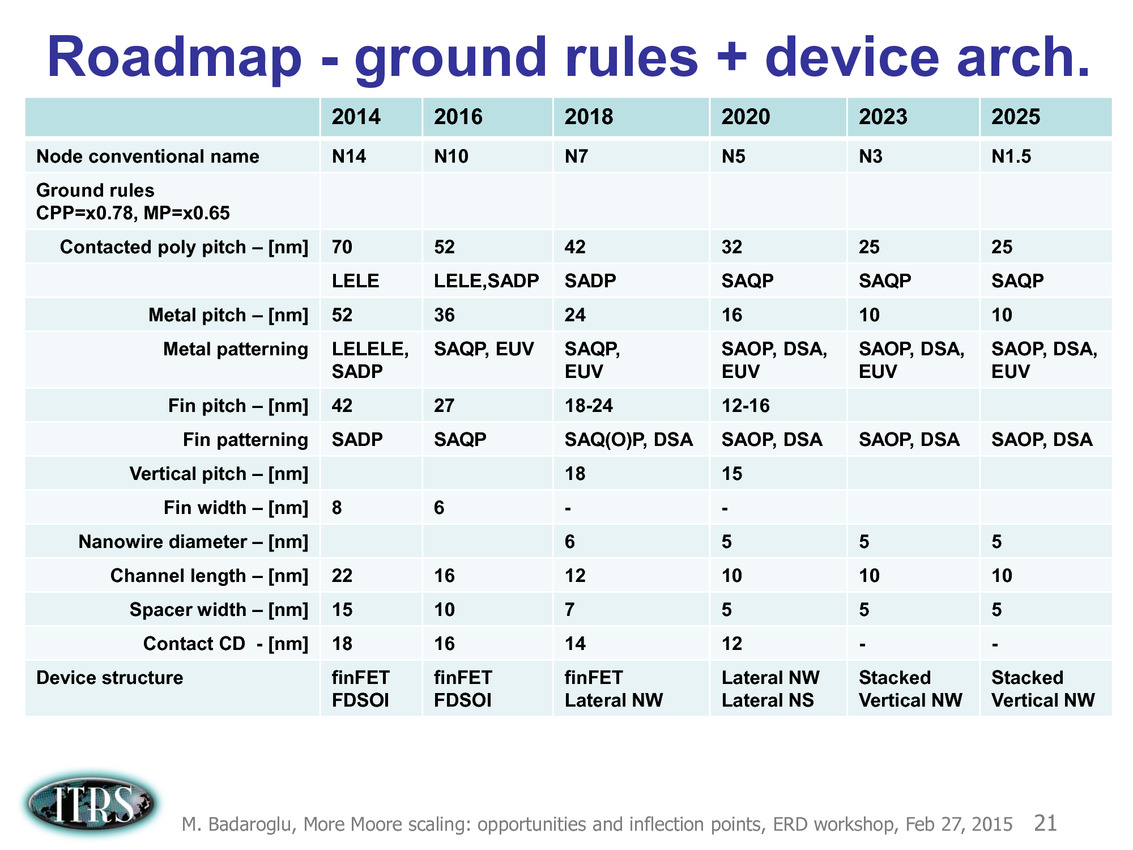

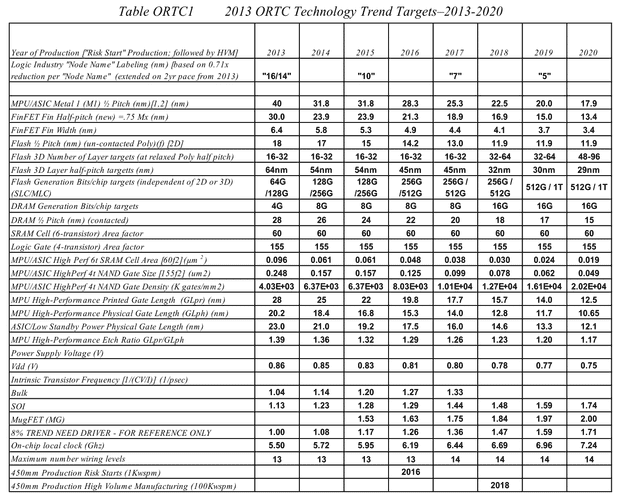

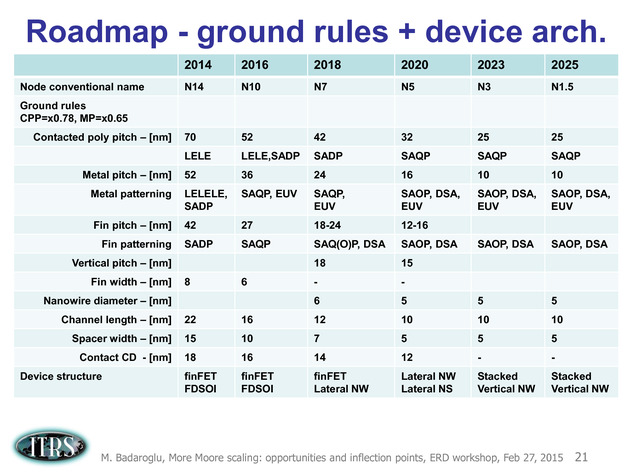

La dernière roadmap ci-dessus donnait des grandes lignes sur la manière de mettre à l'échelle les différents composants des transistors. Après les difficultés autour du 90nm, l'industrie est passé progressivement de la règle dite de la mise à l'échelle géométrique (on réduit tout dans des proportions identiques, le nom du node indiquant en général la taille de la porte) à celle de la mise à échelle par équivalence (equivalent scaling).

Etant donné que différentes parties composant les puces posent des problèmes différents, des règles d'équivalences ont été mises au point pour permettre de continuer a atteindre les buts de réduction des coûts/augmentation de densité imposé par la loi de Moore (on peut voir sur le tableau la couche d'interconnexion M1 et l'écart minimal entre deux transistors FinFET, en passant par des estimations des tailles de blocs fondamentaux comme la SRAM).

Pour 2016, la roadmap annonçait par exemple de la SRAM 6 transistors (6T) haute performance en 10nm autour de 0.048 µm2, ce qui n'est pas très éloigné de ce que présentait Samsung il y a une dizaine de jours de cela. En pratique cependant, on notera qu'on est globalement assez en retard sur la roadmap qui prévoyait des débuts de production à petite échelle en 10nm en 2015 (Risk Start dans la roadmap, suivi de HVM, fabrication en volume). Chez TSMC par exemple, la production risque est prévue pour la fin 2016 avec une production en volume pour 2017. Intel prévoit ses puces en volume pour 2017 également.

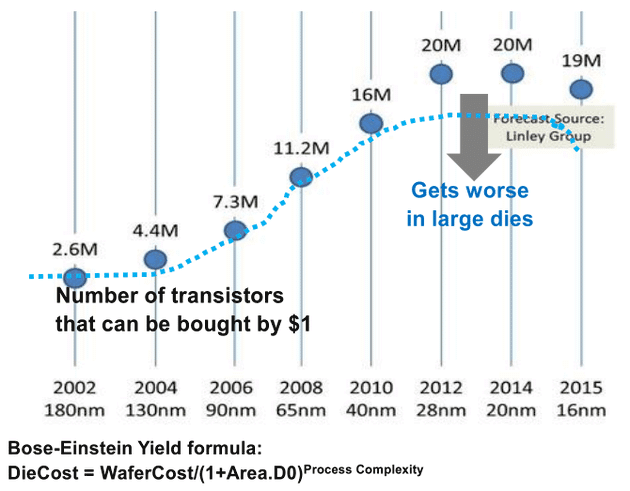

Évidemment depuis 2013 les choses se sont un peu plus compliquées et l'absence de roadmap en provenance de l'ITRS n'a pas forcément aidé. En pratique, la réduction des coûts s'est arrêtée, avec même un retour en arrière à 16nm signant de facto la fin de la loi de Moore, comme on peut le voir sur cette estimation ci-dessus tirée d'une présentation de l'ITRS en février 2015.

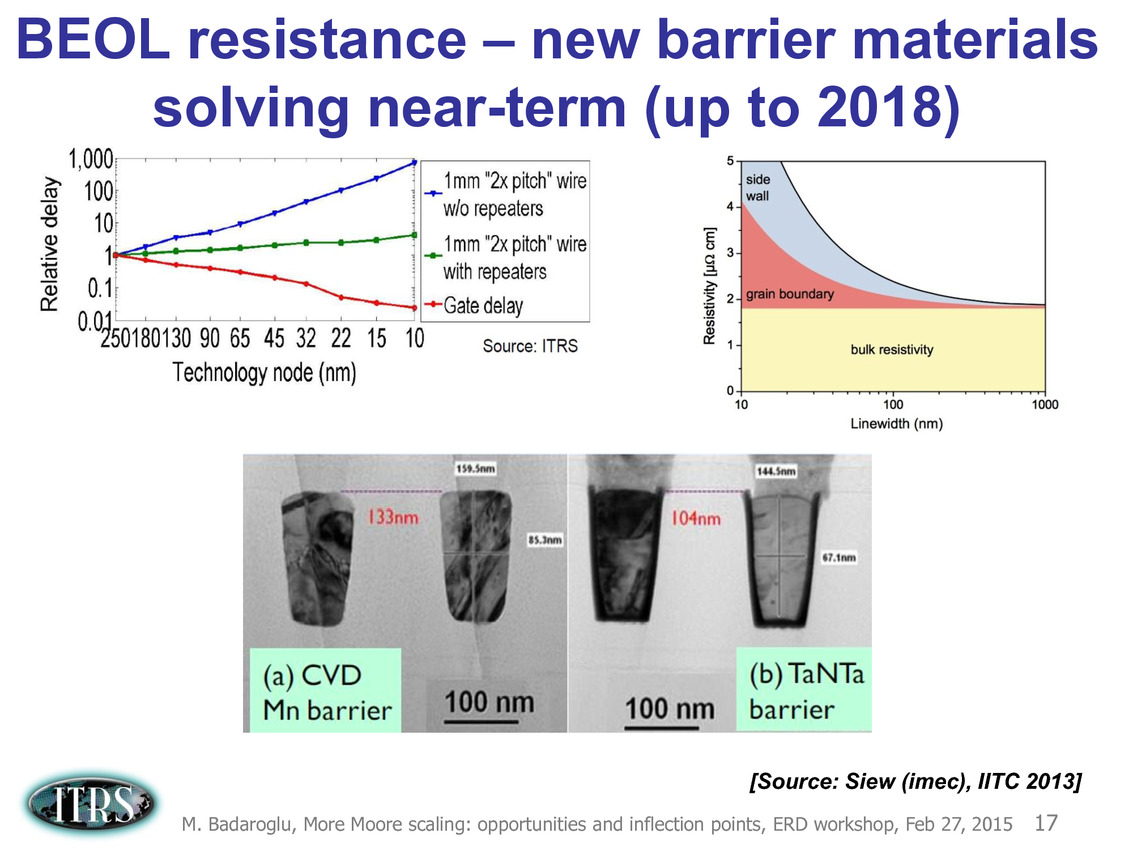

L'absence de nouvelle roadmap en provenance de l'ITRS aura même donné lieu à des divergences d'interprétations fortes, Intel titillant ses concurrents sur la question de la densité théorique. TSMC et Samsung ont fait pour rappel le choix de conserver un BEOL (Back End of Line, la partie basse d'une puce qui sert à l'interconnexion des transistors) commun entre le 20 et le 16nm pour accélérer la cadence de mise en production. En pratique chez TSMC, malgré le BEOL commun, le half pitch M1 reste tout de même dans les clous à 32nm (entre 40 et 31.8 sur la roadmap).

La densité pratique reste de toute manière très différente de ce que peuvent proposer des formules grossières comme celle utilisée par Intel (qui multipliait le pitch M1 par le pitch entre deux portes), qui pour exploiter les FinFET aura fait le choix d'utiliser pour certains de ses transistors critiques des structures plus larges composées de plusieurs fins (dans des proportions non négligeables même si la proportion exacte est rarement évoquée de manière précise par Intel).

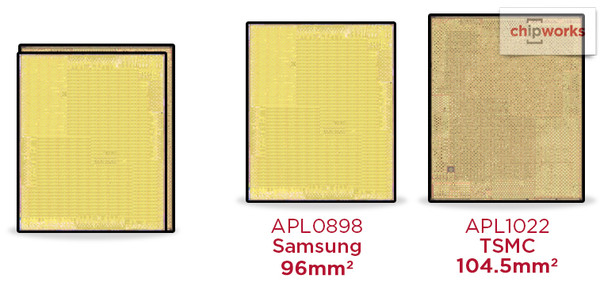

Cumulé a de multiples autres détails (différents types de blocs sont présents avec des densités différentes, de la SRAM aux blocs plus ou moins critiques) il est impossible de tirer grand-chose de la théorie. L'écart entre un Core M Broadwell 14nm fabriqué par Intel (82mm2 pour 1.3 milliards de transistors) et un A8 fabriqué par TSMC en 20nm (89 mm2 pour 2 milliards de transistors) montre qu'il est difficile de comparer quoique ce soit à moins de prendre deux puces strictement identiques. Cela aura été possible pour l'A9 d'Apple, dont la superficie atteint 96mm2 chez Samsung contre 104.5mm2 chez TSMC.

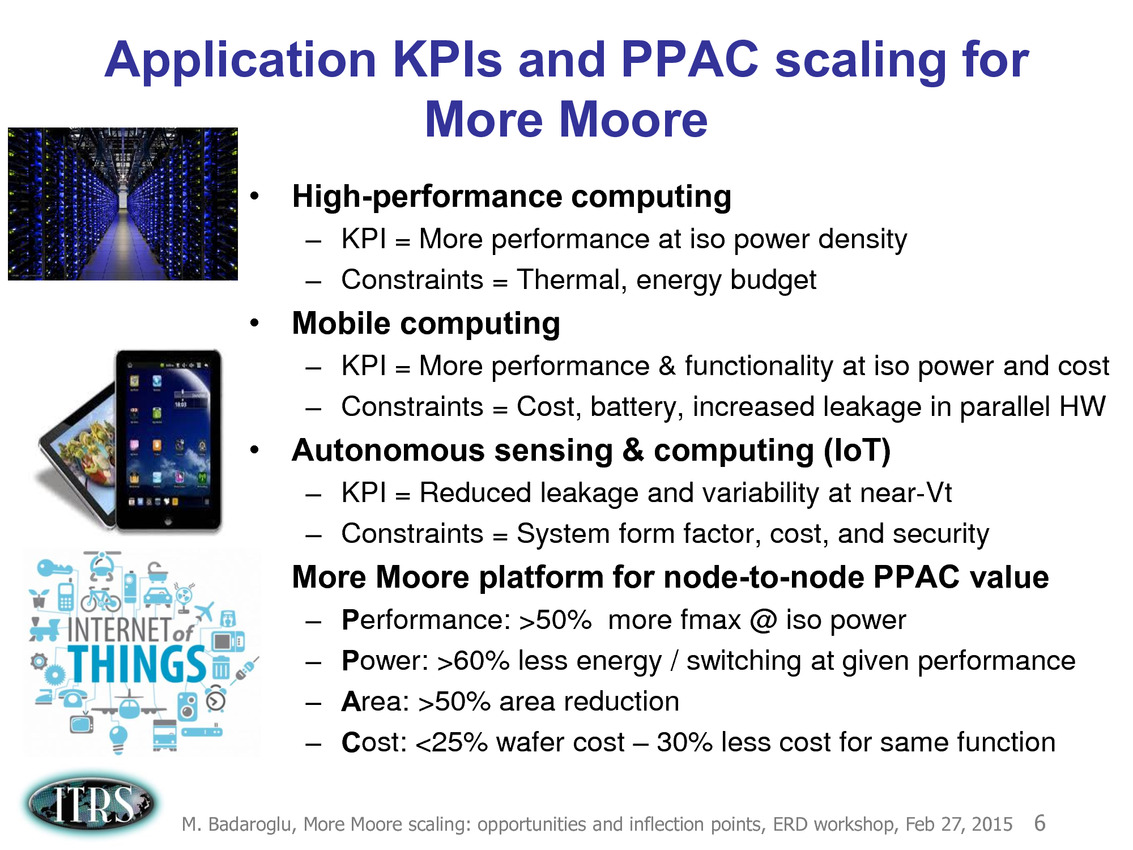

Le mois prochain, l'ITRS devrait donc enfin communiquer une nouvelle roadmap qui d'après Nature tirera définitivement un trait sur la question de la loi de Moore comme moteur d'évolution unique. D'après Nature, la prochaine roadmap se concentrera sur les applications pratiques, allant du smartphones aux puces serveurs et regardera les applications pratiques, que ce soit au niveau circuits d'alimentations, des capteurs nécessaires, ou d'autres blocs de siliciums répondant à des besoins particuliers.

La véritable question est de savoir ce que comportera réellement cette roadmap qui serait rebaptisée d'après Nature International Roadmap for Devices and Systems, abandonnant même le mot transistor !

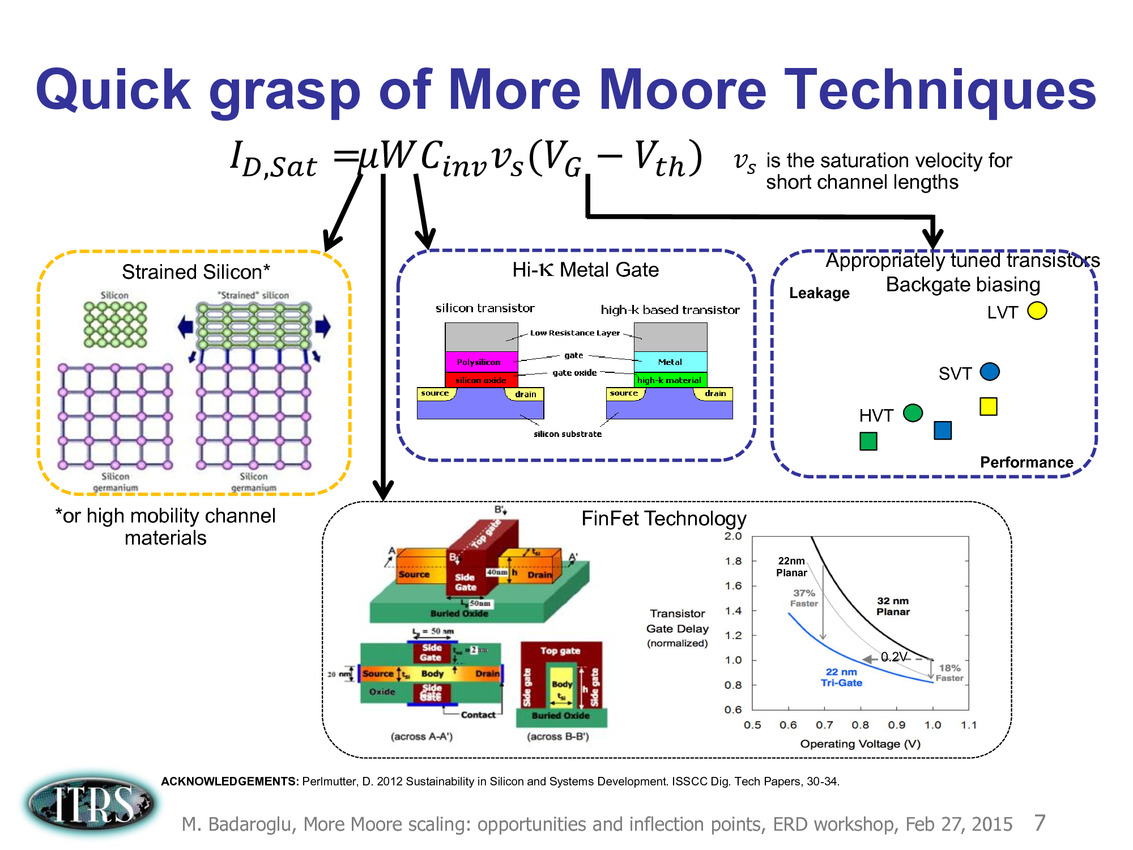

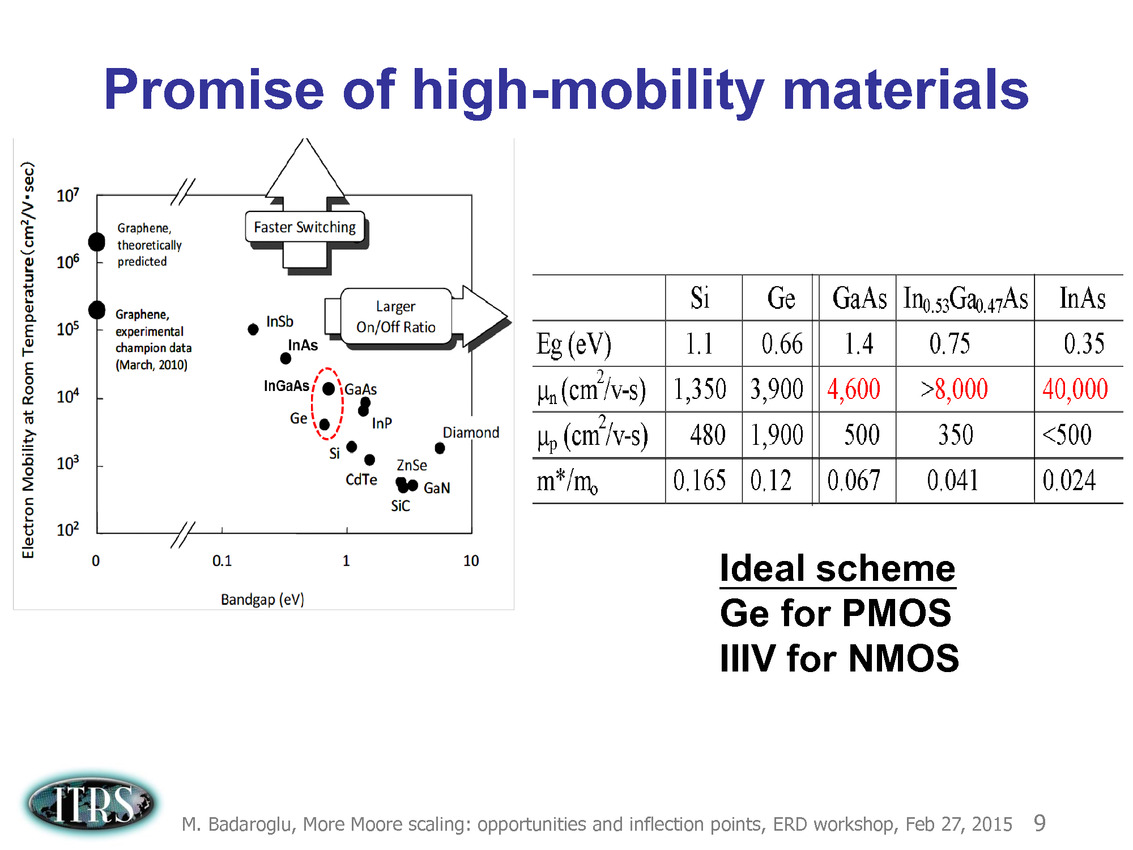

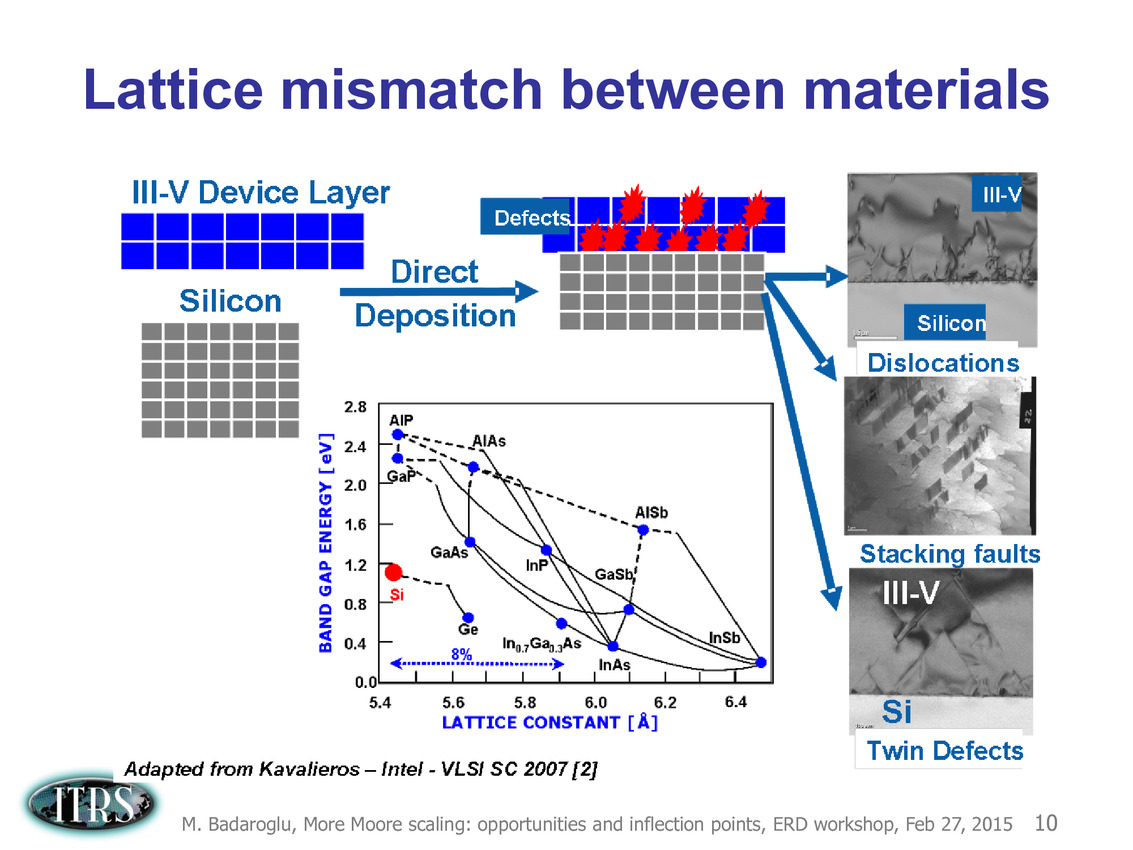

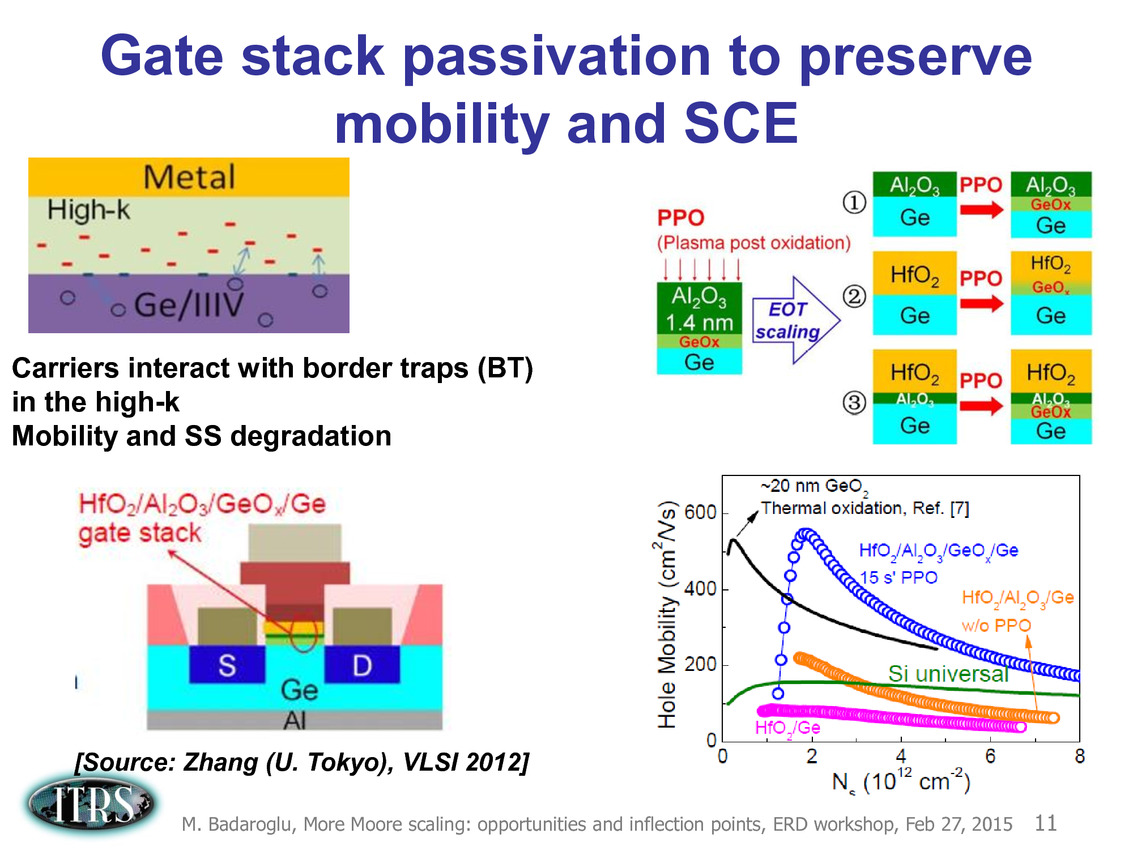

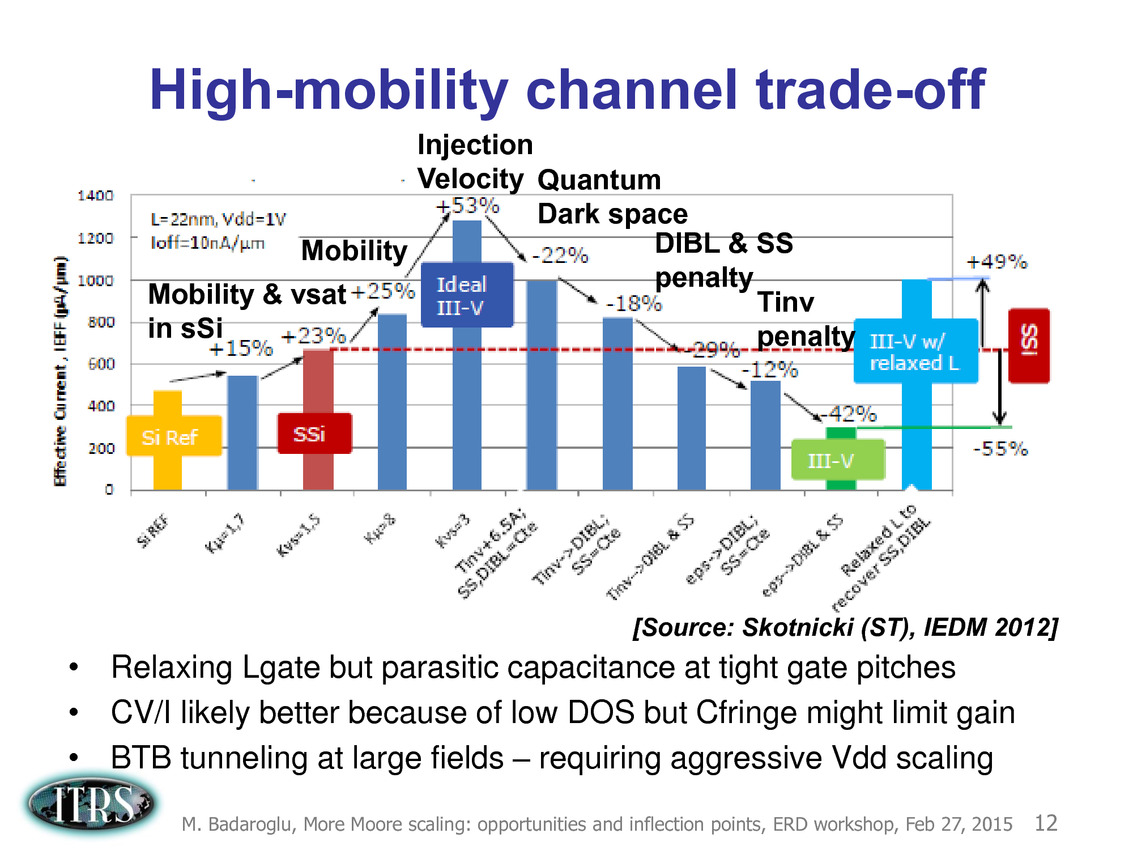

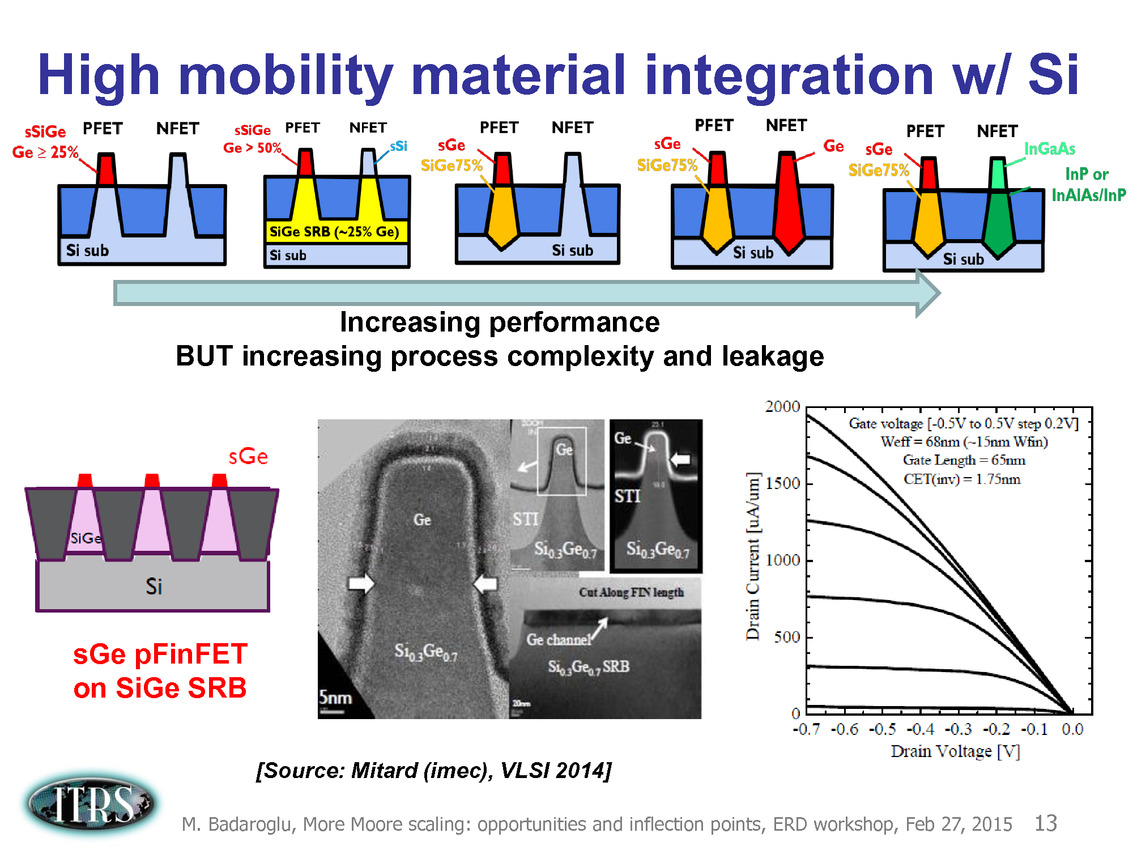

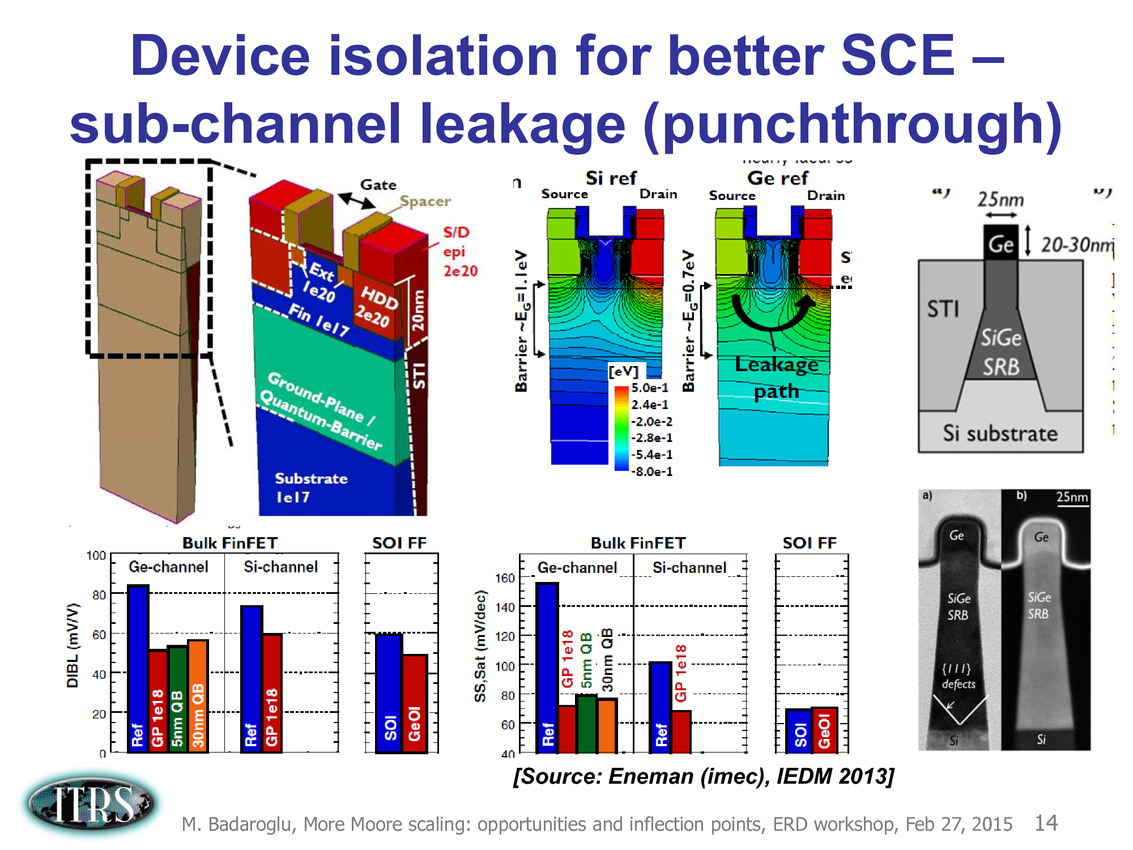

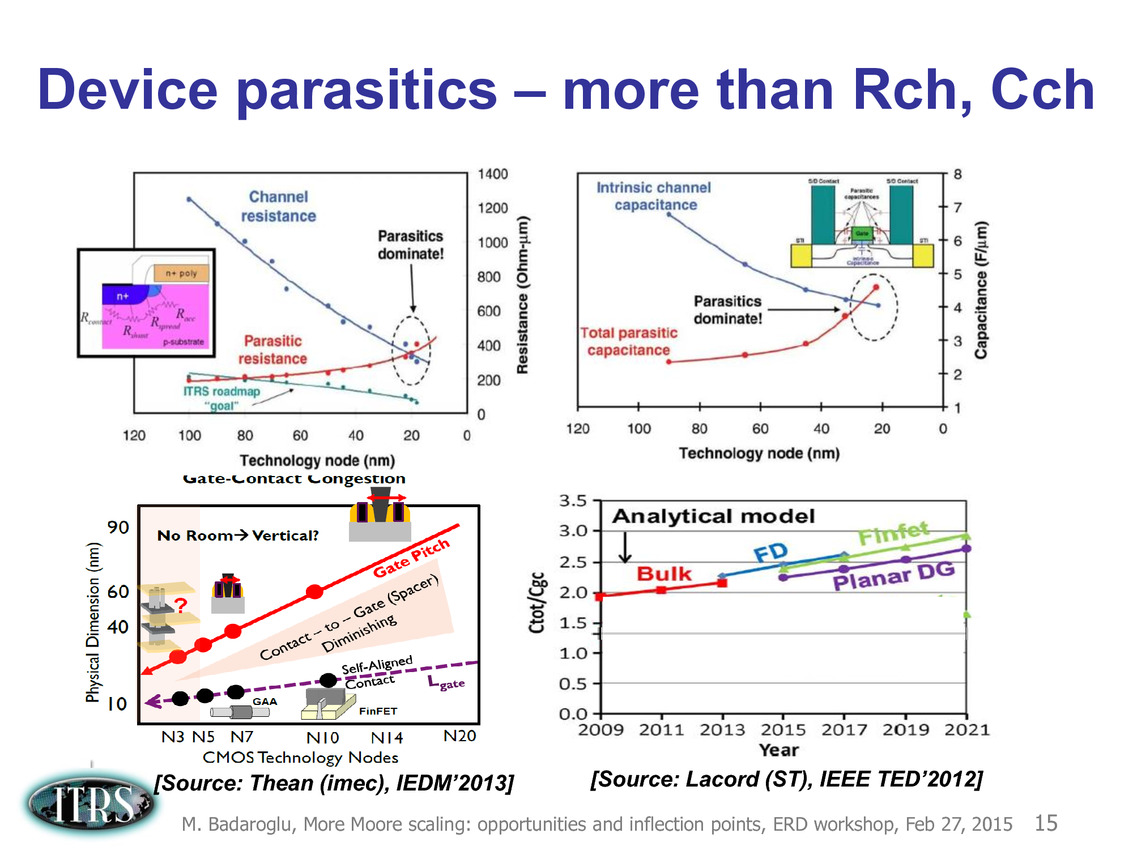

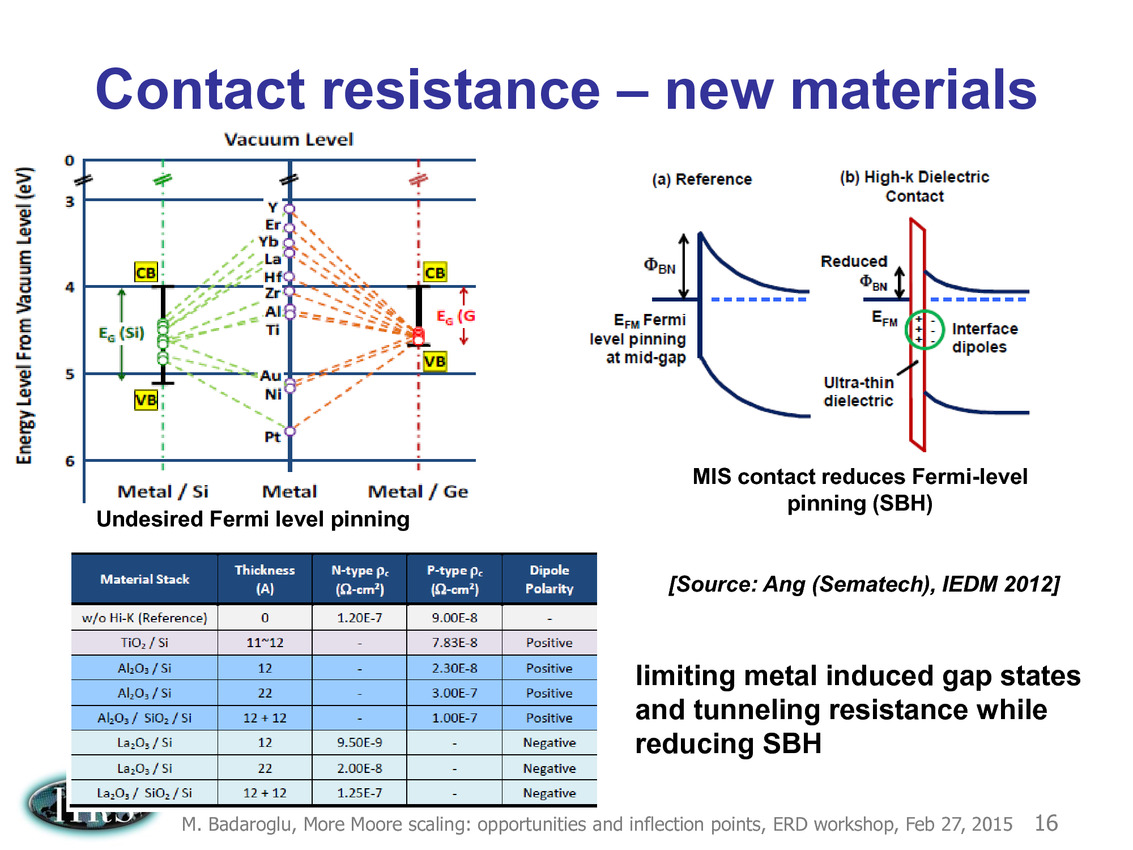

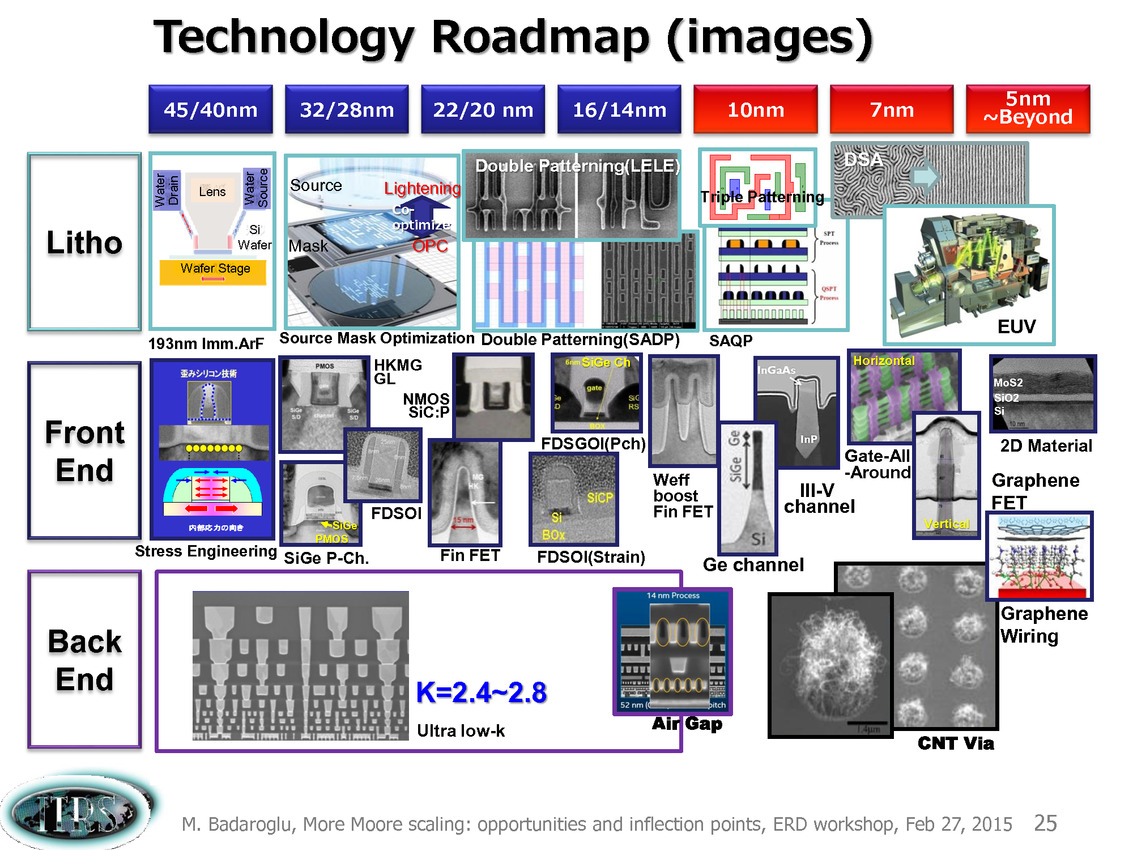

Ce que l'on sait, c'est que la réorganisation de l'ITRS en 2014 s'est faite autour de groupes de travaux, avec notamment un groupe baptisé « More Moore » pour évoquer les pistes techniques pour les prochains nodes, dont vous pouvez retrouver ci-dessous la dernière présentation datant de février 2015.

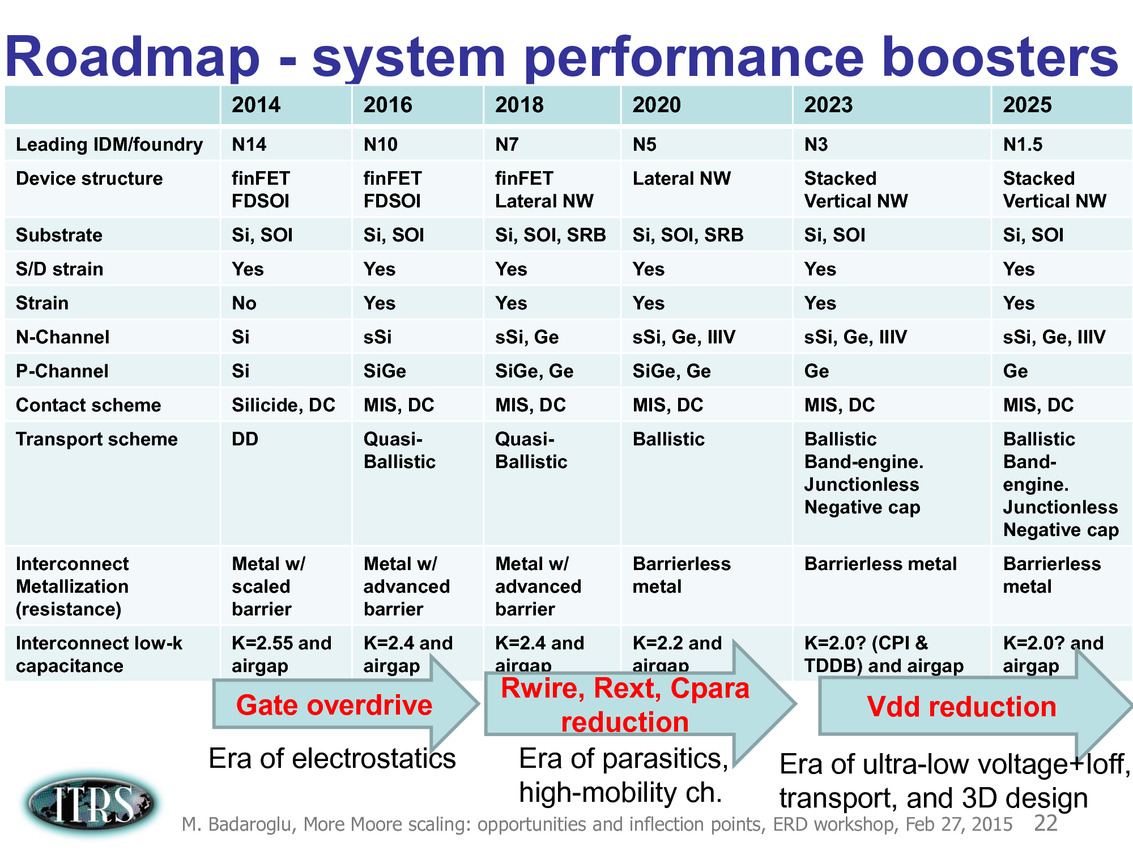

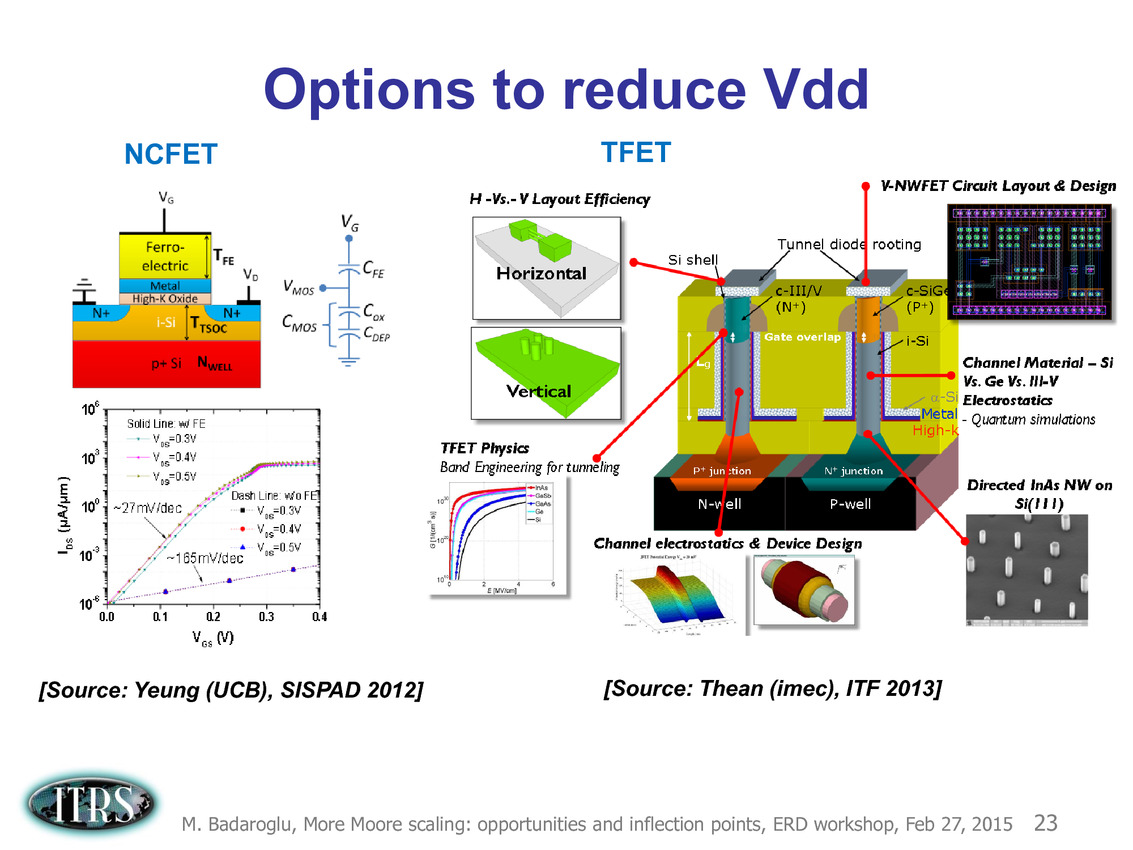

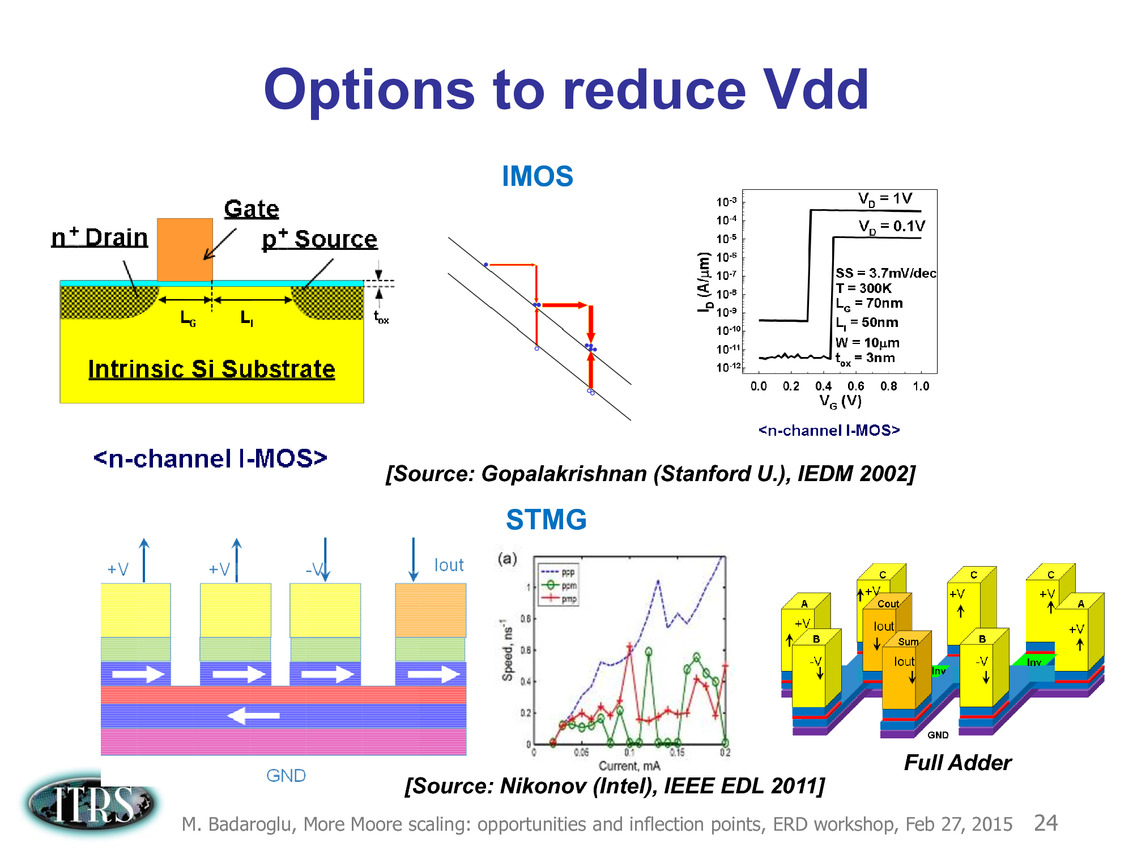

Une présentation intéressante qui évoque de multiples pistes et où l'on trouve un début de roadmap que nous avons remis ci-dessous :

En pratique, après l'ère de la mise à l'échelle géométrique, et l'ère des équivalences, l'ITRS évoque l'ère du "3D Power Scaling" dont les meilleurs représentants sont la NAND 3D ou des technologies comme la mémoire HBM. Des techniques complexes à appliquer aux puces logiques même si la présentation évoque quelques pistes et alternatives.

On attendra donc le mois prochain pour en savoir un peu plus !

3 architectures 10nm pour Intel ?

Alors qu'Intel a indiqué lors de ses résultats trimestriels avoir pour objectif de revenir au rythme habituel de 2 ans entre deux process de fabrication, il ne semble que ce retour à la normale ne soit pas prévu pour le passage à 7nm.

A l'instar de ce qui se passe sur le 14nm qui va voir passer successivement Broadwell, Skylake et Kaby Lake, ce sont ainsi trois architectures qui seraient prévues en 10nm selon Fool.com : Cannonlake pour le second trimestre 2017, Icelake un an plus tard et finalement Tigerlake au second semestre 2019. L'arrivée des produits en 7nm ne se ferait ainsi pas avant 2020, soit par rapport au planning annoncé en 2010 1 an de retard pour le 14nm, 2 ans pour le 10nm et 3 ans pour le 7nm.

Si Intel aime annoncer une densité supérieure de son 14nm par rapport aux process 14/16nm concurrents, ce que contredisent bien entendu ces derniers, l'arrivée de produits 7nm en 2020 mettrait tout le monde d'accord puisque côté TSMC on devrait voir des puces 7nm sortir des chaines de fabrication avant la fin 2018.

Un tel décalage peut paraître étonnant puisque c'est ASML qui équipe principalement toutes les fonderies, il est très probable qu'il découle en fait de choix différent entre d'un côté attendre l'EUV, ce que fera peut-être Intel pour le 7nm, ou faire appel à de plus en plus de multiple patterning et de parties de process communes avec le node précédent afin de repousser l'EUV au 5nm, ce qui est l'option prise par TSMC. L'avenir nous dira quels choix vont être faits et lequel sera le bon !

Intel abandonne le Tick-Tock, confirme Kaby Lake

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

Au milieu de l'annonce de nouveaux retards sur sa roadmap mobile (notamment SoFIA LTE qui est désormais attendu pour la première moitié de 2016), Brian Krzanich a indiqué que la transition d'un node à l'autre ne tenait plus réellement le rythme des 24 mois que le constructeur souhaitait s'imposer, mais que sur les deux générations précédentes, il était plus proche des deux années et demi. En conséquence, la stratégie du Tick-Tock doit s'adapter et il aura confirmé l'arrivée d'un troisième produit 14 nm, Kaby Lake qui sera lancé durant la seconde moitié de 2016 (comme on le pressentait le mois dernier) !

Le CEO d'Intel décrit Kaby Lake comme « bâti sur les fondations de la micro architecture Skylake », mais « avec des améliorations clefs de performances ». Un phrasé relativement vague qui laisse entendre qu'il s'agirait d'un peu plus que d'un « Skylake refresh », sans vraiment s'engager (possiblement un nouveau GPU seulement ?). Le lancement de Cannonlake est lui bel et bien repoussé à la seconde moitié de 2017, en 10nm.

Interrogé (légèrement) sur le sujet par les analystes, Brian Krzanich a qualifié le retard par la complexité croissante de mise au point des process et que les difficultés du 10nm, si elles étaient similaires en pratique à celles rencontrées pour le 14nm, n'étaient pas directement liées au retard du 14nm. Intel est sur le sujet dans une position délicate puisque le constructeur a toujours clamé que le retard du 14nm n'aurait aucun impact sur le 10nm. Selon le CEO, la lithographie continue à être de plus en plus complexe, notamment à cause de l'augmentation des étapes de multi-patterning. En marge de cela, il aura rappelé que le 10nm d'Intel sera une solution sans EUV (le reste de l'industrie ne s'attends pas non plus à disposer de l'EUV pour le 10nm).

Pour le CEO, rajouter Kaby Lake à la roadmap permet d'améliorer la « prévisibilité » pour ses partenaires. Un argument qui ne manque pas d'ironie quand l'on connait l'historique du Tick-Tock chez Intel. La stratégie du Tick-Tock avait été mise en place en interne chez Intel au début des années 2000 par Pat Gelsinger dans le but de mettre de l'ordre dans le développement parfois anarchique des architectures qui a conduit à de nombreux projets et architectures repoussés et abandonnés. En interne, il s'agissait de délimiter clairement le périmètre de deux équipes de développement d'architectures, une située en Oregon et l'autre en Israël. Le tout articulé autour des changements de process tous les deux ans.

Ainsi chaque nouveau passage à un process (65 vers 45 nm, etc) serait un Tick. Une version légèrement modifiée de l'architecture précédente, portée vers le nouveau node (ce que l'on appelle un die shrink), tandis que la « nouvelle architecture », le Tock serait lancé l'année suivante, lorsque le process de fabrication serait arrivé à maturité.

Historiquement, ce n'est qu'avec beaucoup de créativité que le constructeur aura pu compter 24 mois entre chaque node, des retards de plusieurs mois ayant été observés au fil des années mais globalement jusqu'ici Intel s'était imposé de tenir le modèle de deux produits principaux (on met de côté les produits/architecture dédiées spécifiquement à la mobilité) par node sur environ deux ans.

Avec le 14nm le modèle n'était plus tenable, obligeant en 2014 Intel à proposer un Haswell refresh, simple « speed bump » d'Haswell, lancé en juin 2013 en lieu et place de Broadwell. En pratique si Intel s'est targué d'avoir « lancé » le 14nm en 2014, il s'agissait d'un seul processeur, le Core M, qui plus est dans un stepping remplacé avant même sa sortie ! Et pour le desktop, la gamme Broadwell aura été réduite au minimum avec seulement deux modèles, lancés le mois dernier pour tenir les annonces. Avec au final un retard d'un an sur la cadence que s'imposait jusqu'ici Intel.

En pratique Skylake (le tock original 14nm) est toujours attendu pour cette année même si Intel n'a pas encore confirmé de quelle manière s'effectuerait son lancement. Il a été indiqué par Intel qu'une des conséquences du ralentissement de l'activité en Q2 était un inventaire encore important, laissant penser que le constructeur pourrait repousser certains SKU de Skylake. Le lancement des modèles K était prévu pour rappel pour le 5 aout, tandis que le reste de la gamme 4 curs était attendue entre le 30 aout et le 5 septembre. On ne s'étonnerait pas de voir ces références repoussées de plusieurs semaines afin d'écouler les inventaires existants, même si Intel ne l'a pas dit clairement.

On notera également qu'au détour d'une question, Brian Krzanich a confirmé que le 10nm d'Intel utiliserait toujours des FinFET, et non un autre type de structures comme certaines rumeurs avaient pu le laisser entendre. Il a indiqué que le 10nm serait la troisième génération de FinFET d'Intel. A une autre question il a indiqué que des changements de matériaux étaient par contre attendus sans les préciser.

Interrogé enfin sur l'impact de ces retards sur « l'avance » d'Intel en matière de process par rapport au reste de l'industrie, Brian Krzanich s'est voulu rassurant, indiquant que l'avance d'Intel ne diminuerait pas sur le reste de l'industrie. De notre point de vue, il est probable que TSMC, et possiblement Samsung lancent une production en volume autour, voir même un peu avant Intel. Ce qui serait, au moins pour l'image, un véritable drame pour la firme de Santa Clara.

Cannonlake 10nm retardé à 2017, Kaby Lake pour 2016 ?

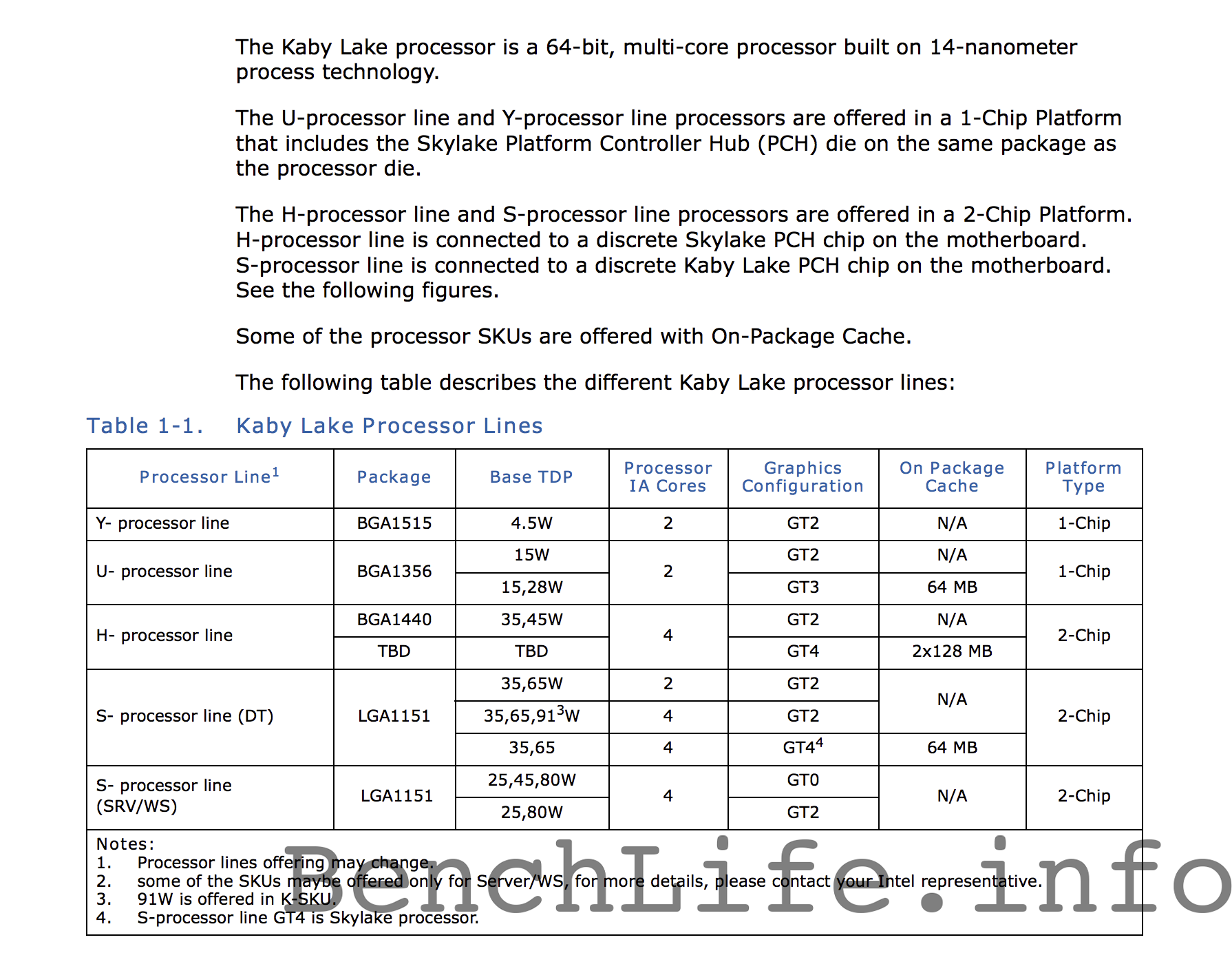

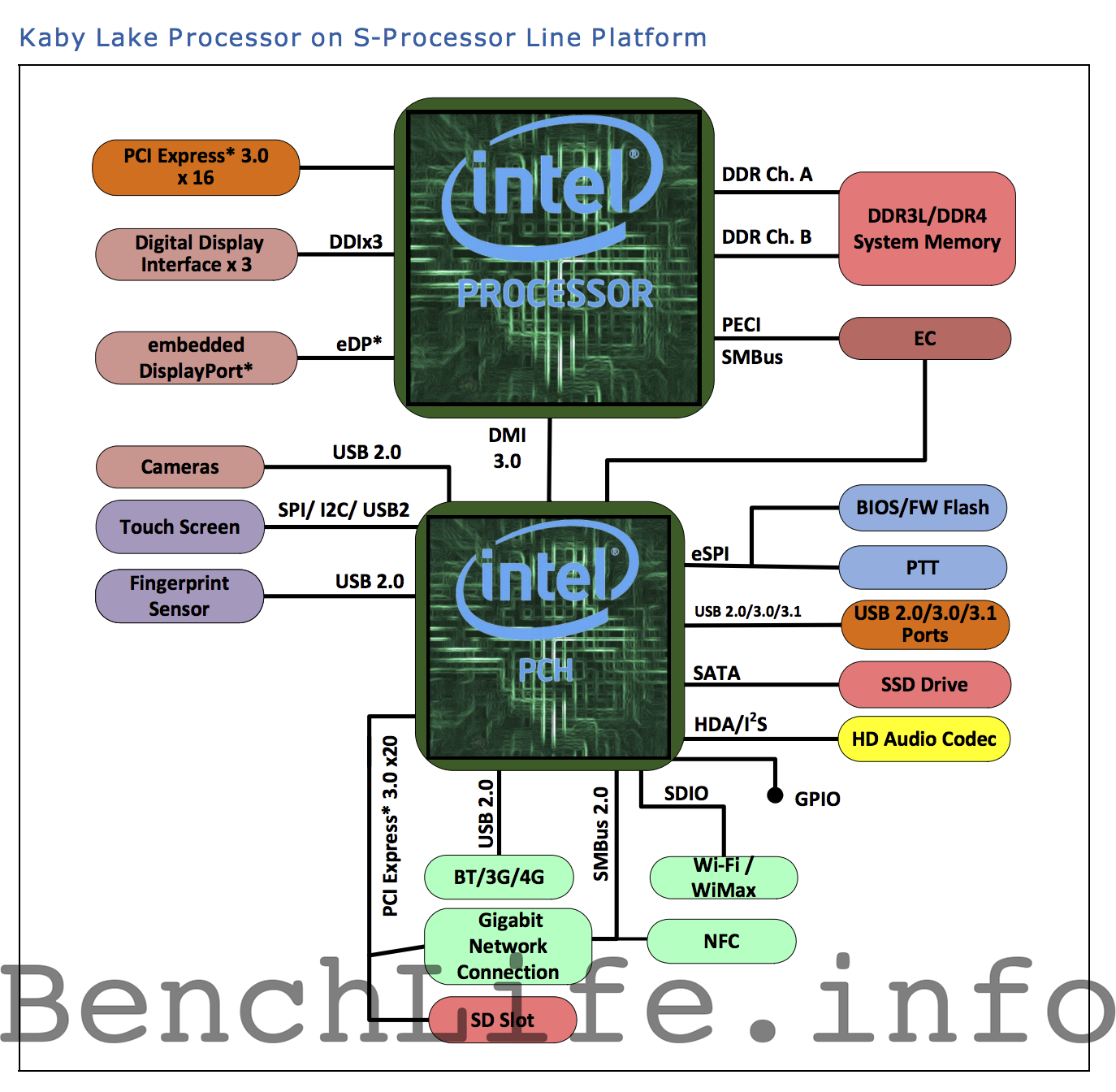

Selon Benchlife.info , Intel sera en retard sur Canonnlake, qui est pour rappel un "tick" en 10nm de Skylake. Afin d'avoir tout de même une nouveauté à se mettre sous la dent en 2016, une nouvelle ligne de processeur 14nm, Kaby Lake, serait à l'ordre du jour.

Comme d'habitude de nombreuses déclinaisons sont listées mais on ne sait pas vraiment en quoi ces processeurs seront différent des Skylake. S'agit-il d'un simple speed bump comme nous l'avons déjà connu avec Haswell Refresh ? Seule vraie nouveauté apparente, au format BGA en gamme H une puce est listée avec 2x128 Mo d'eDRAM embarquée, contre au mieux 128 Mo sur Broadwell et Skylake, ce qui devrait permettre d'augmenter les performances de l'iGPU.

Sur desktop on reste en LGA 1151 avec 2 à 4 curs, avec 35/65W en 2 curs et 35/65/91W en 4 curs. Le TDP de 91W concerne les processeurs en version K, ce chiffre est assez étrange puisqu'il est censé être de 95W sur le Skylake K. Intel prévoit également de sortir des versions 4 curs LGA 1151 accompagnées de l'iGPU soit GT4, qui intègre 72 Executions Units (soit 50% de plus que sur un GT3 Skylake ou Broadwell), et de 64 Mo d'eDRAM. Autre bizarrerie alors que ce tableau est censé représenter la ligne de processeurs Kaby Lake ces versions sont annotées comme étant des Skylake !

Côté chipset le diagramme laisse penser qu'on aura droit à une nouveauté avec l'arrivée de l'USB 3.1 qui pour rappel double les débits pour atteindre 800 Mo /s en pratique (cf. notre focus). Une mise à jour mineure mais qui permettra à tous les fabricants de cartes mères de sortir leur nouvelle gamme annuelle même en l'absence de nouveauté importante, comme ce fut le cas à l'époque du Z97.

Après un passage au 14nm retardé, Intel connaitrait-il des déboires sur le 10nm ? C'est ce qu'on peut penser si le retard de Cannonlake se confirme, ce qui augure d'une année 2016 assez morose côté CPU chez Intel, alors qu'on attend dans le même temps le retour sur le devant de la scène d'AMD avec Zen !

ASML vend 15 machines EUV à Intel

La société ASML s'est fendu hier d'un communiqué de presse pour indiquer avoir signé un accord important pour la vente de machines de lithographie EUV. Nous étions revenus sur le sujet à la fin du mois dernier, après de long et multiples retards, cette technologie de lithographie nouvelle génération avait effectué quelques progrès substantiels, notamment chez TSMC, qui avait commandé deux machines NXE:3350B livrables cette année, des machines dédiées au 10nm.

Le communiqué d'ASML indique que la firme néerlandaise a trouvé un accord avec un de ses « gros client américain » pour livrer, dans un délai non précisé, 15 machines EUV. Deux de ces machines au moins seront de type NXE:3350B (10nm) et seront livrées cette année.

Il ne faut pas trop d'imagination pour deviner que le client en question est Intel. La société avait investi de manière importante dans ASML en 2012 même si elle restait prudente sur l'utilisation à venir de la technologie. Cet accord semble montrer un regain d'intérêt autour de l'EUV, même si à l'image de TSMC on s'attend probablement à un déploiement initial autour du 7nm.

La cadence de production des machines sera en effet étalée dans le temps. Six (à huit) machines NXE:3350 devraient être vendues cette année (deux à Intel, deux à TSMC et possiblement deux à Samsung qui était le troisième à avoir investi dans ASML en 2012). La production devrait s'intensifier progressivement puisque ASML table sur la production de douze machines en 2016, vingt-quatre en 2017 et 48 en 2018.

On notera enfin que si l'intérêt autour de l'EUV se porte aujourd'hui pour la fabrication de circuits logiques (processeurs), ASML compte également déployer l'EUV auprès des fabricants de mémoire DRAM dans un second temps. La production de mémoire flash NAND en EUV pourrait suivre avec un décalage de deux à trois ans selon le CEO d'ASML.