Les contenus liés aux tags AMD et Zen

Afficher sous forme de : Titre | FluxVentes d'AMD en baisse, Zen et Polaris en ligne de mire

CES: Discussion avec Lisa Su, CEO d'AMD

Pas encore de tape-out pour Zen, dispo en 2017 ?

Bristol Ridge, un Carrizo en AM4 en attendant Zen

Résultats en baisse pour AMD

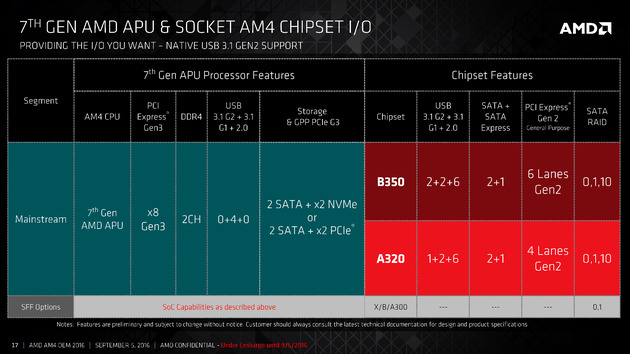

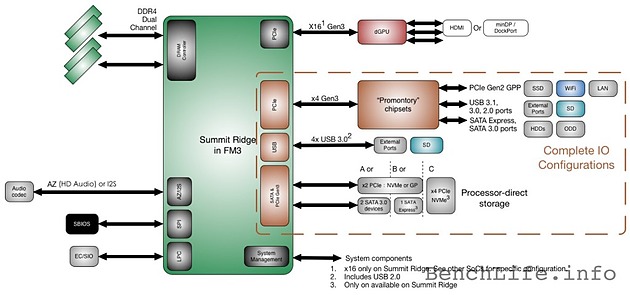

Chipset X370 pour les Zen Summit Ridge

Il y a deux semaines de cela, AMD A lancé sa "7ème" génération d'APU desktop, les Bristol Ridge. Il s'agit pour rappel d'une version desktop de l'APU mobile Carrizo, utilisant toujours l'architecture Bulldozer/Excavator et fabriqués en 28nm.

Contrairement aux APU précédentes, elles ne sont pas compatibles avec le socket FM2+, mais avec le nouveau socket AM4 qui sera également utilisé avec par les futurs Zen Summit Ridge.

Deux chipsets ont été lancés pour l'occasion, les A320 et B350 mais nous notions qu'un modèle plus haut de gamme était prévu pour le lancement des Zen. Le site Benchlife confirme en annonçant le nom du chipset qui s'appellera X370.

Ce chipset devrait se retrouver sur des cartes mères plus haut de gamme qui seraient dévoilées au CES. Officiellement le lancement de Zen est prévu pour le premier trimestre, nos confrères s'avançant à parler d'une fenêtre probable pour le mois de février pour les Summit Ridge et les cartes mères X370.

AMD détaille l'architecture de Zen

Comme annoncé, AMD a profité de la conférence Hot Chips pour dévoiler les détails de l'architecture des cores CPU Zen, utilisée par ses prochains processeurs. AMD avait déjà dévoilé la semaine dernière quelques grandes lignes, cette fois on dispose de beaucoup plus de détails techniques.

Notez qu'en ce qui concerne les versions disponibles des puces, le nombre de cores, la fréquence, ou le fonctionnement du contrôleur mémoire, il faudra attendre, AMD ne dévoilera ce type de détails qu'ultérieurement. On a tout de même droit à nombre de détails techniques.

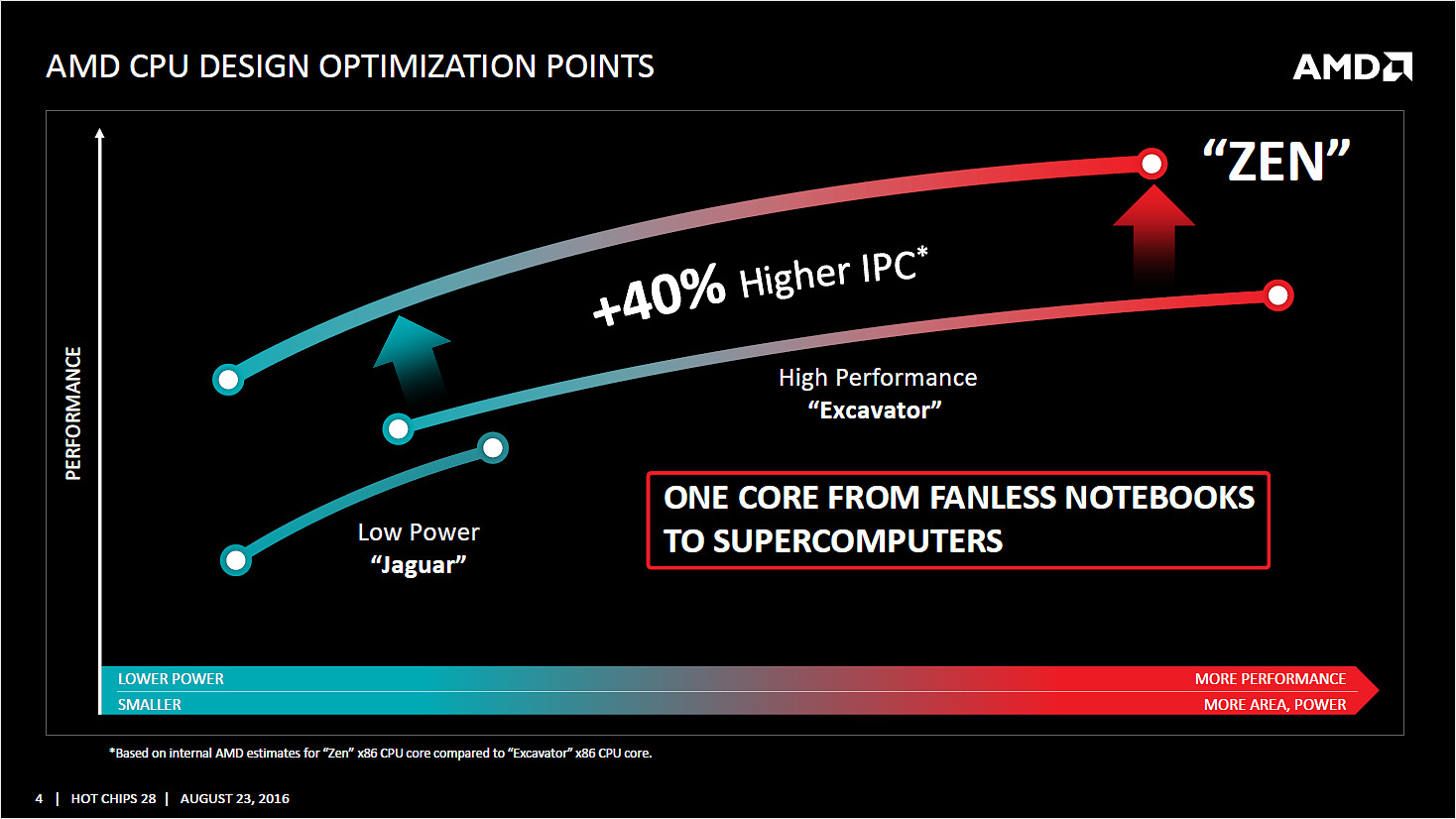

Le message de base d'AMD est de dire que l'architecture est repartie d'une feuille blanche, même si AMD concède avoir réutilisé certains blocs fonctionnels de ses architectures précédentes. En pratique, Zen aura été développé pour remplacer intégralement Jaguar et Excavator, ce qui laisse penser qu'on verra Zen décliné dans de larges gammes de TDP dans les mois à venir.

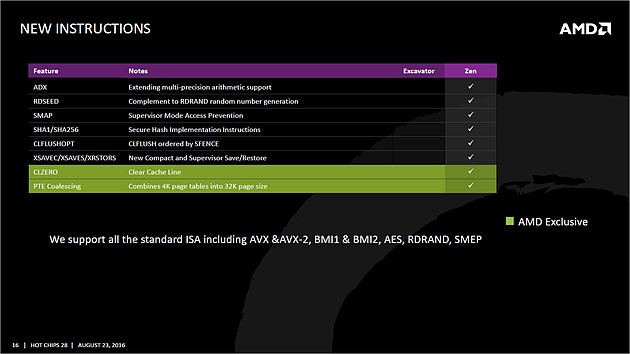

Le jeu d'instruction

Avant d'entrer dans les détails, un point sur les jeux d'instructions. AMD se met à jour en supportant à peu près toutes les extensions existantes, on retrouve ainsi AVX et AVX2, l'accélération des instructions SHA, mais aussi des choses plus originales comme les instructions de mémoire transactionnelle (TSX), introduites avec assez peu de succès par Intel pour Haswell. AMD rajoute en prime deux instructions, dont une pour libérer une ligne de cache, et l'autre pour combiner des pages mémoires. AMD est donc aligné sur ce que proposait Intel jusque Broadwell, Skylake n'ajoutant que SGX et MPX dont l'utilisation est plus particulière.

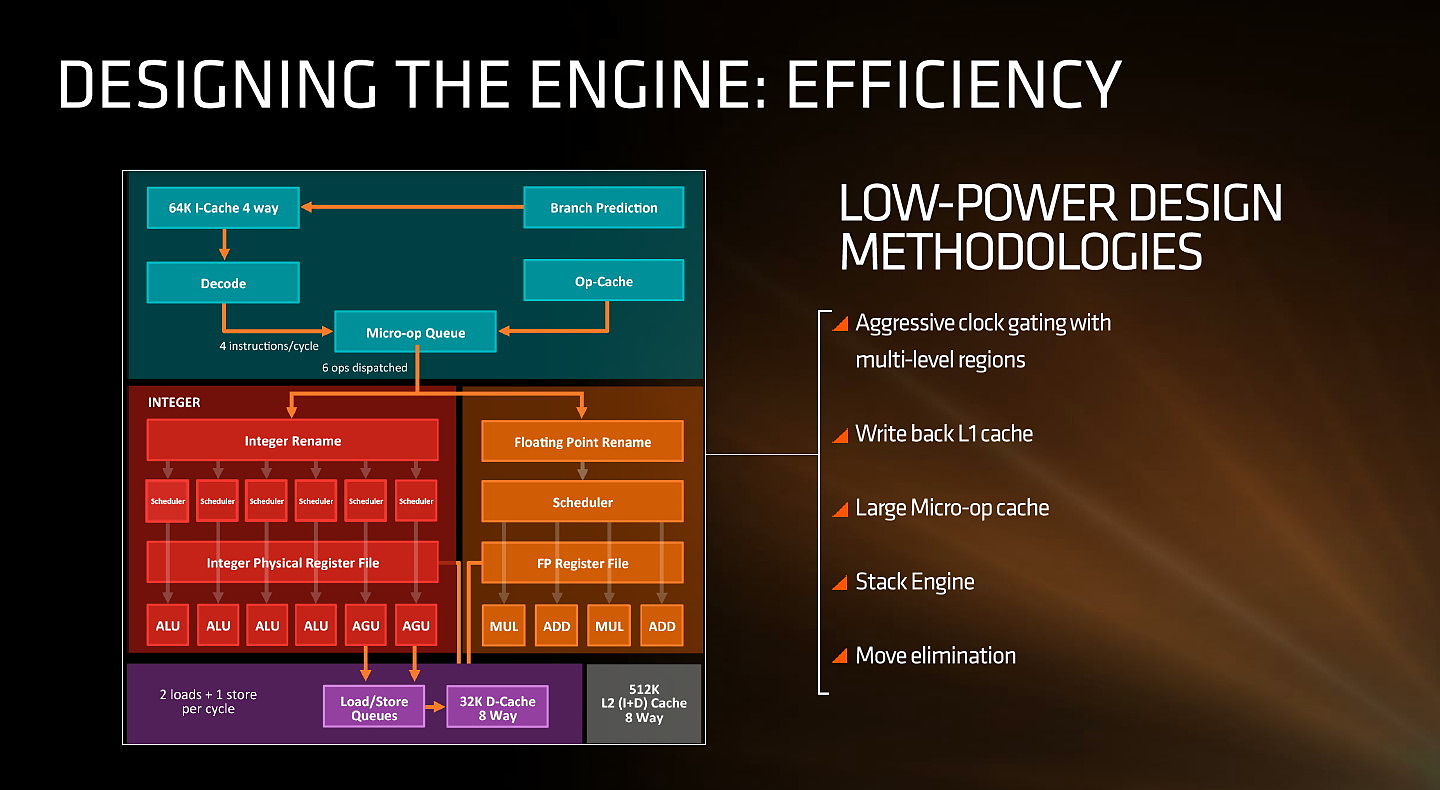

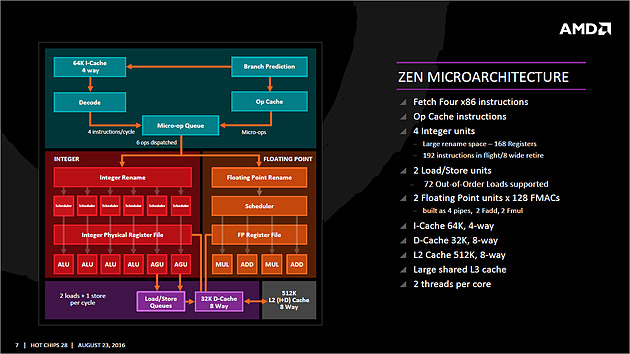

Zen dans les grandes lignes

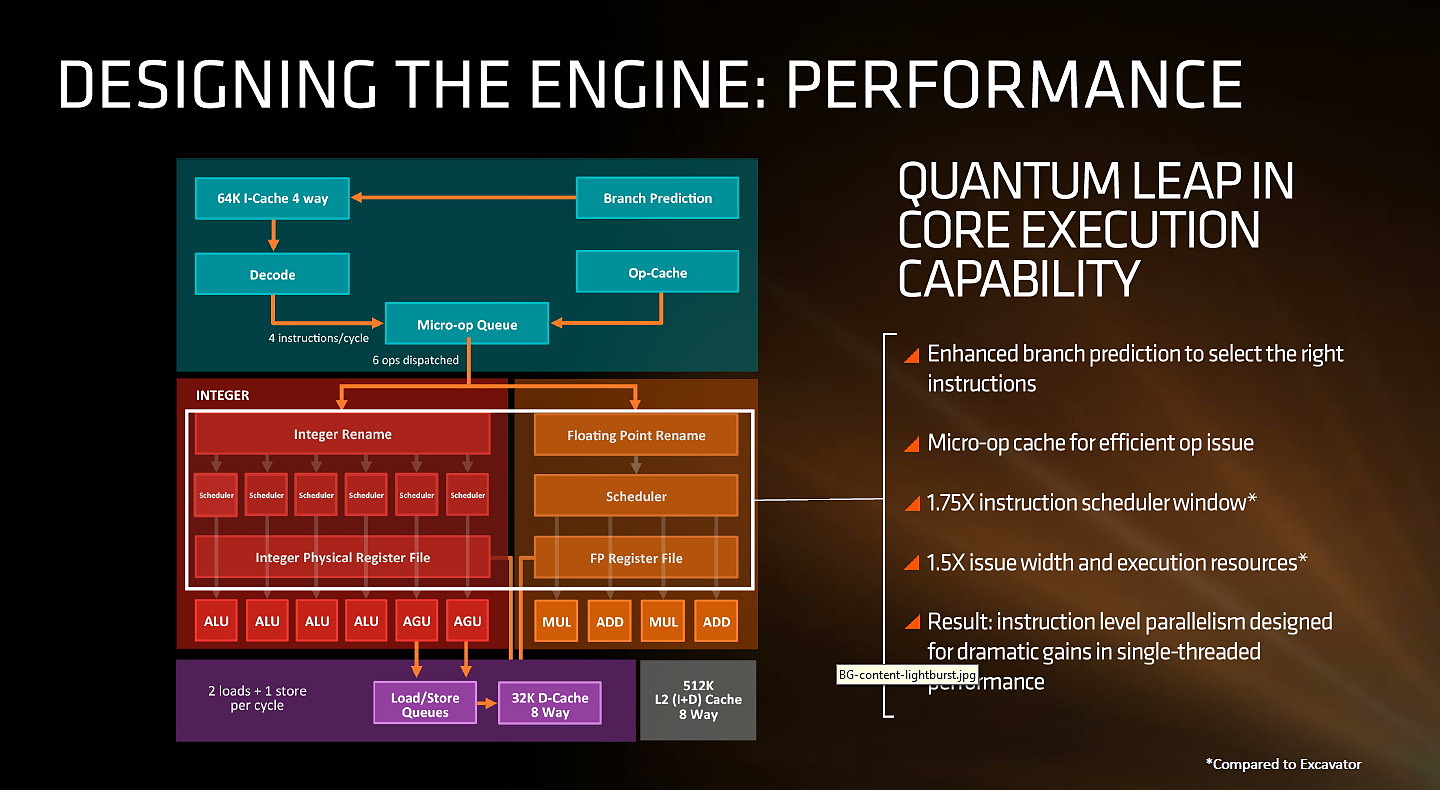

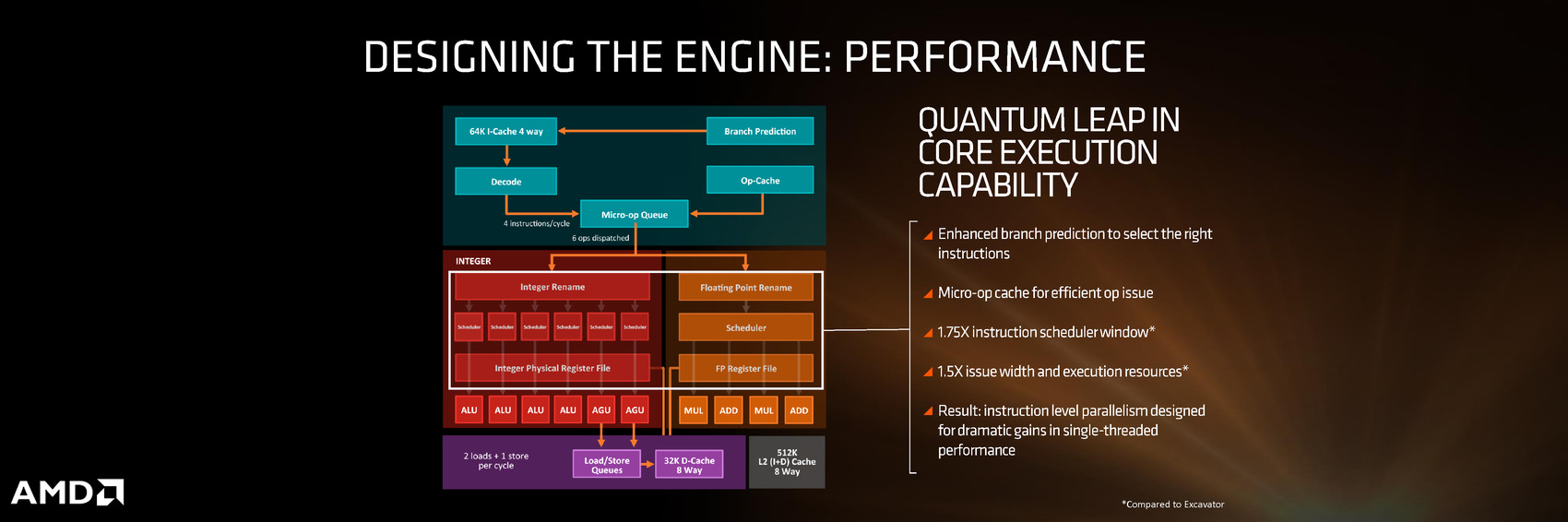

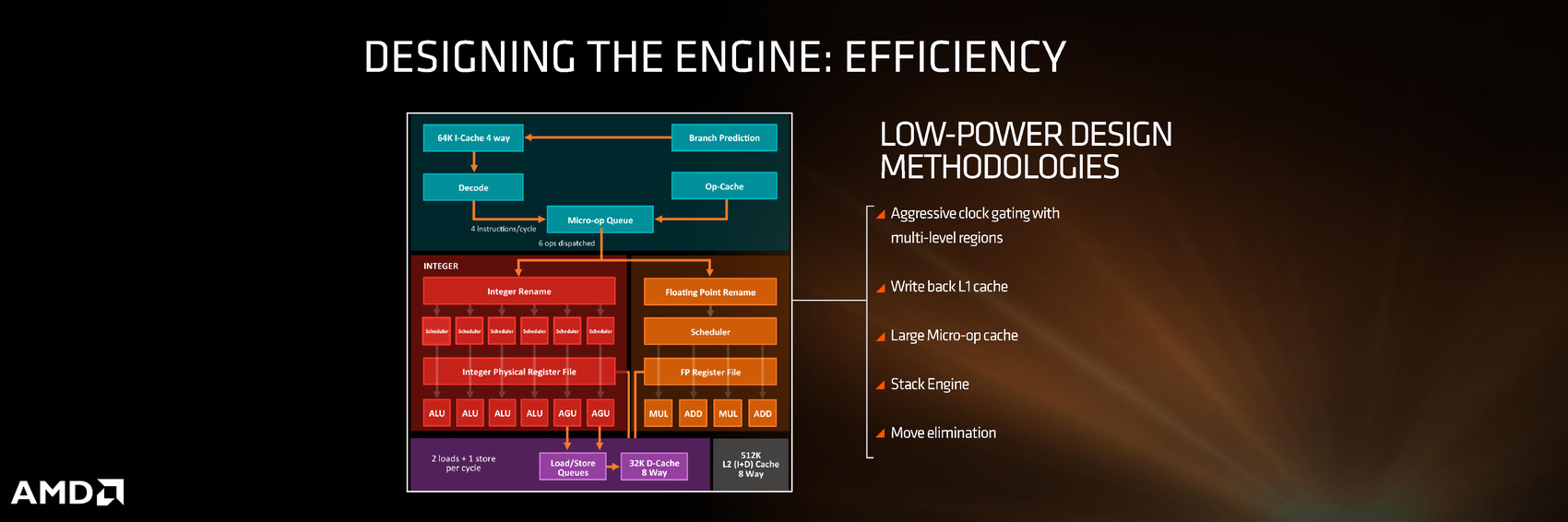

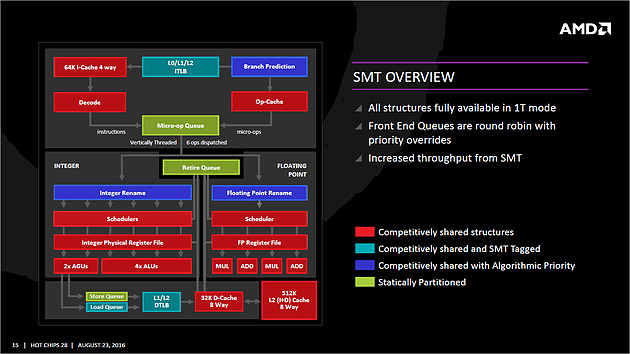

Ce schéma des grandes lignes avait déjà été présenté mais désormais AMD y accole beaucoup plus de détails. Pour rappel ce schéma commence en haut à droite, avec la partie Branch Prediction ou les instructions arrivent avant d'être décodées. Le point important à retenir est qu'AMD distingue clairement le chemin "Integer" (bloc rouge, opérations sur les nombres entiers, et toutes les opérations classiques comme les boucles, etc...) et le chemin "Floating Point" (bloc orange, opération sur les nombres à virgules). Ils disposent de chaque côté de leurs propres schedulers et Mike Clark, l'architecte en chef de Zen qui a effectué la présentation pour AMD les décrit comme des coprocesseurs indépendants.

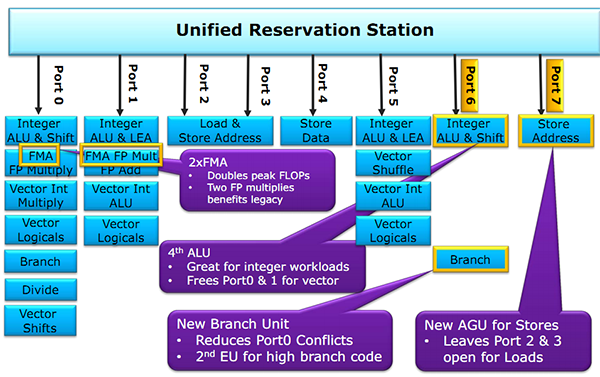

Schéma de fonctionnement des Haswell avec leurs ports d'exécution qui mélangent entiers et flottants sur les ports 0 et 1

Comme vous pouvez le voir ci dessus, il s'agit d'une implémentation qui diffère de ce que propose Intel sur ses architectures Core ou les instructions flottantes sont traitées sur les mêmes ports que les autres instructions (un port peut regrouper plusieurs unités d'execution), avec un scheduler unique. Par le passé, cette scission était nécessaire pour AMD, l'architecture Bulldozer regroupait dans un module deux blocs "Integer" et partageait un seul bloc "Floating Point". Ce qui ressemblait a une bonne idée s'est heurtée à de nombreux problèmes sur Bulldozer et ses dérivés. AMD a voulu conserver l'idée de la séparation tout en résolvant les problèmes restant, nous y reviendrons.

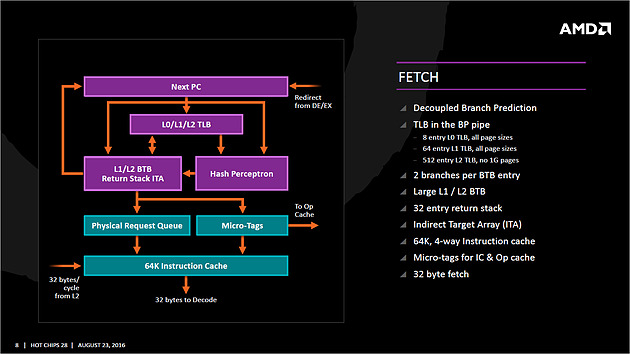

Le front-end

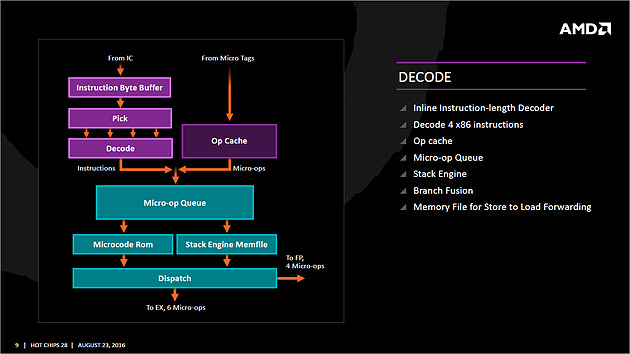

Tout en haut du graphique d'architecture précédent, on retrouve la partie du front end qui récupère (fetch) les instructions. Son rôle est d'extraire les instructions à exécuter, la prédiction de branchements (on parle de conditions, si elle est vraie, effectue ceci, sinon, effectue cela) tentant de déterminer lesquels seront nécessaires. Le TLB (un cache pour traduire les adresses mémoires virtuelles) est intégré et tout le mécanisme a été amélioré pour être plus efficace en ajoutant une table pour les adresses de retour des branches (l'endroit ou l'exécution doit se poursuivre à la fin de la branche, le bloc d'instruction exécuté après la condition).

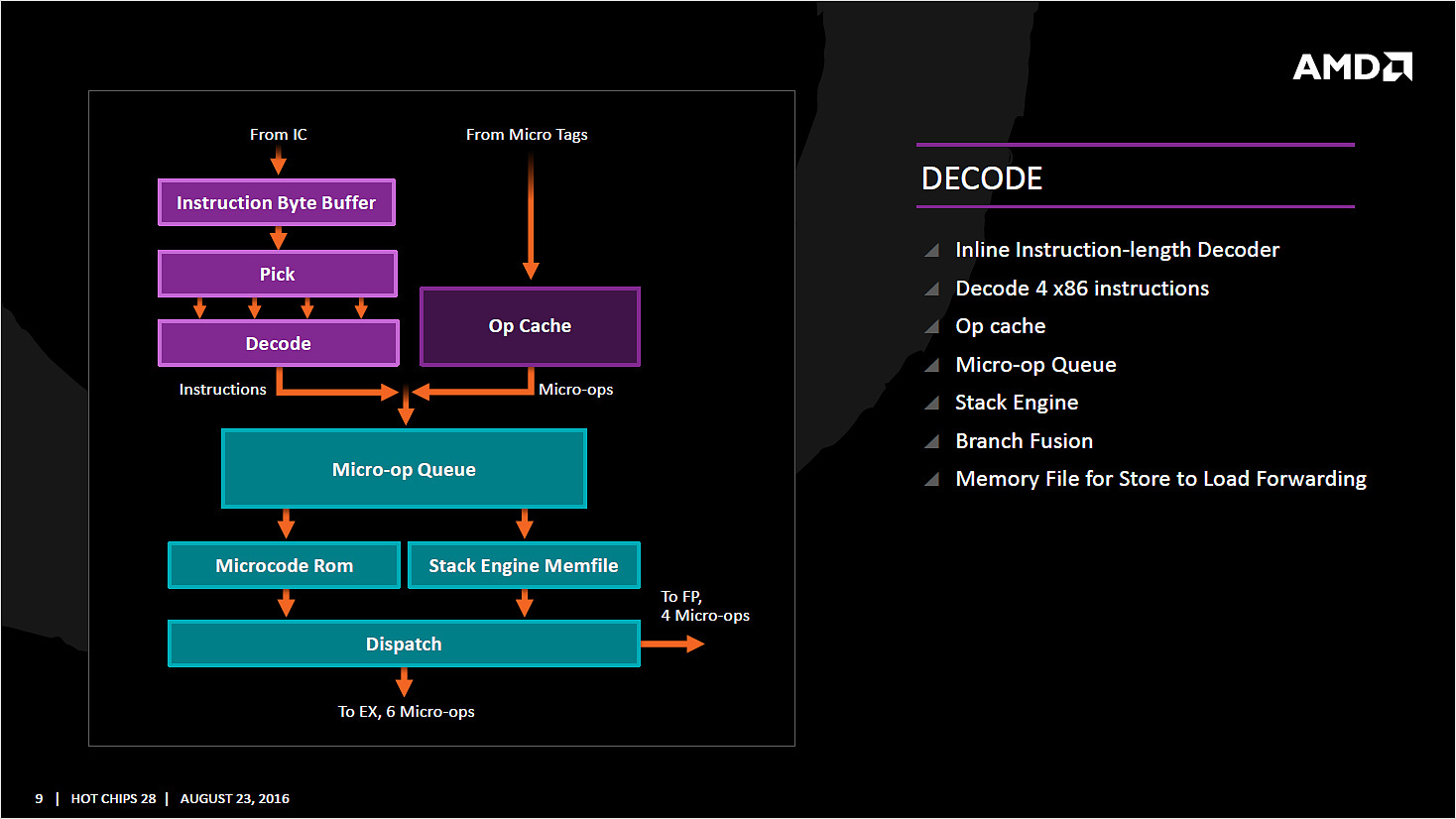

Les instructions récupérées vont ensuite être placées dans le cache d'instruction avant d'être décodées. C'est ici que les instructions x86 sont lues par le processeur, qui les transforme en des micro-opérations (micro-op) qui seront exécutées par la suite dans le pipeline. Les décodeurs sont capables de traiter jusque quatre instructions par cycle (c'est équivalent à ce que propose Intel sur Haswell et Skylake) qui sont transformés en jusque 6 micro-op. Certaines instructions peuvent être fusionnées en une seule micro-op (notamment celles de branchements), la encore les similarités avec ce que propose Intel sont fortes.

Comme chez Intel, AMD utilise un cache qui stocke la correspondance entre une instruction décodée et la micro opération qui en est issue. Le jeu d'instruction x86 comportant un bon millier d'instructions de tailles variables, l'idée est de garder en cache les instructions les plus récemment décodées en mémoire pour pouvoir les traduire automatiquement en micro-op sans repasser par la case décodage. Cela permet d'ajouter plusieurs micro-op supplémentaires par cycles a traiter.

Par rapport à ses architectures précédentes, AMD dit avoir "significativement" augmenté la taille de son Op Cache et que ce seul changement est responsable d'une grande partie des gains d'IPC et de consommation. On y retrouve une logique semblable aux évolutions architecturales que l'on a vu à la concurrence : le front end joue un rôle excessivement important dans les architectures x86 sur les performances du reste de la puce. Le voir soigné de la sorte est plutôt une bonne nouvelle pour Zen même si comme toujours nous réserverons notre jugement en pratique !

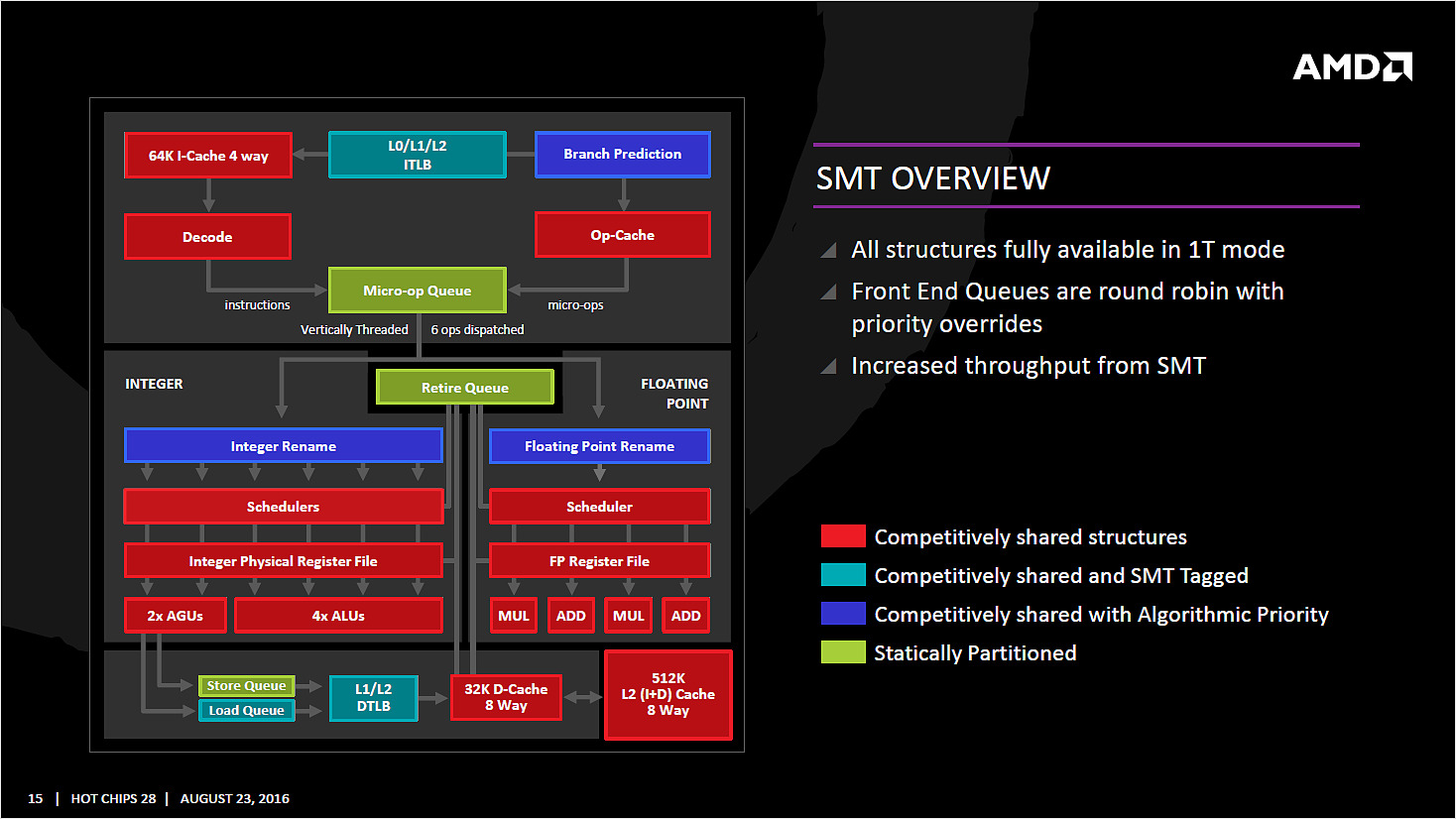

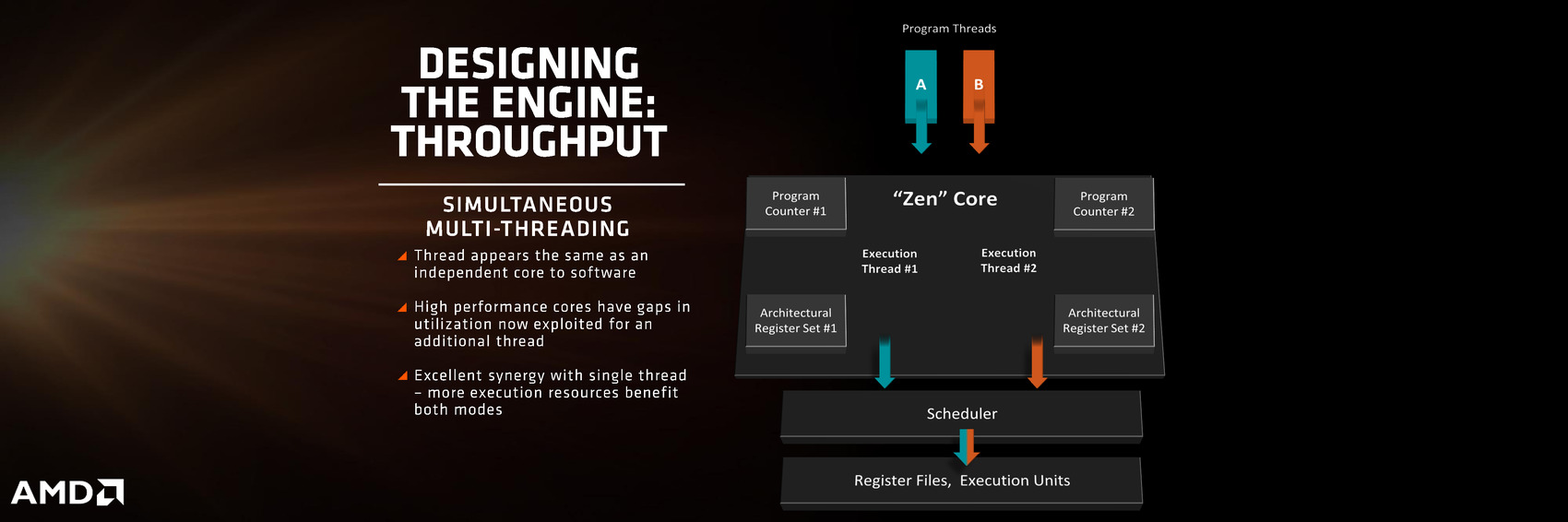

On notera que les micro-ops sont placées dans une file, ou plus exactement deux files. AMD implémente pour rappel le SMT (Simultaneous Multi Threading) qui permet de gérer deux threads par coeur (l'HyperThreading est le nom marketing de l'implémentation SMT d'Intel). La file de micro-op est ainsi scindée en deux (ce qui est identique à ce que fait Intel pour Sandy Bridge et Skylake, Haswell ayant utilisé une file commune). Les instructions vont enfin être dispatchées vers les ports. En pratique 10 micro ops peuvent être envoyées (6 vers la partie "Integer" de la puce, 4 vers la partie "Floating Point"), soit deux de plus que sur Haswell (Intel ne nous a pas donné l'information pour Skylake).

Les unités d'executions

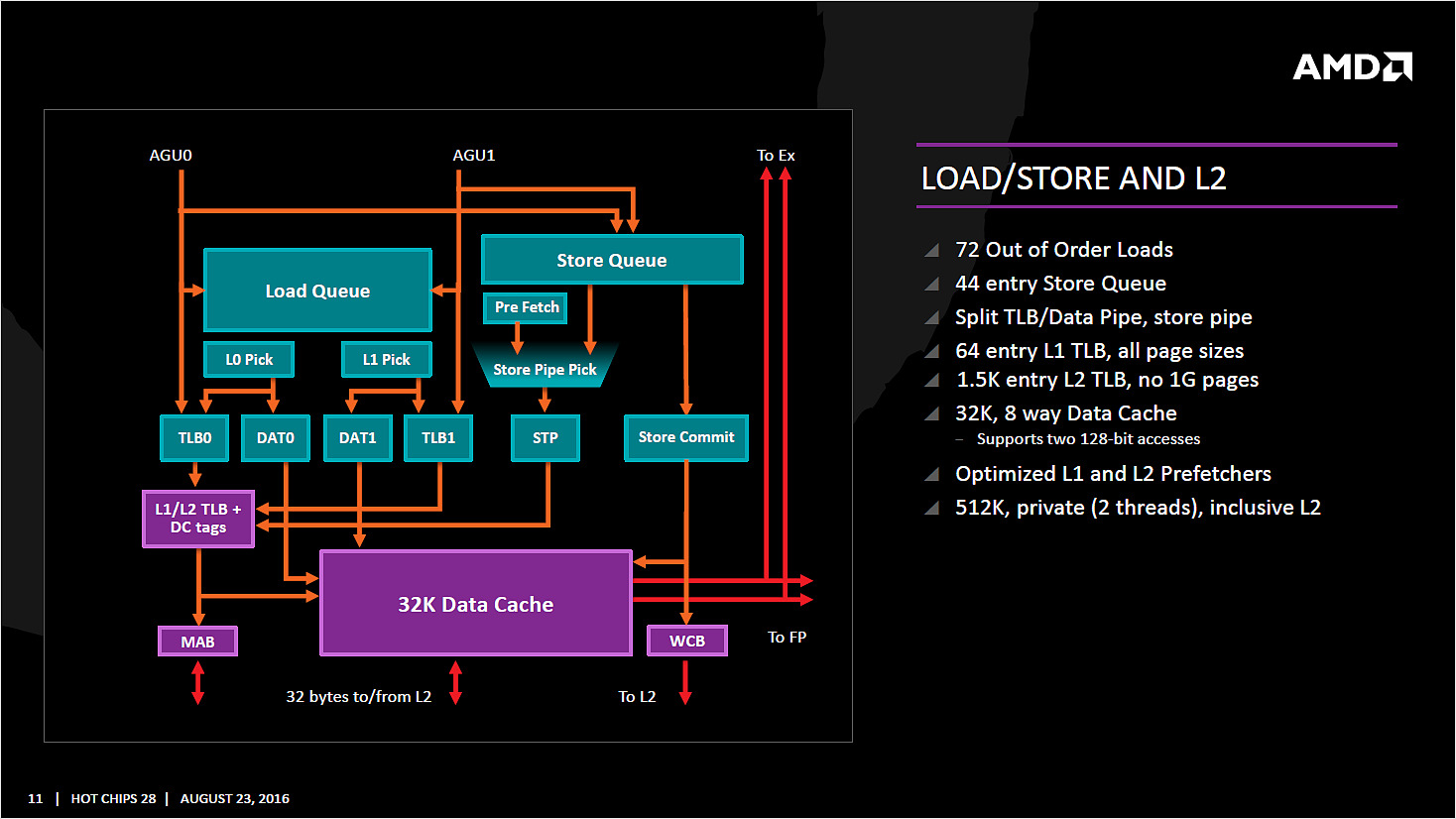

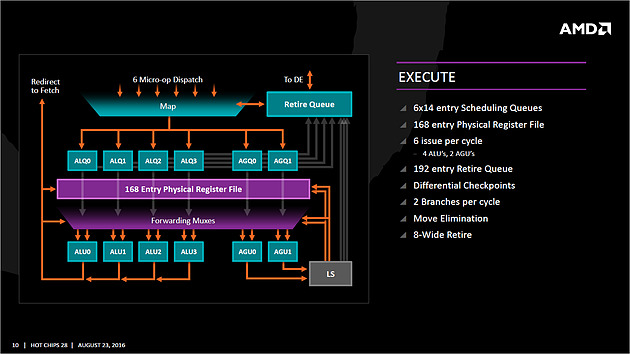

Les micro-op vont être dispatchées vers 6 files d'exécution (l'équivalent des ports d'Intel) dont la taille a été significativement augmentée (14 entrées par file, soit 84 pour cette partie de la puce, Skylake en compte 97 en tout mais il faut ajouter celles dédiées aux opérations FP, nous y reviendrons). AMD dispose de deux files dédiées aux opérations mémoires (AGU, adress génération unit) qui asservissent un système de lecture/écriture mémoire (Load/Store) sur lequel on reviendra. Quatre files sont dédiées aux instructions de "calcul" et de branchements. AMD les appelle ALU sur son schéma, il s'agit en pratique d'une série d'unités d'executions. Chaque ALU regroupe au minimum la possibilité de traiter les instructions logiques de base. AMD ne le détaille pas sur son schéma, mais d'autres unités sont présentes.

Le constructeur nous a confirmé que deux des ALU contiennent une unité dédiée au branchement, une ALU contient une unité gérant les divisions, une ALU contient une unité gérant les multiplications entières, et enfin une ALU contient une unité dédié au CRC32. AMD ne détaille pas la répartition exacte des unités sur les ALU, mais on apprécie les détails supplémentaires qui ont été donnés. L'efficacité de ces unités dépendra en grande partie de la capacité du front-end a les alimenter, mais sur le papier là encore, le design semble largement adéquat.

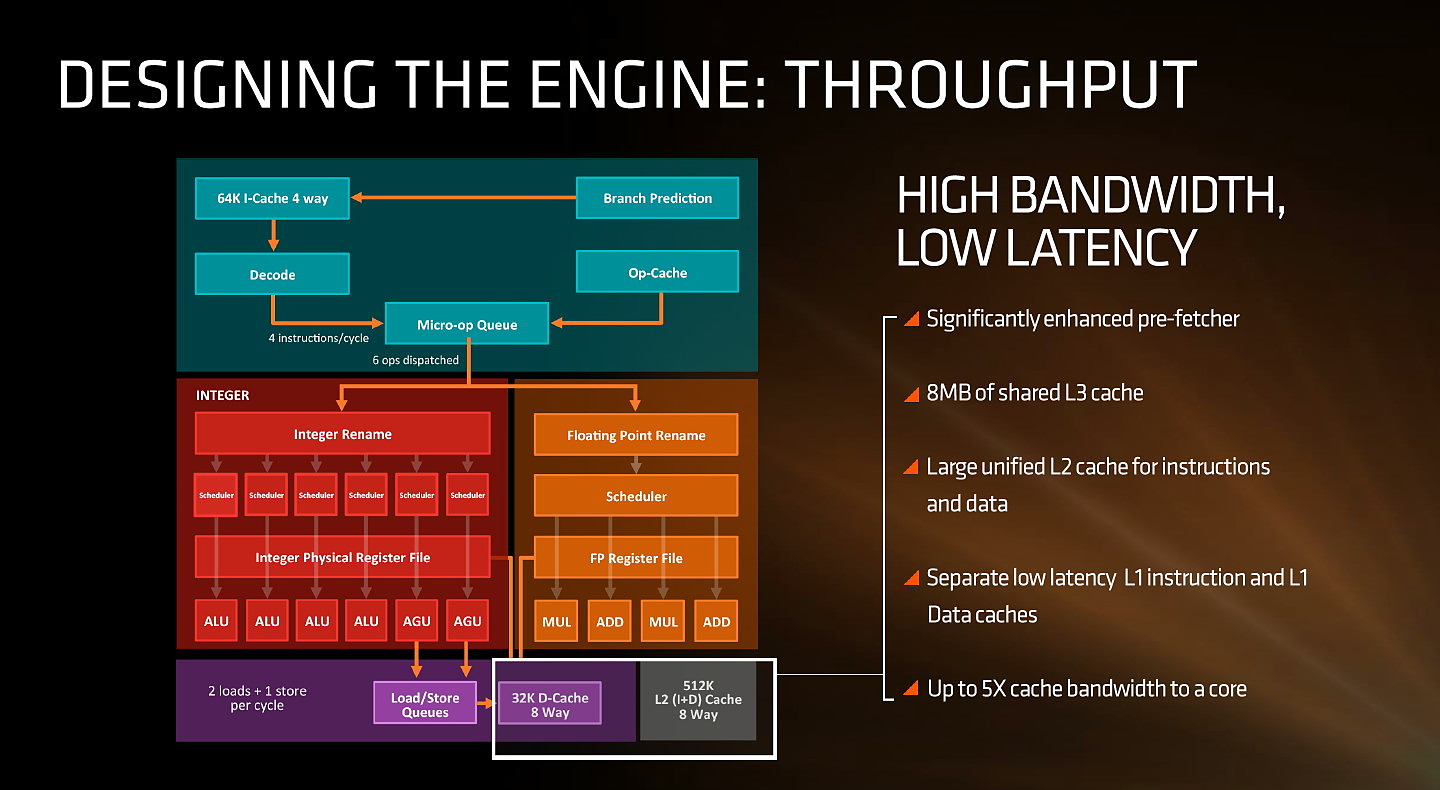

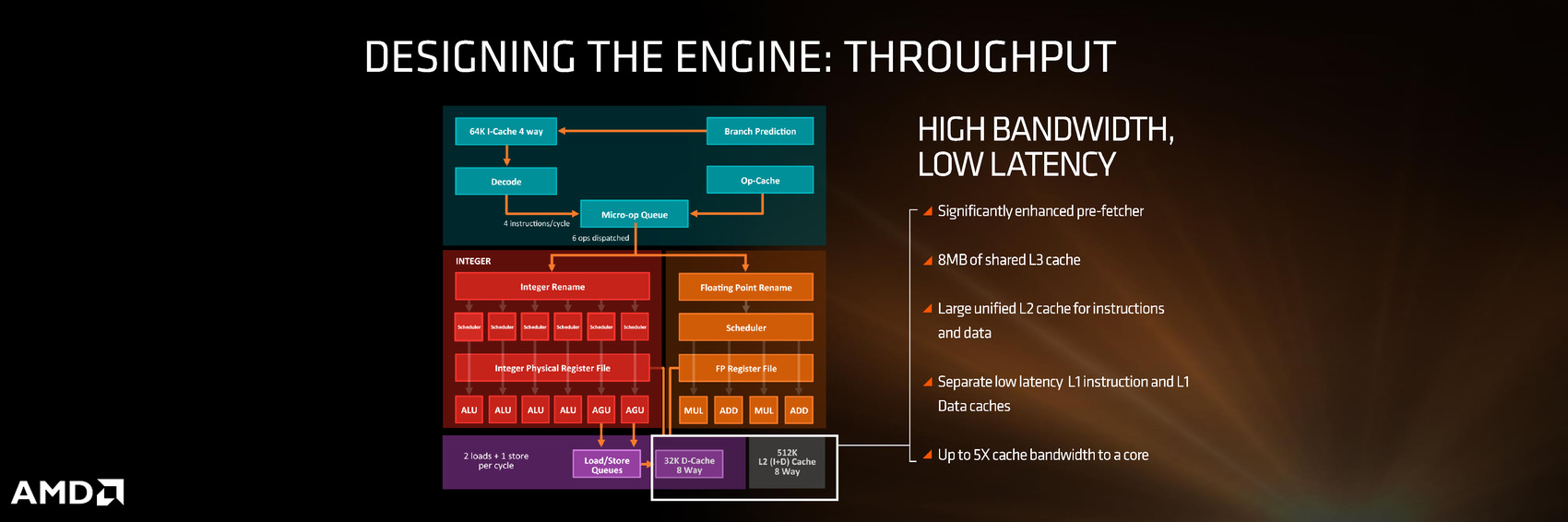

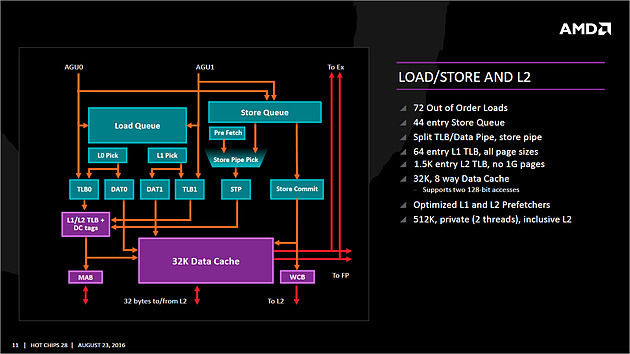

Comme nous le disions, les AGU asservissent les unités qui lisent et écrivent les données dans le sous système de cache. On retrouve des longueurs de files comparables à ce que l'on a chez le concurrent (72/44 pour Zen, 72/42 pour Haswell et 72/56 pour Skylake). Pour les chargements, AMD rentre dans le détail en indiquant qu'un des autres points faibles de ses architectures précédentes était lié aux opérations de chargement mémoire. Deux accès séparés 128 bits en lecture sont désormais possibles, et les unités peuvent accéder en simultanée au cache L1 et au cache TLB pour maximiser le débit, et ainsi streamer les données rapidement du cache L2 vers le L1.

L'efficacité des prefetchers (qui tentent de récupérer les informations en avance du moment ou le processeur en aura besoin) est indiquée comme meilleure et là encore il faudra attendre pour en savoir plus. Si AMD ne donne pas la rapidité de ses caches, il nous a été confirmé que la bande passante pratique est significativement plus rapide désormais, ce qu'on ne manquera pas de vérifier.

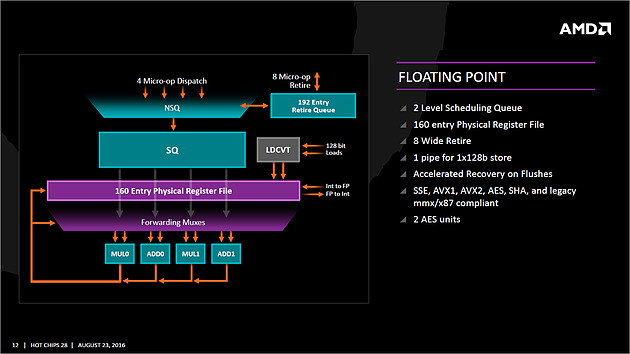

Si l'on revient en arrière, le dispatcher de micro-op pouvait envoyer jusque 6 instructions vers la partie Integer, et quatre vers la partie Floating point. Le scheduler dédié aux unités flottantes dispose ici de 96 entrées ce qui nous donne un total de 180 entrées par coeur (contre 97 pour Skylake). Il s'agit même en pratique d'un double scheduler.

C'était l'un des points faibles du design séparé que l'on évoquait plus haut : sur Bulldozer un scheduler trop petit sur la partie FP pouvait arriver à bloquer la partie Integer du CPU, un cas qui visiblement était assez fréquent. Avec un double scheduler, AMD dit avoir résolu le problème en pratique. On disposerais désormais bel et bien de deux blocs réellement indépendants pouvant travailler en parallèle (et ne se bloquant plus l'un l'autre).

Quatre unités d'exécution FP 128 bits sont donc présentes, deux dédiées plus spécifiquement aux multiplications et deux aux additions. Elles peuvent être combinées pour réaliser jusque 2 FMA 128 bits en parallèle par cycle. Sur ce point AMD est en retrait puisque Haswell pouvait effectuer deux FMA 256 bits par cycle. Il faudra voir l'impact pratique sur les performances, mais sur de micro benchmarks ou des cas spécifiques, ce sera un point limitant pour Zen.

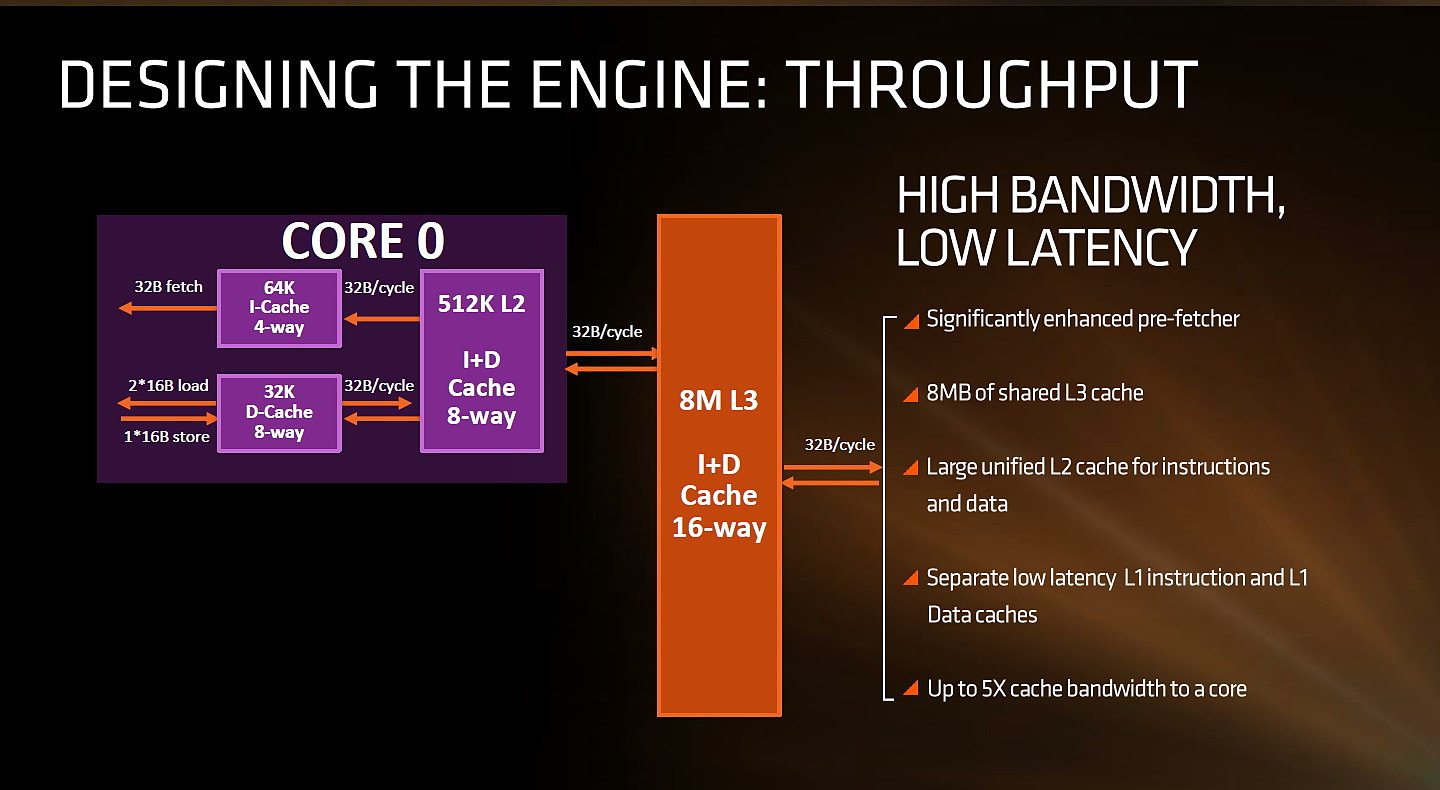

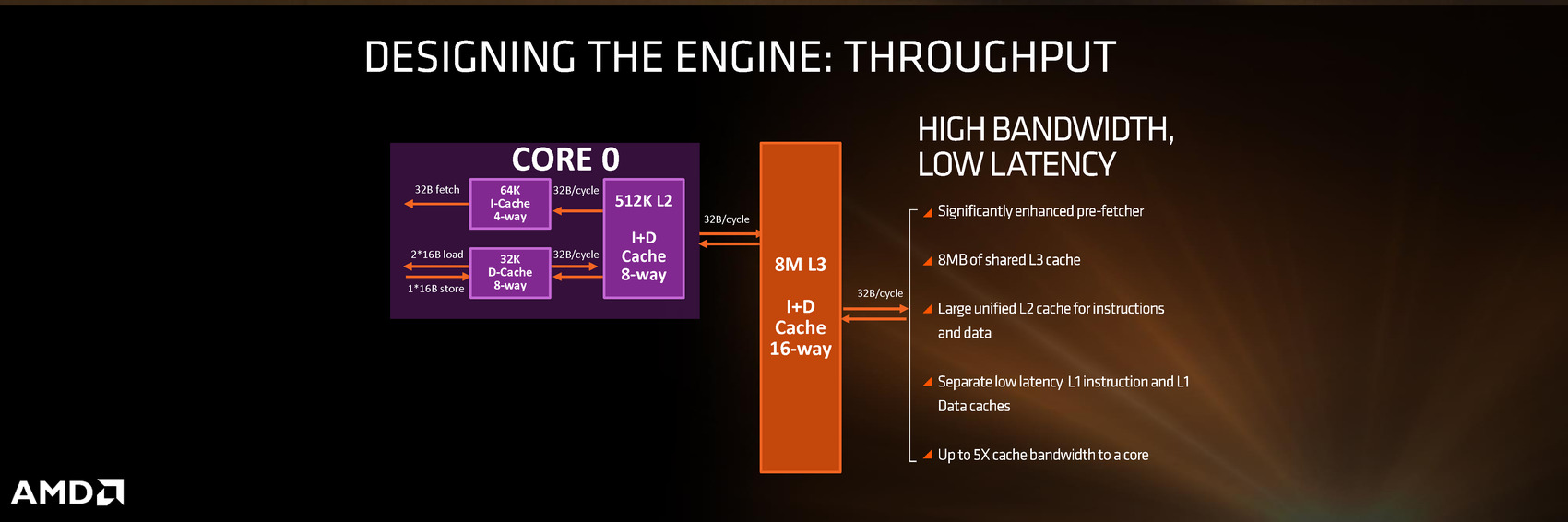

Les caches mémoires

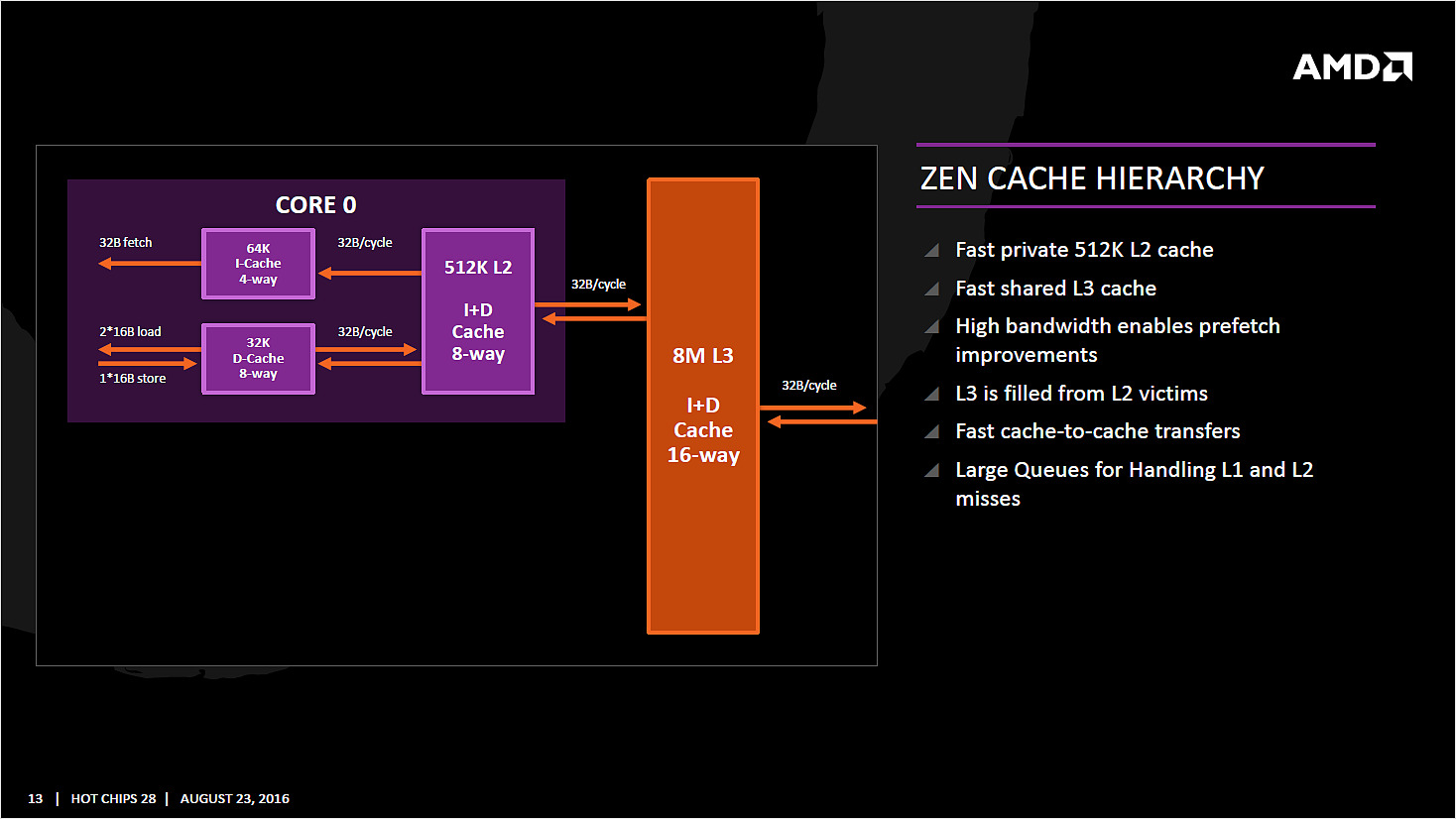

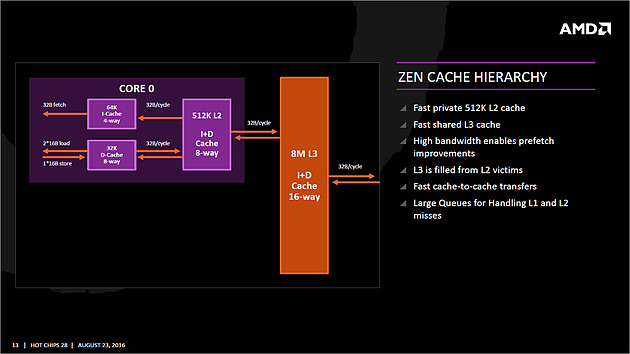

Sortons de la partie exécution pour regarder plus précisément les caches mémoires. AMD a choisi d'utiliser un cache L1 write back au lieu du write through utilisé précédemment, s'alignant là aussi sur ce que fait Intel. Cela devrait assurer une bien meilleure bande passante mémoire pour le L1 dont la taille est de 32 Ko. Chaque coeur dispose en prime d'un cache L2 de 512 Ko (le double de Skylake), et l'on retrouve un cache L3 partagé de 8 Mo assez spécial. Il est en prime (principalement) exclusif par rapport au cache L2.

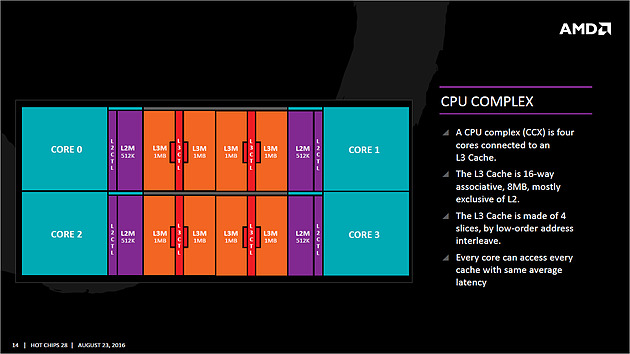

Les blocs de coeurs

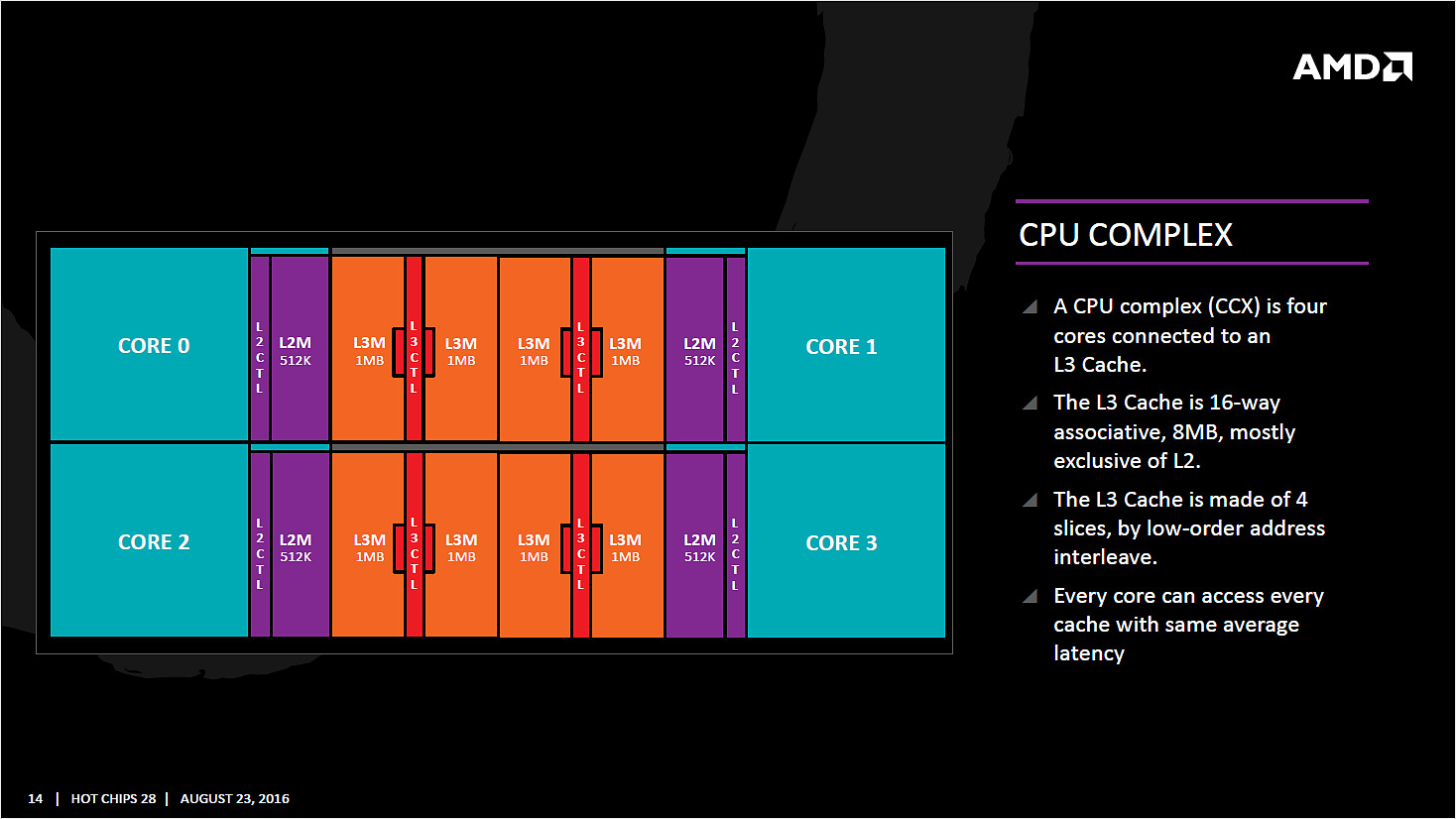

C'est l'un des rares détails d'un peu plus haut niveau qu'aura partagé AMD : les coeurs Zen sont regroupés par blocs de quatre. Chaque coeur comme indiqué plus haut est relié a son propre cache L2 de 512 Ko, et également à 2 Mo de cache L3. Ces quatre partitions de cache L3 sont reliées ensemble et chaque coeur peut accéder a chacune des partitions. Selon l'emplacement des données, la latence ne sera pas la même, même si AMD n'a pas voulu quantifier l'éventuelle différence (on admirera la manière dont AMD a tenté de détourner le sujet en parlant de latence moyenne !). Chaque CCX (le nom donné au groupe) dispose donc au total de 8 Mo de cache, et AMD peut ainsi construire des puces utilisant plusieurs modules CCX.

Ces derniers sont reliés point à point au reste du système (notamment au contrôleur mémoire, etc) par un data fabric, un système de bus interne. Dans le cas d'une puce disposant de deux CCX, un coeur souhaitant accéder à la mémoire L3 de l'autre bloc CCX passera par les blocs en amont du contrôleur mémoire, avec un système de cohérence type MOESI. Il n'y a pas de lien direct point à point entre les CCX à ce qui nous a été indiqué, en tout cas pour ce qui concerne les premières versions de Zen (les déclinaisons serveurs pourraient être reliées différemment). On notera enfin que les coeurs/L2 et le L3 disposent d'un plan de fréquence séparé.

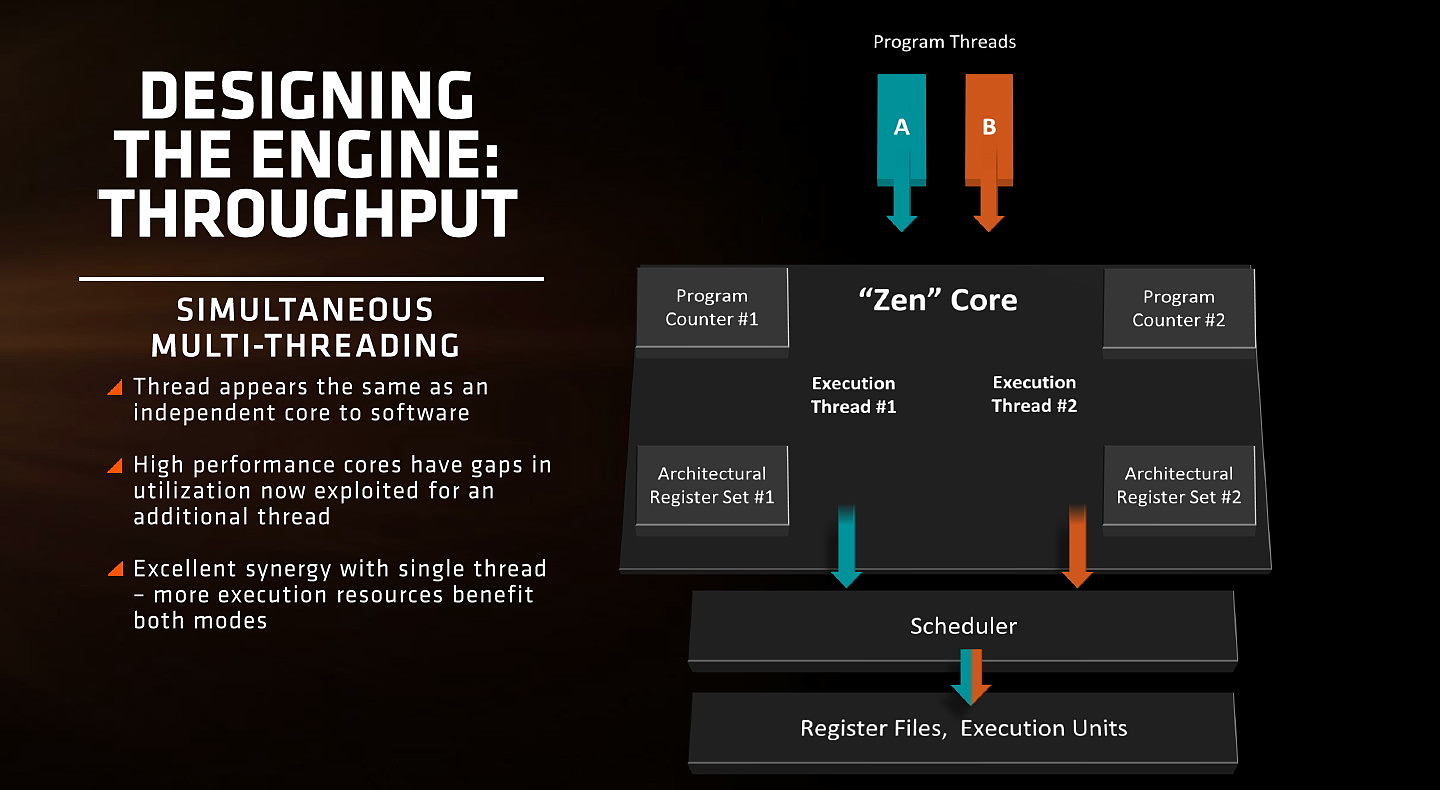

Un dernier mot sur le Simultaneous Multi Threading

AMD a terminé sa présentation en indiquant avec beaucoup de précisions la manière dont les blocs sont partagés lorsque l'on utilise le SMT. En pratique il n'y a que très peu de cas ou AMD partitionne en deux des buffers pour chacun des threads. C'est le cas, nous l'avons vu plus haut, de la file de micro-op principale, et l'on notera que c'est le cas aussi pour la file d'écriture vers les caches. Les autres structures sont partagées entre les threads en fonction des besoins, ce qui est plutôt une bonne nouvelle là aussi.

En résumé

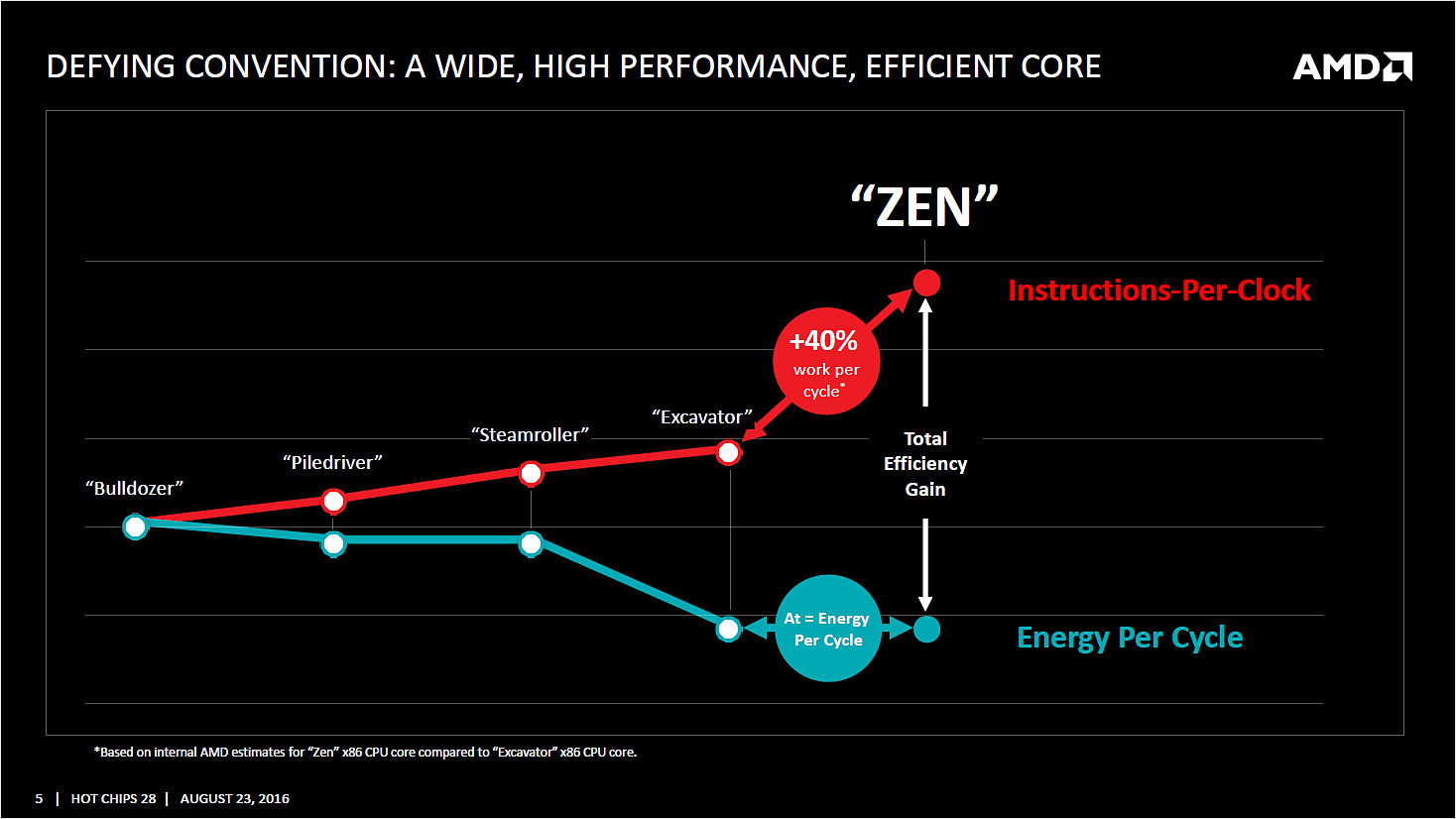

Cette présentation de Hot Chips était l'une des plus attendues, et l'on est obligé de dire que sur le papier au moins, AMD semble proposer une architecture vastement supérieure à ce qu'il proposait auparavant avec ses coeurs Jaguar ou Excavator. Certains diront que c'était un moindre mal, mais les changements sont conséquents.

Sur le papier, le travail important réalisé sur le front-end nous rappelle de nombreux choix également effectués par Intel pour son architecture Core, ce qui semble être une très bonne chose pour les performances et la consommation.

AMD garde un design différent pour la partie exécution en scindant en deux les ports "Integer" et "FPU". Un design qui n'avait pas particulièrement réussi aux modules de Bulldozer, mais AMD semble avoir appris des problèmes que cette partition avait causé. Il faudra voir si en pratique cette séparation portera enfin les fruits attendus.

De la même manière l'architecture des caches semble avoir été revue dans le bon sens, le passage au write back pour le L1 devrait augmenter largement sa bande passante, et le reste des caches est confortablement dimensionné.

Sur le papier, le retard architectural d'AMD semble en très grande partie comblé, et il n'y a que sur le choix des unités 128 bits en virgule flottante que l'on émettra un bémol.

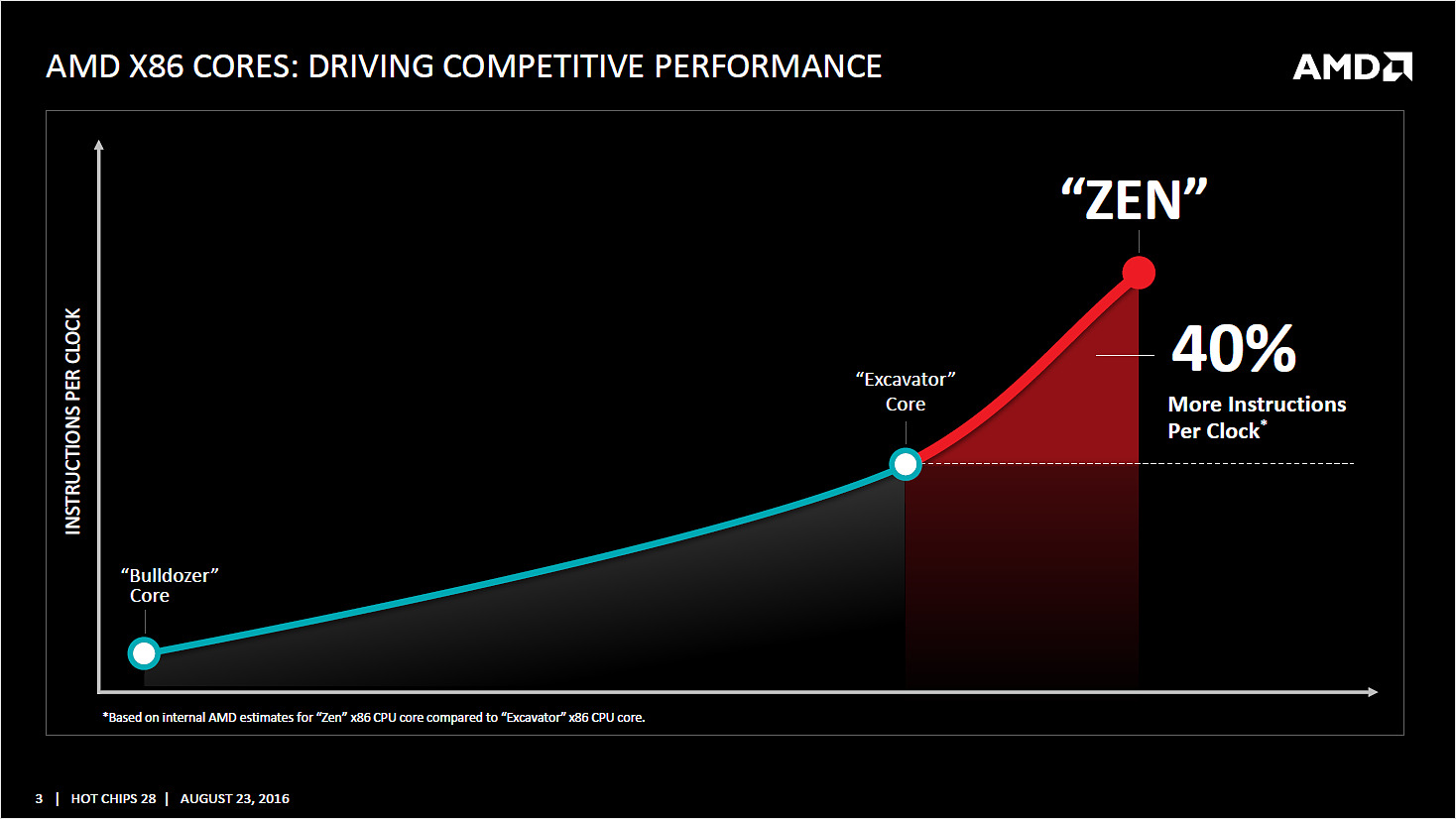

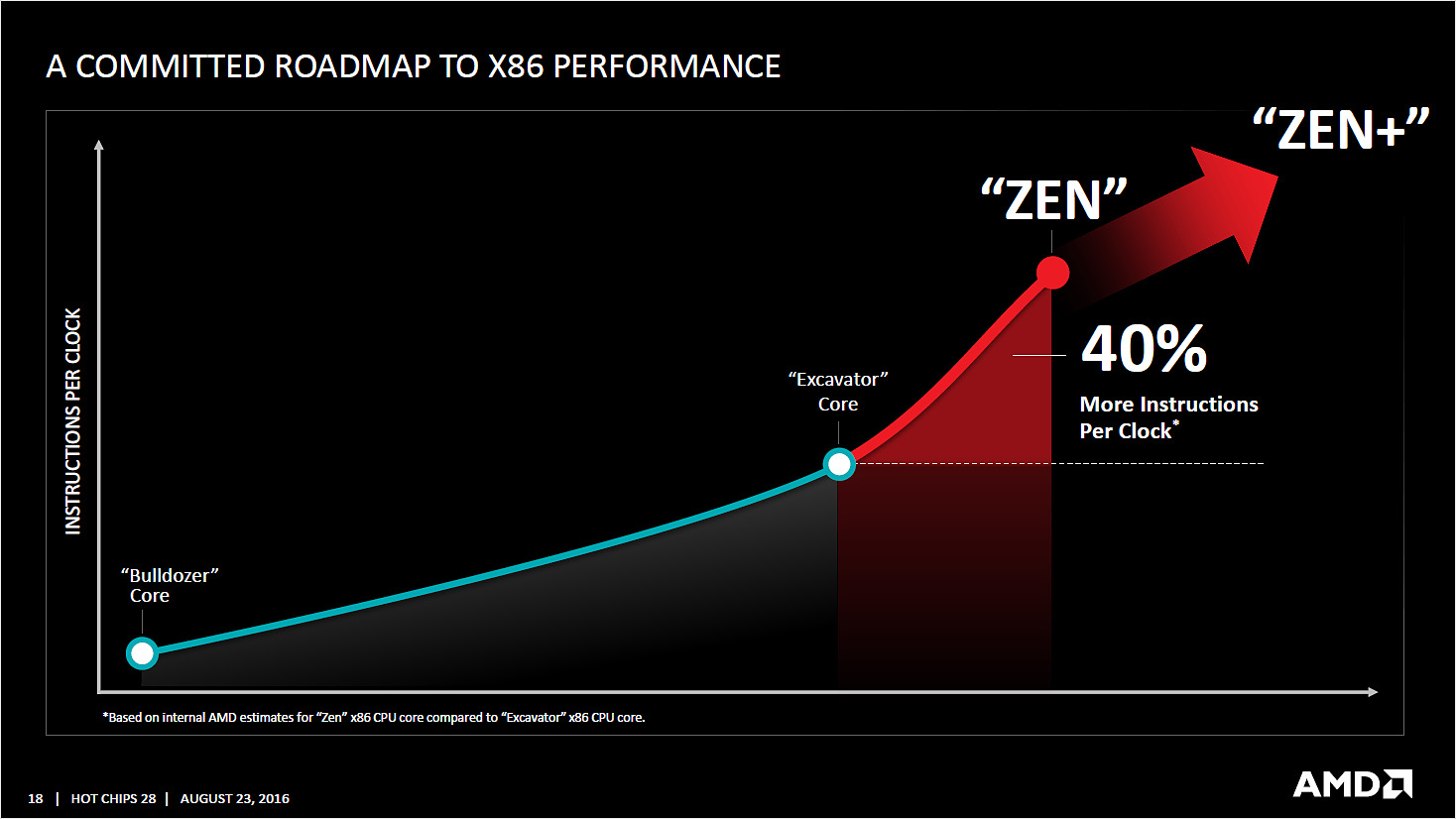

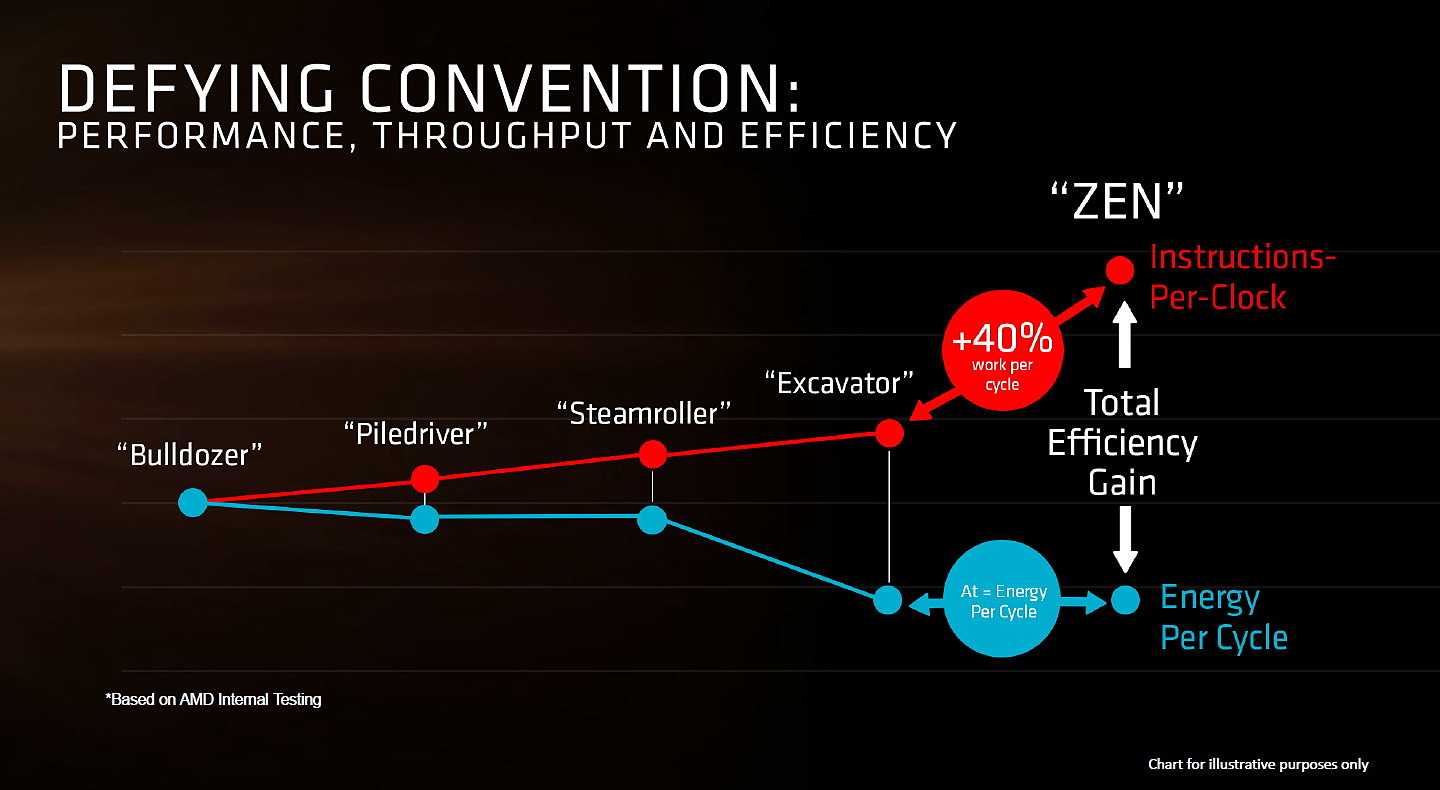

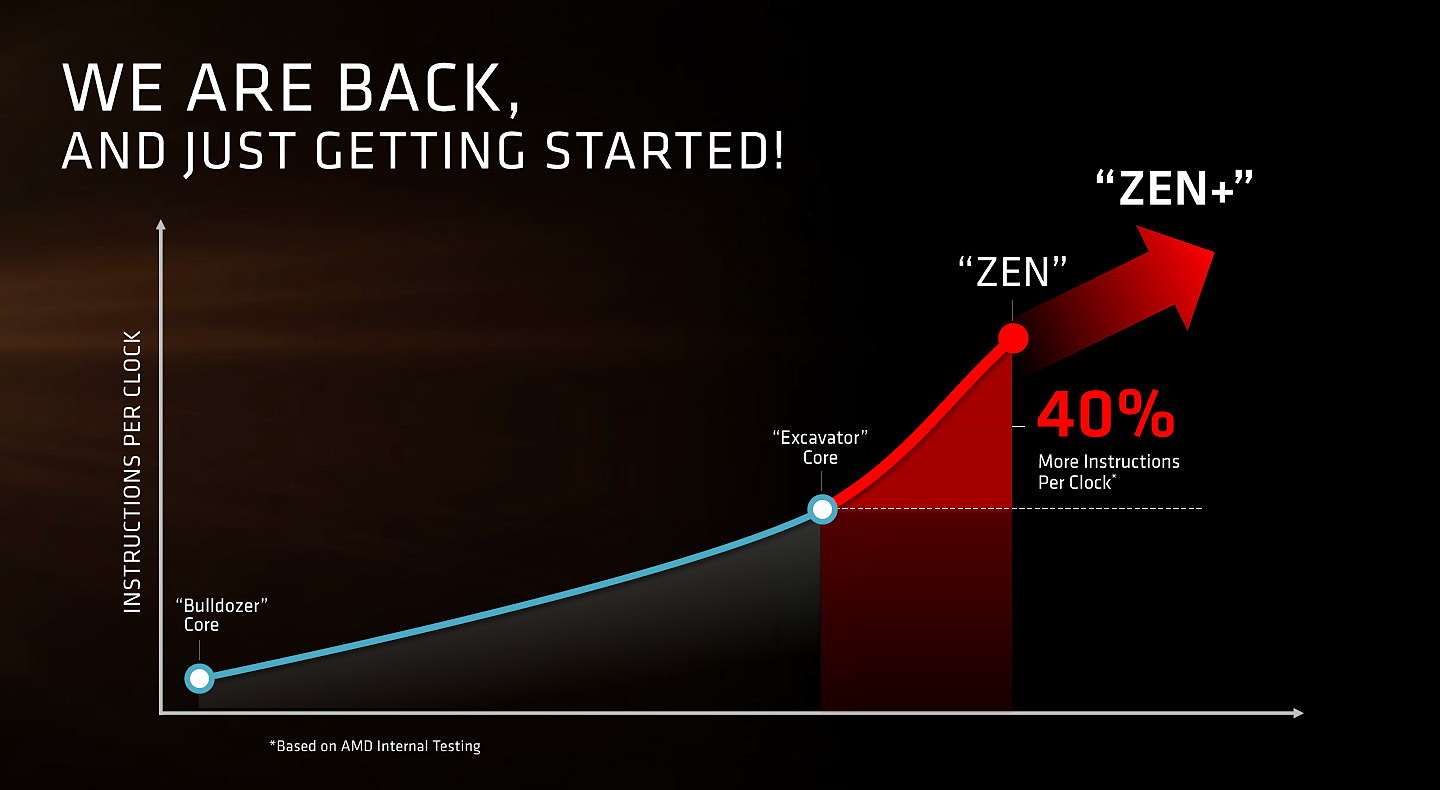

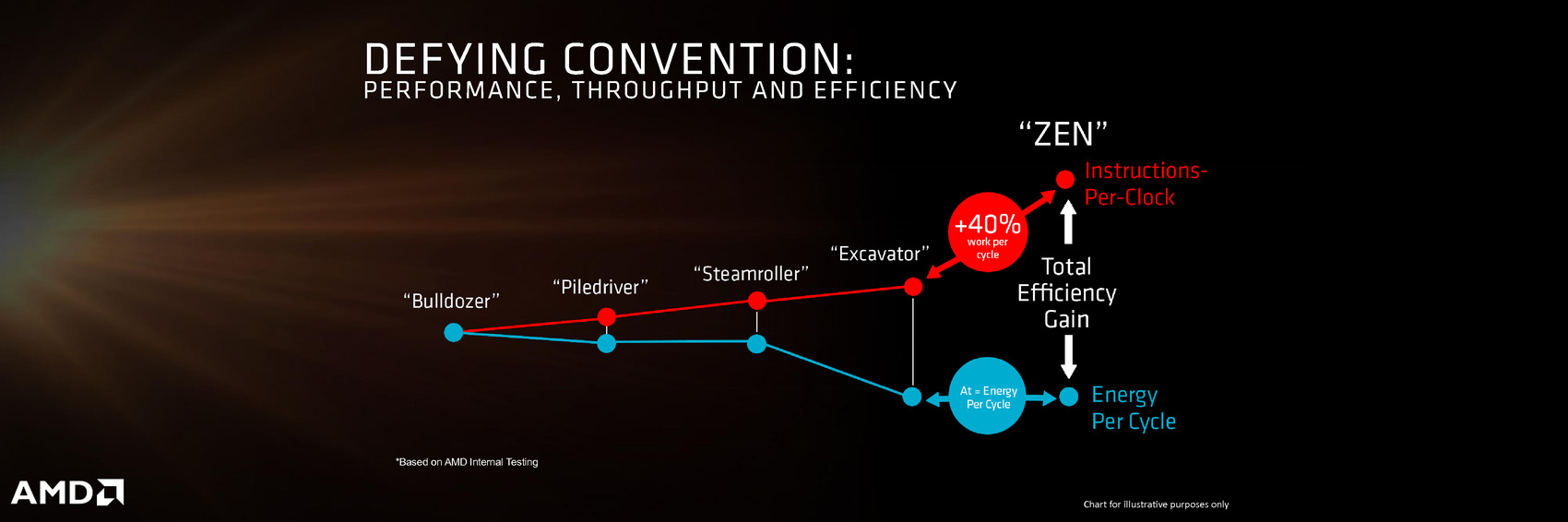

Reste qu'entre la théorie et la pratique, de nombreuses choses peuvent jouer et si AMD martèle avoir fait progresser de 40% l'IPC par rapport à son architecture précédente, on rappellera que le chiffre est obtenu en comptant l'effet de l'intégration du Simultaneous Multi Threading. Sur ce qui est des performances monothread, point primordial, rien n'a été indiqué. Le fait que la notion de coeur ait été malmenée par Bulldozer et Excavator complique de toute manière l'interprétation de ces chiffres.

Comme toujours, seuls des tests pratiques pourront nous donner la réalité de la situation. Dans l'attente d'autres détails, que ce soit sur la partie uncore, et bien évidemment sur les fréquences et quantités de coeurs embarqués (sans parler des prix), nous n'irons pas plus loin dans les prédictions.

Dans tous les cas, le retour d'un semblant de concurrence dans le marché du x86 ne serait pas pour nous déplaire !

Vous pouvez retrouver ci dessous l'intégralité de la présentation d'AMD :

AMD en dit un peu plus sur Zen

Lors d'une présentation organisée hier soir en marge du forum technologique d'Intel, AMD est revenu sur sa future architecture Zen. Mark Papermaster, Chief Technology Officer, a dévoilé quelques détails de plus sur ces processeurs très attendus.

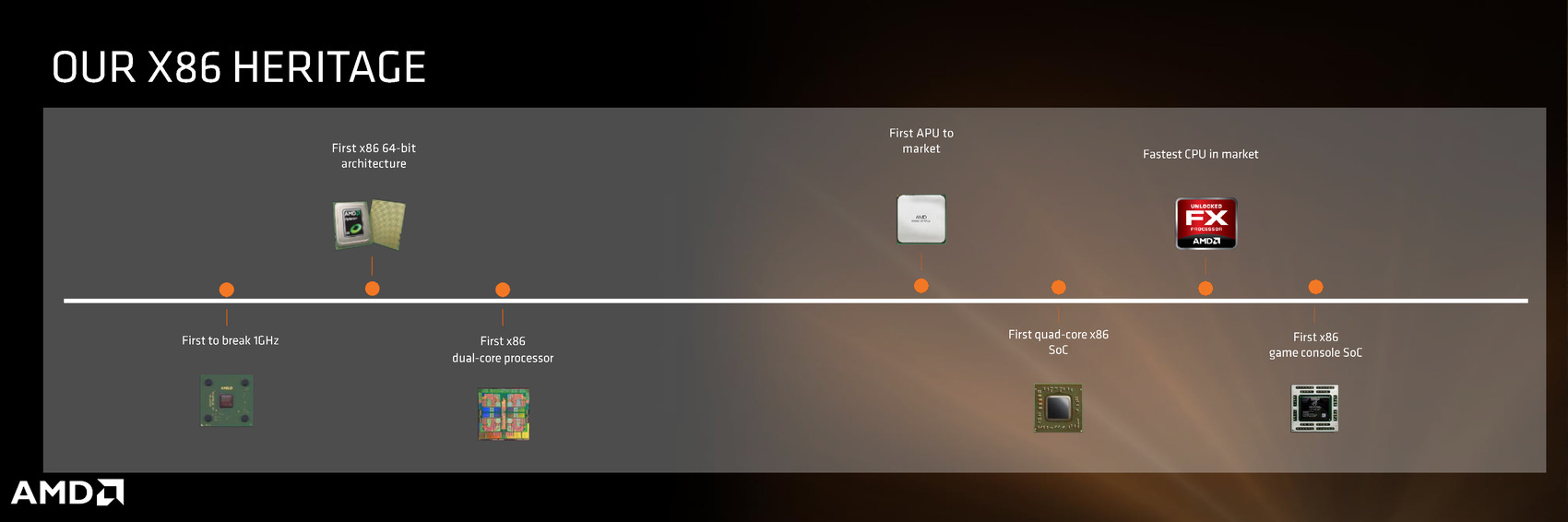

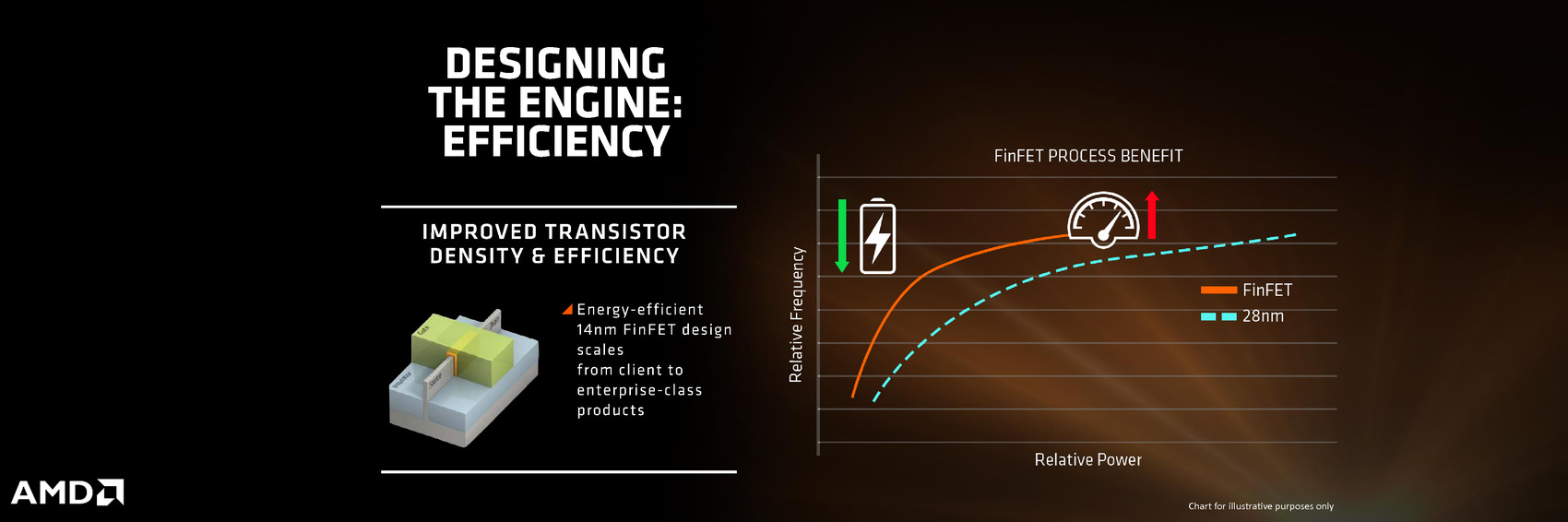

De nombreux espoirs reposent sur cette architecture CPU Zen et, à l'approche de sa concrétisation, AMD va progressivement dévoiler de plus en plus de détails. AMD insiste lourdement sur le fait d'être reparti d'une feuille blanche, ce qui arrive de moins en moins souvent dans l'industrie, les évolutions étant en général progressives. Mais pour qu'AMD revienne dans la course une rupture radicale était nécessaire par rapport à Bulldozer et ses dérivés.

AMD réaffirme ainsi toute sa confiance dans l'architecture Zen et estime pouvoir revenir dans le segment x86 haute performances, allant même jusqu'à parler de sa "zone de confort historique". Une forte progression du taux d'IPC, +40%, et du rendement énergétique devrait permettre à Zen de mieux se positionner face aux CPU d'Intel.

Pour pousser autant le taux d'IPC, comme nous le savons déjà, Zen abandonne la structure de module et a recours au Simultaneous Multi-Threading (SMT), dont l'HyperThreading en est l'implémentation d'Intel. Mais ce n'est évidemment pas tout. Il est également question d'une nette amélioration du front-end. La prédiction de branchement évolue, comme c'est le cas à chaque nouvelle architecture CPU mais une modification plus importante concerne l'ajout d'un cache pour les micro-ops dont étaient dépourvus ses précédents CPU, ce qui pouvait donner un avantage important au front-end des CPU Intel.

AMD communique peu de détails sur les buffers exploités par ce nouveau front-end mais indique que la fenêtre d'instructions pour le scheduler a été élargie de 75%, ce qui va également participer à faire progresser le taux d'IPC. AMD n'a cependant toujours pas clarifié quelle part de ce gain d'IPC concernera le mono-thread et indique que ces détails seront communiqués plus tard.

Pour accompagner ce renforcement du front-end, Zen se muscle également côté unité d'exécution. Contrairement à ce que fait Intel, AMD semble avoir conservé de Bulldozer une séparation entre l'ordonnancement des opérations sur les entiers et sur les flottants. Du côté des entiers on retrouve 6 ports d'exécution (4 ALU + 2 AGU) contre 4 précédemment (4 ALU/AGU). Du côté des flottants le schéma laisse entrevoir 2 FMUL et 2 FADD mais AMD n'en dit pas plus sur ce dont sont capables des unités d'exécutions. Dans un autre document, AMD parle cependant d'une largeur limitée à 128-bit pour son unité de calcul sur les flottants, un compromis adapté au marché visé selon le fabricant.

AMD a également fait progresser sa structure de caches. Le cache L1D est doublé et passe de 16 à 32 Ko. Le L1I redescend par contre à 64 Ko alors qu'il était monté à 96 Ko à partir de Piledriver, mais n'est plus partagé par 2 coeurs un sein d'un module. Le L2 est par contre réduit à 512 Ko par coeur alors que le L3 reste à 1 Mo par coeur, soit 8 Mo au total. Difficile de conclure à une nette évolution sur base de ces quelques informations simplifiées, mais AMD parle d'une bande passante par coeur qui pourrait aller jusqu'à être multipliée par 5.

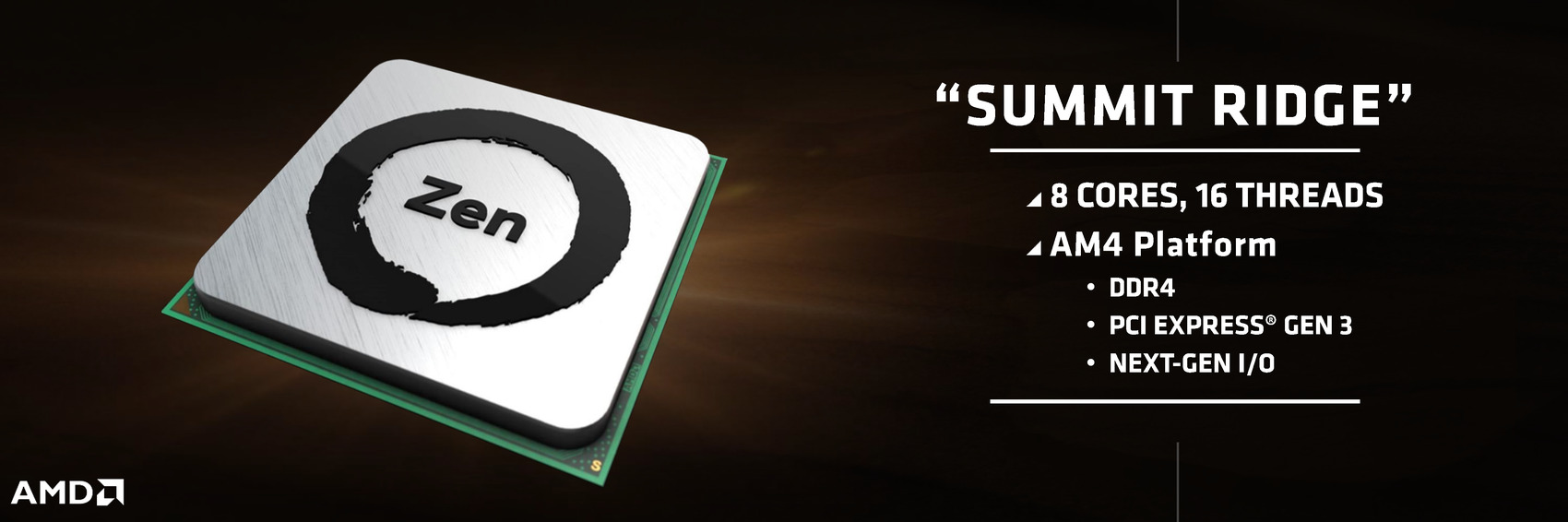

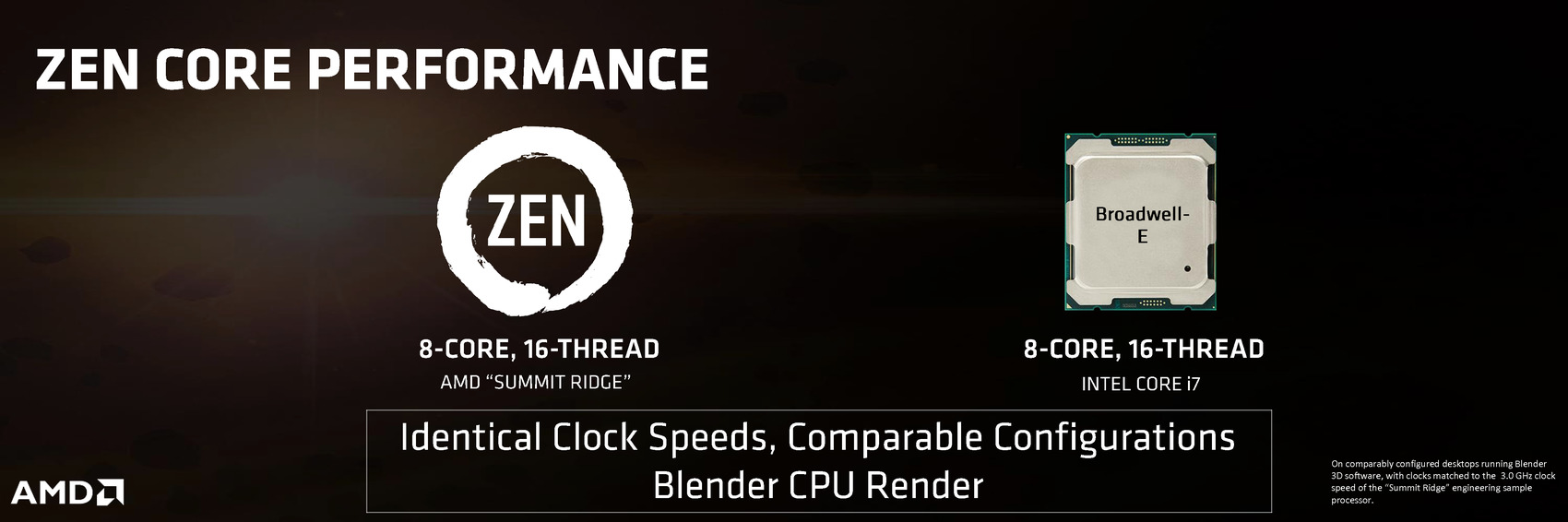

Pour aller plus loin que quelques slides, AMD a fait une première demonstration de performances en comparant un CPU Summit Ridge, Zen 8 coeurs / 16 threads, à un CPU Broadwell-E Core i7 6900K. Les 2 puces étaient cadencées à 3 GHz et équipées d'une mémoire similaire. Sous Blender, qui profite pleinement du multi-threading, Zen était légèrement devant tout en consommant un petit peu moins selon AMD.

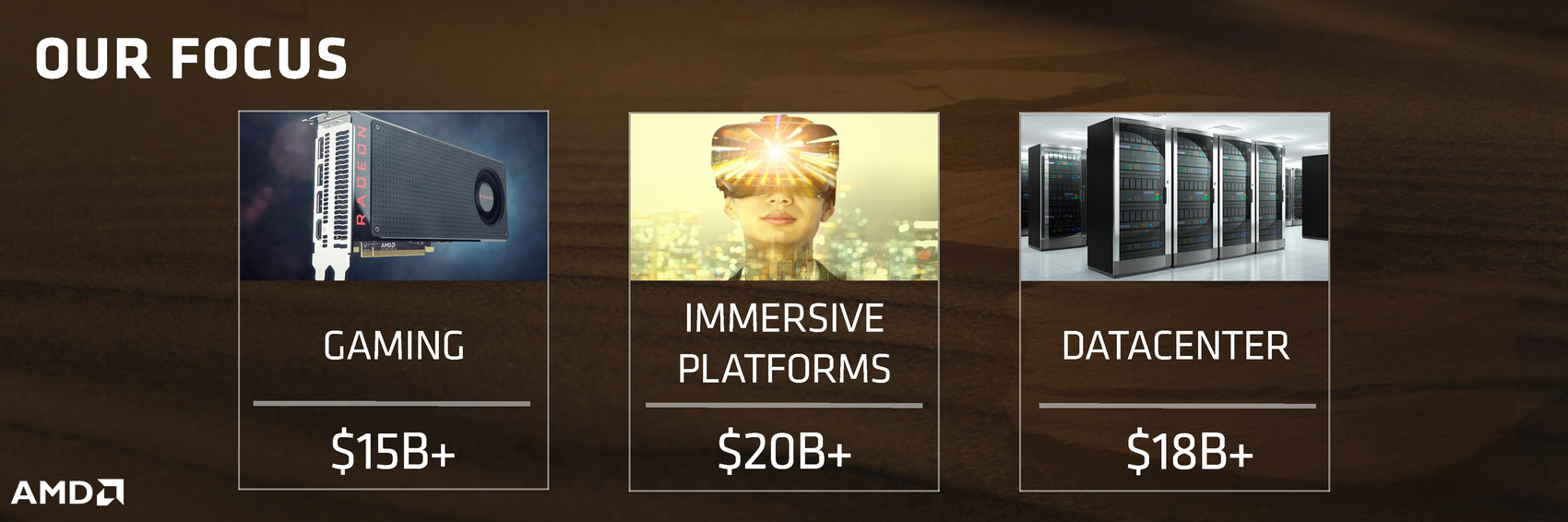

Une autre démonstration a été organisée sur une plateforme serveur 2P avec 2 CPU au nom de code Naples. Une manière pour AMD de confirmer officiellement la version 32 coeurs / 64 threads de Zen dont nous vous parlions il y a 6 mois. Ces CPU Naples sont prévus pour le second trimestre 2017. AMD précise en même temps avoir en quelque sorte mis de côté le développement de CPU ARM, estimant que ce marché n'a pas explosé comme prévu et que c'est du côté x86 qu'il y a le plus de potentiel.

Concernant la disponibilité des premiers CPU Zen, Summit Ridge, destinés à la plateforme AM4, AMD parle toujours du premier trimestre 2017 avec une possibilité de petits volumes fin 2016 si toutes les étoiles s'alignent. AMD ne communique rien en terme de fréquence ou encore de tarif, mais visiblement confiant dans ses prestations, AMD précise que Summit Ridge lui permettra de revenir à des niveaux de performances bien supérieurs à ce dont sont capables ses CPU actuels et donc de viser des segments tarifaires que la société a été forcée de déserter depuis de bien longues années. A noter qu'AMD indique, sans préciser de date, que l'architecture Zen sera ensuite suivie de Zen+ avec à la clef de nouvelles améliorations d'IPC.

Plus de détails devraient être communiqués la semaine prochaine à l'occasion du forum Hot Chips.

Vous pourrez retrouver la présentation complète ci-dessous :

Un souci d'USB 3.1 sur le chipset AM4 ?

La future plate-forme AMD AM4 devrait avoir la particularité d'accueillir des SoC, c'est-à-dire que les processeurs Summit Ridge (AMD FX "Zen") comme les Bristol Ridge (APU en AM4 basé sur Excavator) géreront, en sus du PCIe, directement le SATA et l'USB. Les ports gérés par le CPU seront toutefois limités en nombre (2 SATA 3.0 + 4 USB 3.0) et afin d'étendre les capacités un chipset, optionnel donc, est prévu : Promontory.

Le développement de cette puce a été sous-traité à ASMedia, une filiale d'ASUS spécialisé dans les contrôleurs additionnels. D'après DigiTimes , Promontory connaîtrait des soucis côté USB 3.1 selon la longueur des pistes, ce qui nécessiterait l'utilisation de puces supplémentaires voire d'un contrôleur USB 3.1 externe et augmenterait le coût des cartes mères de 2 à 5$.

AMD n'a pas commenté l'information alors que de son côté ASMedia a indiqué qu'il ne s'agissait que d'une rumeur et que ses produits avaient passés les certifications nécessaires. Il faudra probablement attendre la sortie des cartes mères pour dénouer tout ceci, mais dans tous les cas ce surcoût ne serait vraiment dommageable que sur les cartes mères les moins onéreuses.

Computex: Au Computex c'est Zen qui présente Zen

S'il y a bien un domaine dans lequel AMD est très attendu, c'est celui des CPU avec sa future architecture Zen. Le message d'AMD au Computex est que tout avance comme prévu.

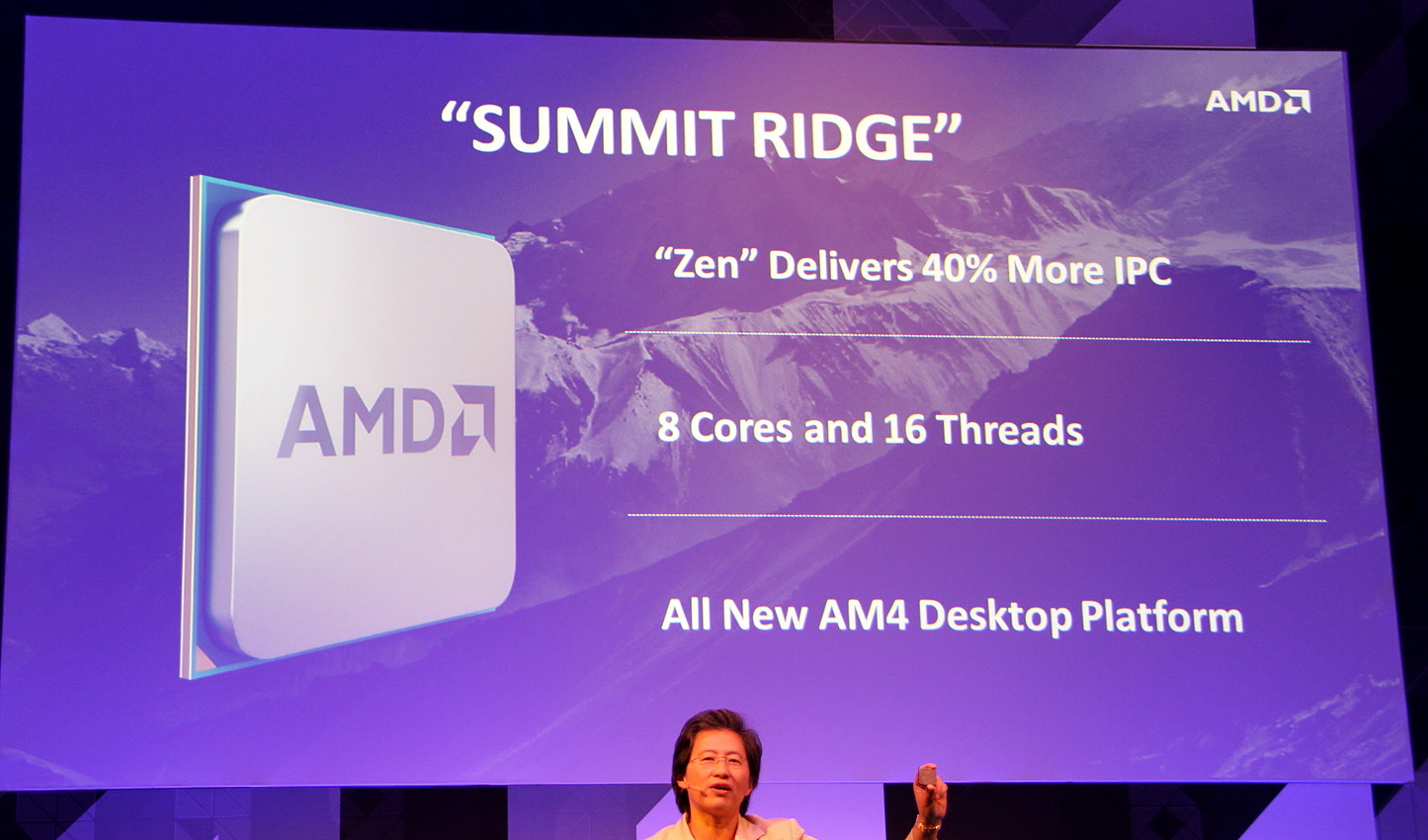

Lisa Su a tenu à dédier la dernière partie de sa présentation à Zen, nom de code de l'architecture qui pourrait redonner un coup de fouet aux CPU et APU de la société. La CEO d'AMD a tout d'abord tenu à réaffirmer que les objectifs n'avaient pas changé : proposer une alternative aux CPU hautes performances d'Intel. La première puce prévue sera, comme déjà annoncé précédemment, de type 8 coeurs / 16 threads et proposera un gain d'IPC de 40%. Si ce ne sera probablement pas suffisant pour reprendre la tête, cela devrait permettre de refermer le gouffre et de pouvoir proposer des CPU qui tiennent la route par rapport à la concurrence.

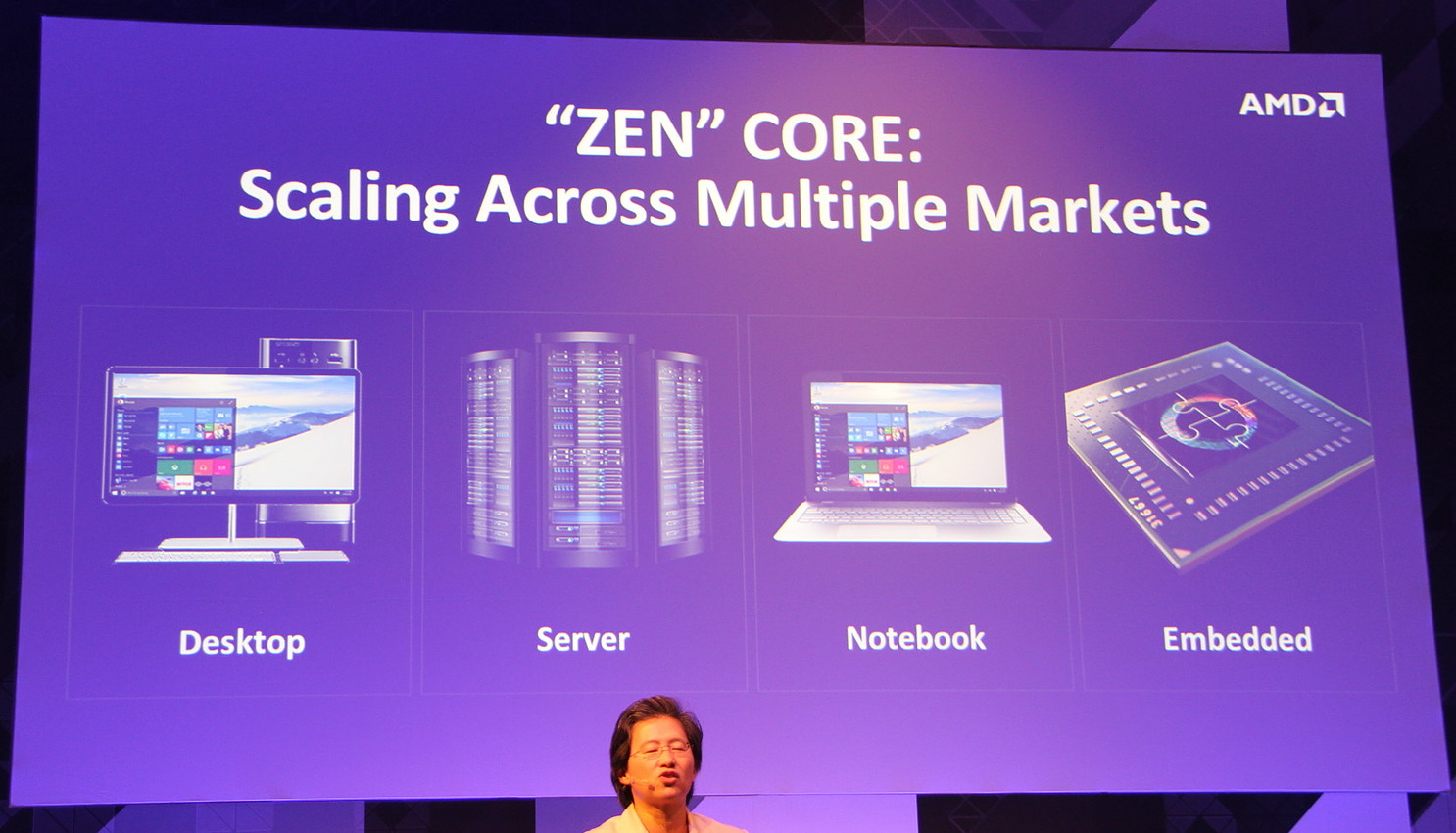

Lisa Su a ensuite confirmé que Zen serait d'abord proposé sur desktop, puis sur serveur, avant de débarquer dans les APU et d'être proposé dans l'embarqué. Reste que c'est surtout au niveau du timing qu'il peut y avoir des inquiétudes, mais à ce sujet Lisa Su se veut rassurante. Le tape-out de la première puce a été effectué en début d'année et Zen tourne dans les labos d'AMD, mais pas seulement.

Ce serait ainsi un système à base de Zen, une grosse tour rouge que nous n'avons pas pu approcher, qui aurait été exploité à Taipei pour monter, éditer et lire la vidéo d'introduction qui lui était dédiée. De quoi démontrer que les premiers prototypes sont fonctionnels, même si cela ne permet pas de savoir comment ils se comportent par rapport aux attentes.

Lisa Su a précisé que ses plus gros clients recevraient les premiers échantillons d'ici quelques semaines et que la montée en puissance de la production débuterait au 3ème trimestre, à priori à temps pour un lancement vers la fin de l'année.