Les contenus liés au tag IDF

Afficher sous forme de : Titre | FluxIDF: Haswell fonctionnel, en démo

Après Ivy Bridge, Mooly Eden a voulu rassurer par rapport à l'avancement de la mise au point de son successeur, Haswell. Nous avons ainsi pu en apercevoir un prototype sur son packaging, laissant entrevoir un die au format très allongé, d'une taille assez proche de celui d'Ivy Bridge.

Intel a insisté une fois de plus sur le fait qu'Haswell marquerait le point culminant de sa stratégie Ultrabook, grâce à un rendement énergétique très élevé, sans toutefois donner le moindre détail technique sur son architecture ni sur ses déclinaisons plus véloces.

Notez enfin que ce CPU prévu pour 2013 est déjà fonctionnel dans les labos du fondeur, desquels un exemplaire s'était échappé pour nous en apporter la preuve à l'IDF :

IDF: +20% de transistors, 16 EU pour Ivy Bridge

Lors de sa keynote, Mooly Eden, Vice-Président du PC Client Group, a dévoilé quelques petits détails supplémentaires sur Ivy Bridge. Il intègrera ainsi 1.4 milliards de transistors, soit 40% de plus que Sandy Bridge (995 millions) dont une bonne partie servira à mettre à jour le GPU intégré, qui représente la plus grosse évolution liée à cette architecture. Nous pouvons d'ailleurs nous demander si Intel ne va pas mettre à jour son GPU lors des "tick", avec le passage aux nouveaux procédés de fabrication, tout comme les cores CPU sont mis à jour lors des "tock".

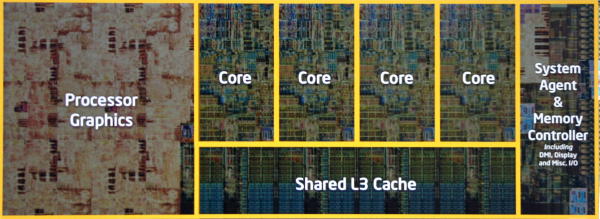

Le die d'Ivy Bridge est encore plus allongé que celui de Sandy Bridge, ce qui s'explique par l'intégration du contrôleur mémoire dans le bloc System Agent ainsi que par la surface plus importante occupée par le GPU. Alors qu'elle représente un peu moins de 20% de la surface totale dans Sandy Bridge, cette photo du die indique qu'il s'agira de plus de 30% pour Ivy Bridge.

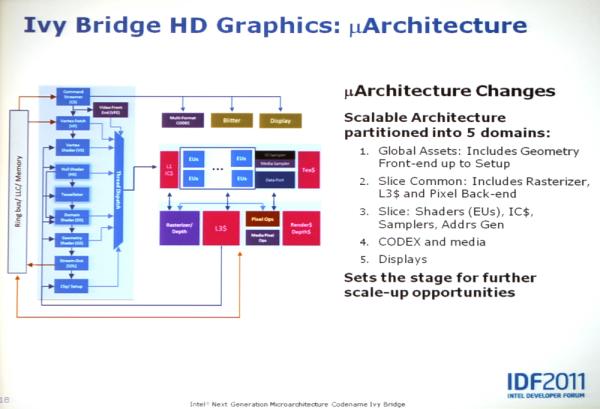

Comme nous l'expliquions précédemment, ce GPU va gagner en modularité et avec l'intégration des unités de texturing dans les blocs d'unités de calcul (EU) il sera également possible de faire varier leur nombre suivant les déclinaisons. Si Intel se refuse à rentrer dans plus de détails, les bruits de couloir font état de la présence de 16 EU dans Ivy Bridge, contre 12 dans Sandy Bridge. Par ailleurs, nous pouvons observer sur la partie GPU de la photo du die 4 blocs identiques d'une part et 2 autres identiques d'autre part. Il se pourrait donc qu'Ivy Bridge repose sur des blocs contenant 2x 4 EU ainsi que 4 unités de texturing. En plus des nombreuses optimisations (notamment le débit de FMA doublé par EU), Ivy Bridge disposerait ainsi de 33% d'EU de plus et du double d'unités de texturing, de quoi égaler Llano sur les performances graphiques.

Notez cependant que Mooly Eden a étrangement insisté sur le fait que la représentation du die sur cette photo n'est pas correcte. Pourtant elle correspond bien au die du wafer d'Ivy Bridge présenté il y a quelques mois, il ne s'agit donc pas d'un montage. Brouillage de piste ? Intel aurait-il changé ses plans et un die revu serait-il au programme, par exemple avec un GPU encore plus costaud pour affronter Trinity ?

Mise à jour du 16/09

Intel a précisé à Anandtech que la comparaison au niveau du nombre de transistors entre Ivy Bridge et Sandy Bridge n'était pas valide car les deux chiffres ont été obtenus à des étapes différentes du design. Pris à une étape plus avancée, lors de la création du layout, le nombre de transistors de Sandy Bridge passe de 995 millions à 1.16 milliards. Avec 1.4 milliards de transistors, Ivy Bridge repose donc sur 20% de transistors en plus et non 40%.

Reste à savoir pourquoi Intel a décidé de changer de méthode de comptage pour le nombre de transistors officiel et si l'impact entre ces différentes méthodes est similaire pour Ivy Bridge et Sandy Bridge.

IDF: Architecture Ivy Bridge, les détails

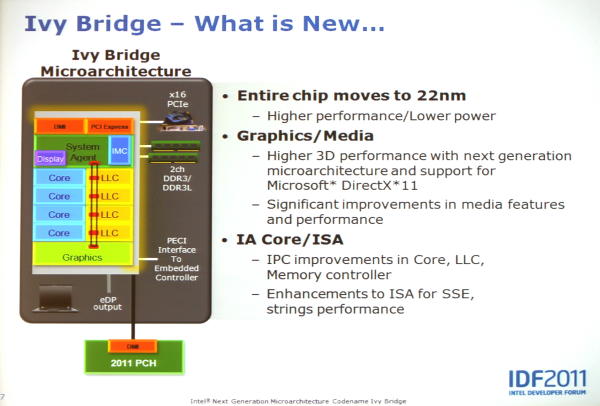

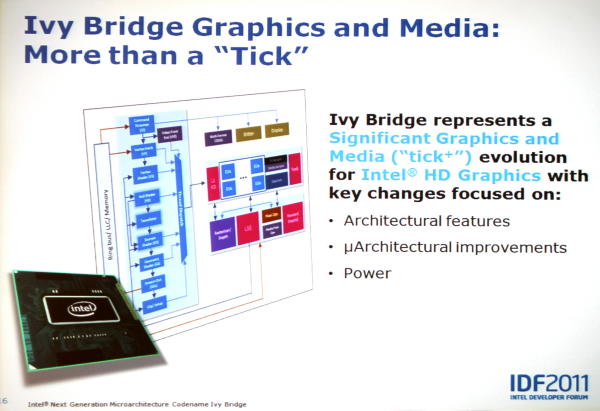

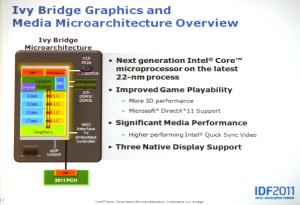

Comme chaque année, Intel profite de l'IDF pour dévoiler de nombreux détails sur l'architecture à venir, cette fois un refresh de l'architecture Sandy Bridge chargé d'introduire le procédé de fabrication trigate en 22 nanomètres : Ivy Bridge. Cette nouvelle architecture apportera globalement un meilleur rendement énergétique, ainsi qu'un core graphique significativement revu, en plus des traditionnelles nouvelles instructions.

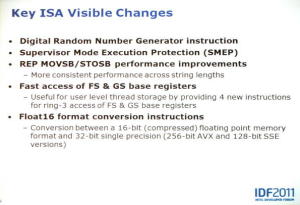

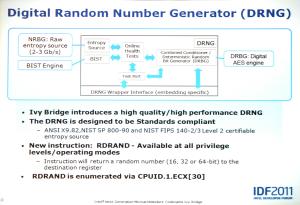

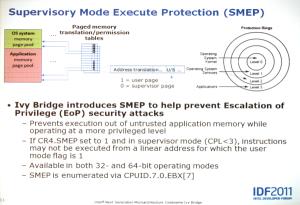

Plus spécifiquement, au niveau de l'ISA du CPU, Ivy Bridge apportera :

- - Un nouveau générateur de nombre aléatoire.

- Le SMEP (Supervisory Mode Execute Protection), pour éviter les attaques de type escalade de privilèges.

- Une amélioration des performances des instructions REP MOVSB et STOSB.

- Un accès rapide aux registres de base FS et GS.

- Des instructions de conversion du FP16 au FP32 et vice versa.

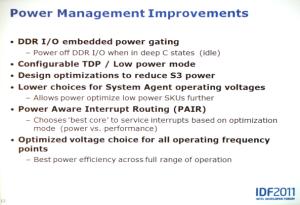

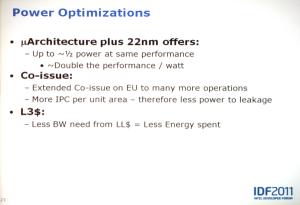

Pour réduire la consommation du CPU et de la plateforme dans son ensemble, Intel a mis en place un power gating autour des I/O DDR3, le support de la DDR3L (basse tension), un TDP configurable, des optimisations pour le mode S3, des tensions plus réduites disponibles pour le System Agent et des tensions mieux adaptées à chaque niveau de performances pour les cores.

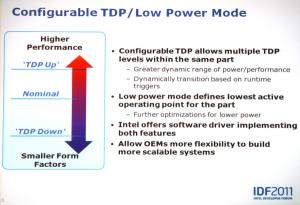

La plus grosse nouveauté proviendra probablement du TDP configurable qui consistera pour chaque modèle de CPU à donner 3 TDPs : un TDP de base, un TDP haut et un TDP bas. Suivant le type d'utilisation du PC, le système pourra décider du TDP à suivre. Par exemple, une fois connecté à une station d'accueil capable d'optimiser le refroidissement, un portable pourra passer au TDP supérieur. A l'inverse, un mode d'économie d'énergie avancée pourra forcer le portable dans le TDP inférieur.

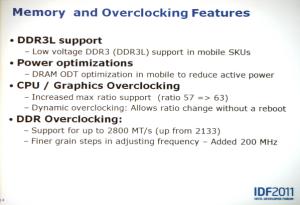

Enfin, quelques petites nouveautés au niveau de l'overclocking feront leur apparition telles qu'un multiplicateur maximum de 63 au lieu de 57, la possibilité d'en changer dynamiquement sans reboot et le support de la DDR3 jusqu'à une fréquence de 2800 MHz au lieu de 2133 MHz actuellement.

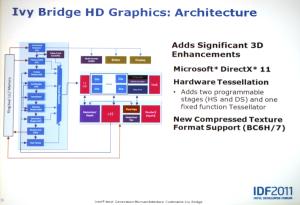

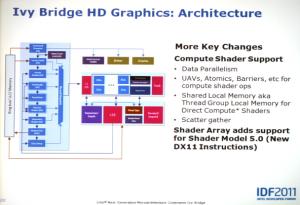

D'après Intel, c'est cependant du côté du GPU intégré que les nouveautés seront les plus importantes :

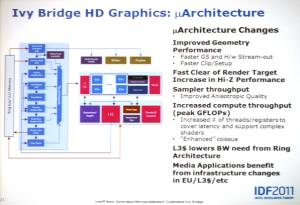

Le nouveau core graphique, qui a été revu pour pouvoir être décliné plus facilement dans des versions disposant de plus d'unités de calcul, serait ainsi nettement plus performant, en plus d'apporter le support complet de DirectX 11 et de DirectCompute. Intel précise cependant avoir privilégié l'augmentation du rendement des unités par rapport à l'augmentation de leur nombre, dans le but de maximiser l'efficacité énergétique. La co-issue a ainsi été améliorée de manière à pouvoir exécuter simultanément les instructions les plus courantes (FMA/MAD et dérivés), ce qui permet dans certains cas de doubler le débit du GPU.

D'autres petites améliorations sont elles aussi destinées à augmenter les performances :

- - Support plus performant des Geometry Shader et du Stream-Out.

- Setup plus évolué capable d'éjecter plus vite les triangles situés en dehors du champ de vision.

- Effacement rapide des render targets.

- HI-Z plus performant.

- Débit des unités de texturing en hausse sur certains formats et filtrage anisotrope de meilleure qualité.

- Support de plus de threads accompagné de plus de registres.

- Un cache L3 pour éviter de consommer trop de bande passante du ring bus ou du LLC.

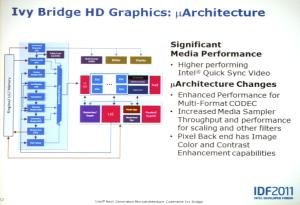

Le moteur vidéo QuickSync a bien entendu également été amélioré, notamment pour supporter l'encodage du MVC et des filtres plus complexes, alors que l'interface d'affichage sera capable de piloter jusqu'à 3 écrans indépendants.

Si Intel ne s'avance pas sur le niveau de performances graphiques d'Ivy Bridge, qui dépendra du nombre d'unités d'exécution, il précise cependant que les performances par watts vont doubler grâce à toutes ces optimisations. Suffisant pour s'opposer à la future APU Trinity d'AMD sur ce terrain ?

Enfin, vous noterez qu'Intel continue de trainer les pieds par rapport au support d'OpenCL sur le GPU intégré. S'il est possible qu'Ivy Bridge puisse le supporter sur la partie GPU en plus de la partie CPU, Intel préfère s'abstenir d'éclaircir ce point pour l'instant. Une position avant tout politique, le fondeur préférant mettre en avant d'autres solutions pour s'attaquer aux algorithmes massivement parallèles.

IDF: MAJ: Sandy Bridge-E, DX79SI, RTS2011LC

Alors qu'Intel semble plutôt discret sur la plateforme Sandy Bridge-E dont la sortie se rapproche, ce futur CPU haut de gamme est malgré tout en démonstration dans l'Extreme Zone de l'IDF, accompagné de la carte-mère de référence DX79SI ainsi que du système de refroidissement dédié au(x) modèle(s) Extreme Edition, le système de watercooling RTS2011LC.

La DX79SI est une carte-mère haut de gamme destinée à la plateforme socket 2011. Elle propose ainsi 3 ports PCI Express au format 16x (dont un câblé en 8x) et 2 slots mémoire par canal, soit 8 au total. Pour le reste sa connectique est par contre plutôt limitée, notamment au niveau des ports SATA (4 seulement), mais il est possible que cela change sur la version commerciale de la carte.

Les versions Extreme Edition du Sandy Bridge-E seront livrées avec un système de watercooling tout en un fabriqué par Asetek et dérivé du 570LC.

L'Extreme Tuning Utility sera mis à jour pour la sortie du Sandy Bridge-E, Intel en profitant pour faire la démonstration d'un overclocking à 4.72 GHz, certes loin du récent record d'AMD, mais obtenu avec le kit tel qu'il sera commercialisé et sur un système réellement utilisable.

Mise à jour :

Intel nous a précisé qu'en réalité aucun système de refroidissement ne sera livré avec aucun des Sandy Bridge-E, le fabricant estimant que dans tous les cas les utilisateurs préféreraient se tourner vers un modèle différent de celui de référence.

Le kit de watercooling tout en un RTS2011LC sera cependant commercialisé à part par Intel.

IDF: La grand-messe Intel ouvre ses portes

Comme chaque année, le mois de septembre est l'occasion de se rendre à l'Intel Developer Forum de San Francisco, évènement au cours duquel Intel fait le point sur ses plans autant à court terme qu'à long terme. De quoi en apprendre en peu plus, tout du moins nous l'espérons, sur les Sandy Bridge E et leur plateforme, sur Ivy Bridge et le 22 nanomètre, sur Cedar Trail et les tablettes ou encore sur l'architecture MIC et les successeurs de Larrabee.

La keynote d'ouverture de Paul Otellini, le CEO et Président d'Intel, est cependant restée inhabituellement sobre et vague en annonces, évitant notamment toute référence aux Sandy Bridge E dont la finalisation de la plateforme semblerait poser quelques problèmes de dernière minute.

Paul Otellini a principalement rappelé l'importance de proposer aux utilisateurs un environnement consistant dans lequel pourront circuler de manière transparente les informations entre les différents périphériques connectés qui sont en train de se multiplier à vive allure, ce qui inclut bien entendu la garantie d'une sécurisation suffisante. Le rachat de McAfee commencera d'ailleurs très bientôt à porter ses fruits à ce niveau avec l'arrivée de DeepSAFE tout d'abord réservée au monde professionnel et qui proposera, en combinaison avec les CPU de la marque, une sécurité renforcée contre les rootkits. Une première étape avant la généralisation de l'intégration plus poussée entre le CPU et le logiciel pour renforcer la sécurité sur toutes les plateformes proposées par le fondeur.

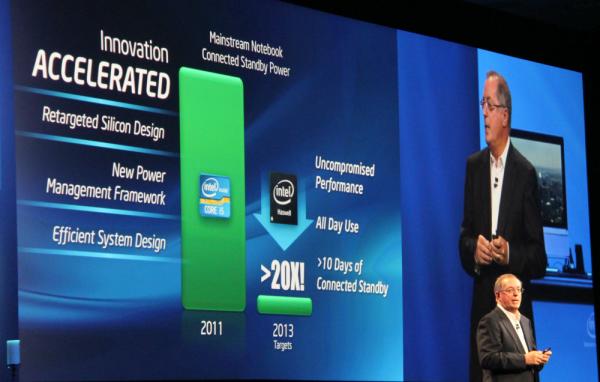

Pour faciliter une connectivité permanente, Paul Otellini indique se reposer sur le travail acharné entrepris par Intel depuis plusieurs années autour de la réduction de la consommation de la plateforme. En plus de faire baisser l'enveloppe thermique en charge de 50%, la plateforme Ultrabook de 2013, bâtie autour du CPU Haswell fabriqué en 22nm, devrait ainsi permettre une réduction de plus de 20X de la consommation en mode veille connectée, de quoi porter l'autonomie dans ce mode à plus de 10 jours ! Pour rappel, ce mode veille connectée permet par exemple d'avoir un accès instantané à ses emails lors du réveil du PC ainsi qu'à toutes autres données qui émergeront des nouveaux modèles d'utilisation ainsi rendus possibles (météo, news, état de remplissage du frigo ).

Paul Otellini et Andy Rubin, Senior Vice President of Mobile, Google.

Enfin, pour conclure ce premier keynote, Paul Otellini a annoncé un partenariat important, attendu depuis longtemps : la coopération renforcée avec Google afin d'optimiser la plateforme Android pour la famille Atom. Intel s'assure ainsi l'accès à un écosystème en pleine explosion et Google à une plateforme x86 qui est loin d'avoir dit ses derniers mots. Pour renforcer l'aspect concret de cette annonce, Paul Otellini a également brièvement montré un smartphone basé sur le SoC Atom Medfield et qui fera office de plateforme de développement pour Android 2.3.