Les derniers contenus liés aux tags Ivy Bridge et IDF

Les 2 contenus de cette page

IDF: +20% de transistors, 16 EU pour Ivy Bridge

IDF: Architecture Ivy Bridge, les détails

IDF: +20% de transistors, 16 EU pour Ivy Bridge

Publié le 15/09/2011 à 08:00 par Damien Triolet

Lors de sa keynote, Mooly Eden, Vice-Président du PC Client Group, a dévoilé quelques petits détails supplémentaires sur Ivy Bridge. Il intègrera ainsi 1.4 milliards de transistors, soit 40% de plus que Sandy Bridge (995 millions) dont une bonne partie servira à mettre à jour le GPU intégré, qui représente la plus grosse évolution liée à cette architecture. Nous pouvons d'ailleurs nous demander si Intel ne va pas mettre à jour son GPU lors des "tick", avec le passage aux nouveaux procédés de fabrication, tout comme les cores CPU sont mis à jour lors des "tock".

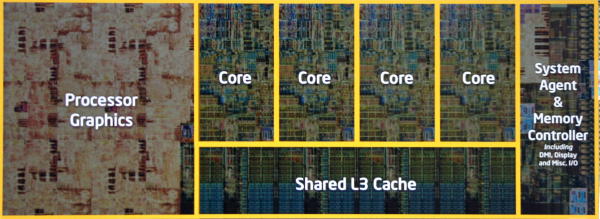

Le die d'Ivy Bridge est encore plus allongé que celui de Sandy Bridge, ce qui s'explique par l'intégration du contrôleur mémoire dans le bloc System Agent ainsi que par la surface plus importante occupée par le GPU. Alors qu'elle représente un peu moins de 20% de la surface totale dans Sandy Bridge, cette photo du die indique qu'il s'agira de plus de 30% pour Ivy Bridge.

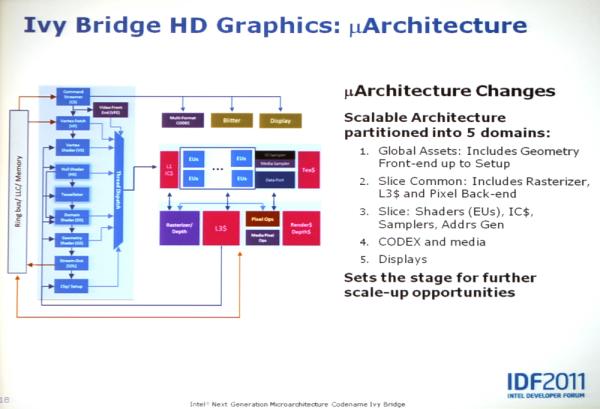

Comme nous l'expliquions précédemment, ce GPU va gagner en modularité et avec l'intégration des unités de texturing dans les blocs d'unités de calcul (EU) il sera également possible de faire varier leur nombre suivant les déclinaisons. Si Intel se refuse à rentrer dans plus de détails, les bruits de couloir font état de la présence de 16 EU dans Ivy Bridge, contre 12 dans Sandy Bridge. Par ailleurs, nous pouvons observer sur la partie GPU de la photo du die 4 blocs identiques d'une part et 2 autres identiques d'autre part. Il se pourrait donc qu'Ivy Bridge repose sur des blocs contenant 2x 4 EU ainsi que 4 unités de texturing. En plus des nombreuses optimisations (notamment le débit de FMA doublé par EU), Ivy Bridge disposerait ainsi de 33% d'EU de plus et du double d'unités de texturing, de quoi égaler Llano sur les performances graphiques.

Notez cependant que Mooly Eden a étrangement insisté sur le fait que la représentation du die sur cette photo n'est pas correcte. Pourtant elle correspond bien au die du wafer d'Ivy Bridge présenté il y a quelques mois, il ne s'agit donc pas d'un montage. Brouillage de piste ? Intel aurait-il changé ses plans et un die revu serait-il au programme, par exemple avec un GPU encore plus costaud pour affronter Trinity ?

Mise à jour du 16/09

Intel a précisé à Anandtech que la comparaison au niveau du nombre de transistors entre Ivy Bridge et Sandy Bridge n'était pas valide car les deux chiffres ont été obtenus à des étapes différentes du design. Pris à une étape plus avancée, lors de la création du layout, le nombre de transistors de Sandy Bridge passe de 995 millions à 1.16 milliards. Avec 1.4 milliards de transistors, Ivy Bridge repose donc sur 20% de transistors en plus et non 40%.

Reste à savoir pourquoi Intel a décidé de changer de méthode de comptage pour le nombre de transistors officiel et si l'impact entre ces différentes méthodes est similaire pour Ivy Bridge et Sandy Bridge.

IDF: Architecture Ivy Bridge, les détails

Publié le 14/09/2011 à 09:38 par Damien Triolet

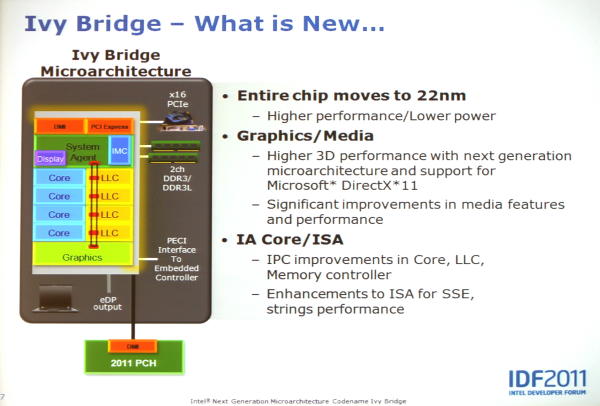

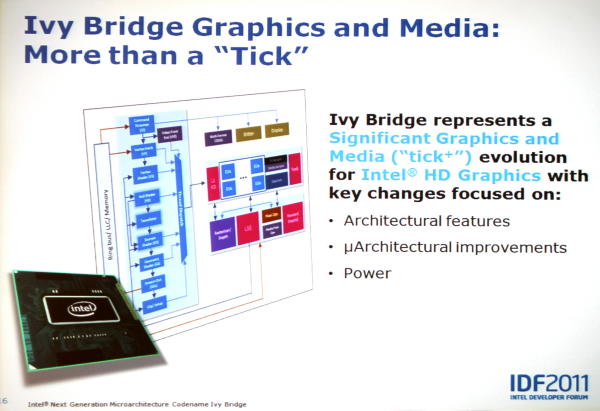

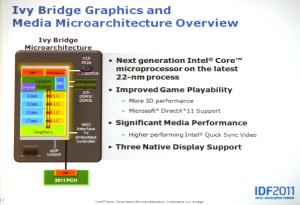

Comme chaque année, Intel profite de l'IDF pour dévoiler de nombreux détails sur l'architecture à venir, cette fois un refresh de l'architecture Sandy Bridge chargé d'introduire le procédé de fabrication trigate en 22 nanomètres : Ivy Bridge. Cette nouvelle architecture apportera globalement un meilleur rendement énergétique, ainsi qu'un core graphique significativement revu, en plus des traditionnelles nouvelles instructions.

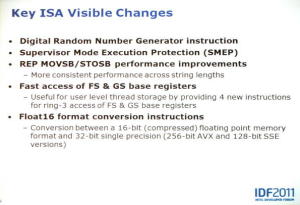

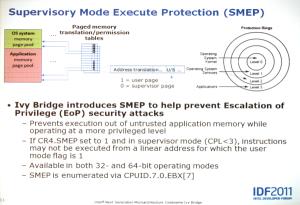

Plus spécifiquement, au niveau de l'ISA du CPU, Ivy Bridge apportera :

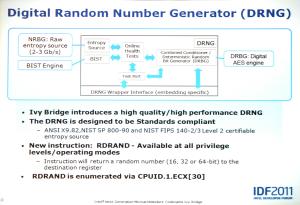

- - Un nouveau générateur de nombre aléatoire.

- Le SMEP (Supervisory Mode Execute Protection), pour éviter les attaques de type escalade de privilèges.

- Une amélioration des performances des instructions REP MOVSB et STOSB.

- Un accès rapide aux registres de base FS et GS.

- Des instructions de conversion du FP16 au FP32 et vice versa.

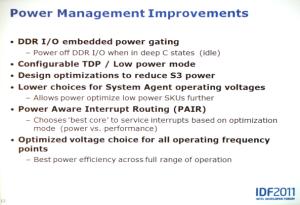

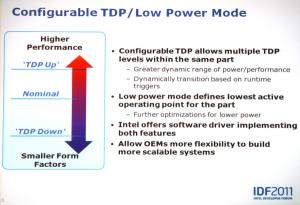

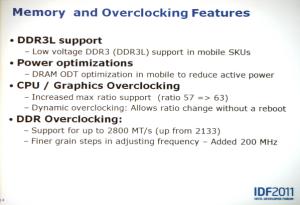

Pour réduire la consommation du CPU et de la plateforme dans son ensemble, Intel a mis en place un power gating autour des I/O DDR3, le support de la DDR3L (basse tension), un TDP configurable, des optimisations pour le mode S3, des tensions plus réduites disponibles pour le System Agent et des tensions mieux adaptées à chaque niveau de performances pour les cores.

La plus grosse nouveauté proviendra probablement du TDP configurable qui consistera pour chaque modèle de CPU à donner 3 TDPs : un TDP de base, un TDP haut et un TDP bas. Suivant le type d'utilisation du PC, le système pourra décider du TDP à suivre. Par exemple, une fois connecté à une station d'accueil capable d'optimiser le refroidissement, un portable pourra passer au TDP supérieur. A l'inverse, un mode d'économie d'énergie avancée pourra forcer le portable dans le TDP inférieur.

Enfin, quelques petites nouveautés au niveau de l'overclocking feront leur apparition telles qu'un multiplicateur maximum de 63 au lieu de 57, la possibilité d'en changer dynamiquement sans reboot et le support de la DDR3 jusqu'à une fréquence de 2800 MHz au lieu de 2133 MHz actuellement.

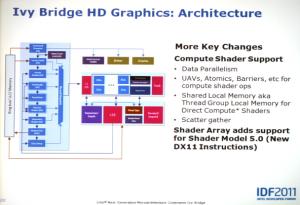

D'après Intel, c'est cependant du côté du GPU intégré que les nouveautés seront les plus importantes :

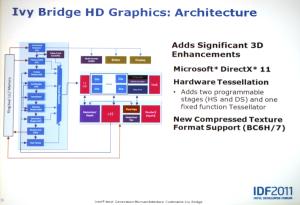

Le nouveau core graphique, qui a été revu pour pouvoir être décliné plus facilement dans des versions disposant de plus d'unités de calcul, serait ainsi nettement plus performant, en plus d'apporter le support complet de DirectX 11 et de DirectCompute. Intel précise cependant avoir privilégié l'augmentation du rendement des unités par rapport à l'augmentation de leur nombre, dans le but de maximiser l'efficacité énergétique. La co-issue a ainsi été améliorée de manière à pouvoir exécuter simultanément les instructions les plus courantes (FMA/MAD et dérivés), ce qui permet dans certains cas de doubler le débit du GPU.

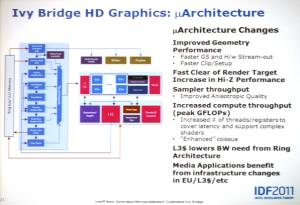

D'autres petites améliorations sont elles aussi destinées à augmenter les performances :

- - Support plus performant des Geometry Shader et du Stream-Out.

- Setup plus évolué capable d'éjecter plus vite les triangles situés en dehors du champ de vision.

- Effacement rapide des render targets.

- HI-Z plus performant.

- Débit des unités de texturing en hausse sur certains formats et filtrage anisotrope de meilleure qualité.

- Support de plus de threads accompagné de plus de registres.

- Un cache L3 pour éviter de consommer trop de bande passante du ring bus ou du LLC.

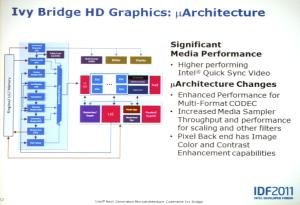

Le moteur vidéo QuickSync a bien entendu également été amélioré, notamment pour supporter l'encodage du MVC et des filtres plus complexes, alors que l'interface d'affichage sera capable de piloter jusqu'à 3 écrans indépendants.

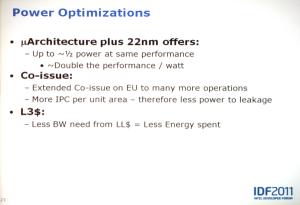

Si Intel ne s'avance pas sur le niveau de performances graphiques d'Ivy Bridge, qui dépendra du nombre d'unités d'exécution, il précise cependant que les performances par watts vont doubler grâce à toutes ces optimisations. Suffisant pour s'opposer à la future APU Trinity d'AMD sur ce terrain ?

Enfin, vous noterez qu'Intel continue de trainer les pieds par rapport au support d'OpenCL sur le GPU intégré. S'il est possible qu'Ivy Bridge puisse le supporter sur la partie GPU en plus de la partie CPU, Intel préfère s'abstenir d'éclaircir ce point pour l'instant. Une position avant tout politique, le fondeur préférant mettre en avant d'autres solutions pour s'attaquer aux algorithmes massivement parallèles.

Les 2 contenus de cette page