Les contenus liés au tag Process

Afficher sous forme de : Titre | Flux12nm FD-SOI pour GlobalFoundries

Nouvel accord WSA entre AMD/GlobalFoundries

Intel Custom Foundry prend une licence ARM !

L'ITRS prépare l'après loi de Moore

16 Go en TLC 20nm chez Micron : 146mm²

10/7nm en avance pour TSMC, EUV pour le 5nm

TSMC vient de publier ses résultats financiers pour le troisième trimestre. Le fondeur taiwannais enregistre une hausse séquentielle de 17% (+22% par rapport à la même période sur 2015), au dessus de ses prévisions. Des bons chiffres qui s'expliquent selon TSMC par une forte demande sur le marché des smartphones.

Ramenés par process, le 16/20nm représente 31% des revenus de la société (contre 23% le trimestre précédent). Le 28nm voit sa part baisser à 24% des revenus, mais TSMC confirme que ses usines restent "pleinement utilisées".

En ce qui concerne les prochains nodes, TSMC a confirmé les informations publiées un peu plus tôt, à savoir l'avance prise par les process 10 et 7nm.

Le 10nm entre en production ce trimestre et les premiers produits finaux seront livrés au premier trimestre 2017. Ce node ne sera pour rappel utilisé que par les très gros clients de TSMC, à savoir Apple et possiblement Qualcomm. Les autres clients attendront le 7nm. La montée des yields est décrite comme "similaire" à celle du 16nm même si "techniquement plus difficile".

Le 7nm entrera en production "risque" au premier trimestre 2017 et TSMC s'empresse d'indiquer qu'il sera utilisé non seulement pour les smartphones, mais aussi pour des GPU, des puces serveurs, et des "PC et tablettes". TSMC décrit des tapeout aggressifs qui commenceront au début du second trimestre. 15 produits devraient être qualifiés en 2017.

La fondeur a également évoqué le 5nm, qui a quitté le stade de la recherche pure pour entrer dans une phase de développement. Et TSMC confirme qu'ils utiliseront de manière "extensive" la lithographie EUV. Cette dernière aurait fait des progrès sur tous les plans, que ce soit en fiabilité, ou sur les problèmes techniques complexes (masques, photo resist, etc). La production "risque" reste prévue pour la première moitié de 2019 (la production volume suit en général de 3 à 4 trimestres).

Lors de la présentation des résultats aux analystes financiers, le CEO de TSMC, Mark Liu, a réitéré une fois de plus voir "l'informatique haute performance" comme un marché sur lequel TSMC espère voir une progression de ses ventes. Les serveurs et les PC clients sont mis en avant, et on a du mal a ne pas y voir un lien avec les annonces d'AMD sur sa renégociation du contrat WSA qui les lie à GlobalFoundries.

Dans la séance de questions/réponses posées, on notera qu'a la question de savoir si la prise de licence ARM par Intel est un risque, Mark Liu estime surtout que cela renforce le rôle d'ARM, tout en ne négligeant pas le rôle qu'Intel pourrait jouer. Reste que sur ce trimestre, la part de marché de TSMC chez les fondeurs (hors activité propre comme Intel pour ses propres puces donc) était de 55%.

Un transistor 1nm fonctionnel

La revue scientifique Science a publié la semaine dernière un papier de l'université de Berkeley évoquant leur recherche sur de nouveaux types de transistors.

Réalisé par un laboratoire de l'université de Berkeley (en partenariat avec le département américain de l'énergie), le papier évoque un transistor utilisant de nouveaux matériaux pour remplacer le silicium.

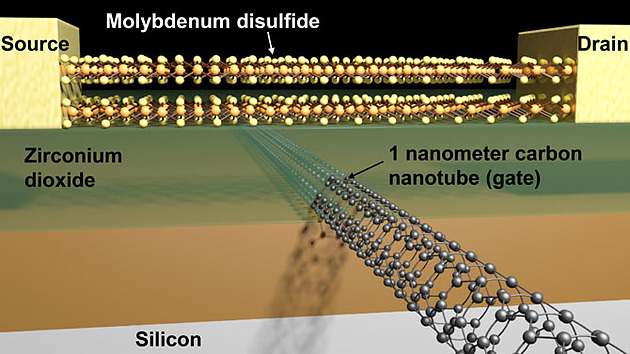

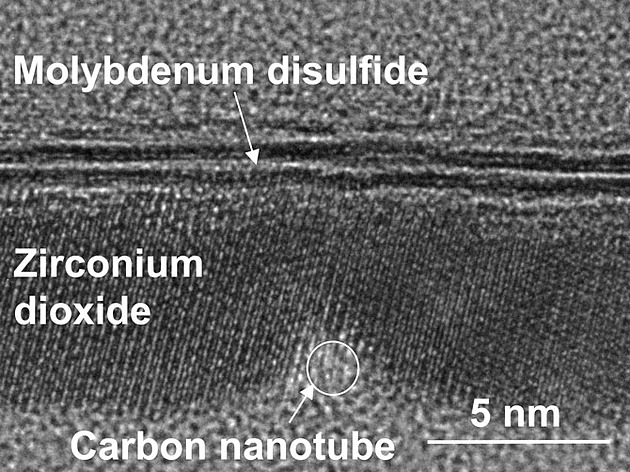

Le laboratoire utilise du disulfure de molybdène (MoS2) pour remplacer le silicium pour la construction principale du transistor. La partie diélectrique de la grille est en dioxyde de zirconium (ZrO2) et la grille en elle même ("l'interrupteur" du transistor) est remplacée par un nanotube de carbone. En pratique la largeur de la grille est d'environ 1 nm.

Théoriquement le MoS2 apporte plusieurs avantages par rapport au silicium, avec une réduction de deux ordres de grandeur des courants de fuites sous les 5nm (on considère en général que 5nm est la limite à partir de laquelle il sera indispensable de changer de matériaux pour les semi conducteurs).

Pour ce prototype, un long nanotube de carbone a été placé par dépôt chimique en phase vapeur. Le procédé de fabrication reste excessivement complexe (en mettant de côté la fabrication également complexe des nanotubes de carbone), et les auteurs de la recherche admettent que la quantité de barrières techniques à surmonter pour imaginer une fabrication en volume est très élevée. Malgré tout, le transistor fabriqué était fonctionnel.

Si la prouesse doit être saluée, on doit noter que le MoS2 n'est pas forcément le matériau idéal pour remplacer le silicium. Si les courants de fuite sont fortement en baisse, c'est aussi parce que les électrons y ont une masse effective largement plus élevée. En pratique, la mobilité des électrons dans le MoS2 est généralement considérée comme très mauvaise ce qui se traduit par une vitesse des transistors réduite. Un point qui n'est pas nouveau mais qui est mis de côté par les auteurs du papier.

D'autres matériaux plus prometteurs sont considérés par les acteurs du marché, on sait par exemple qu'Intel a effectué beaucoup de recherche sur l'Arséniure de Gallium-Indium (InGaAs) ou le Phosphore d'Indium (InP) qui pourraient apparaître dans l'un des prochains process du constructeur. TSMC et Samsung s'intéressent également de près à ces nouveaux matériaux que l'on attend probablement autour de 5nm.

10 et 7nm en avance chez TSMC ?

Un des auteurs du blog SemiWiki a assisté à l'OIP Ecosystem Forum de TSMC et rapporte plusieurs informations intéressantes ayant été données par le fondeur taiwannais concernant ses process à venir.

Pour ce qui est du 10nm, TSMC serait en avance avec une production en volume (HVM) avancée d'un trimestre : au lieu de démarrer en Q1 2017, elle démarrera au dernier trimestre de cette année.

Le développement du 7nm, lié à celui du 10nm (voir notre article précédent) serait lui aussi en avance d'un trimestre. La production "risque" démarrera au premier trimestre 2017, et la production en volume au quatrième trimestre 2017.

La roadmap 10/7nm de TSMC, déjà excessivement agressive par rapport à la concurrence, le devient encore plus. TSMC utilisera pour rappel le même matériel pour la fabrication des deux nodes (avec une densité qui augmente largement, 1.63x annoncé entre 10 et 7nm) ce qui explique la manière dont les deux nodes avancent en simultanée.

On rappellera toutefois que si le 10nm sera disponible rapidement en volume, il ne devrait être utilisé que par les gros clients "mobiles" de TSMC (Apple et possiblement Qualcomm). La majorité des clients de TSMC (fabricants de GPU inclus) devrait passer directement au 7nm qui sera le vrai node "pour tous" (à l'image de ce que l'on a pu voir avec le 20nm et le 16nm).

TSMC et InFo PoP pour l'A10 de l'iPhone 7

Ce week end, la société Chipworks a procédé à son traditionnel "teardown" des puces incluses dans l'iPhone 7 , en se concentrant particulièrement sur le SoC A10 d'Apple.

Rappel sur l'A9

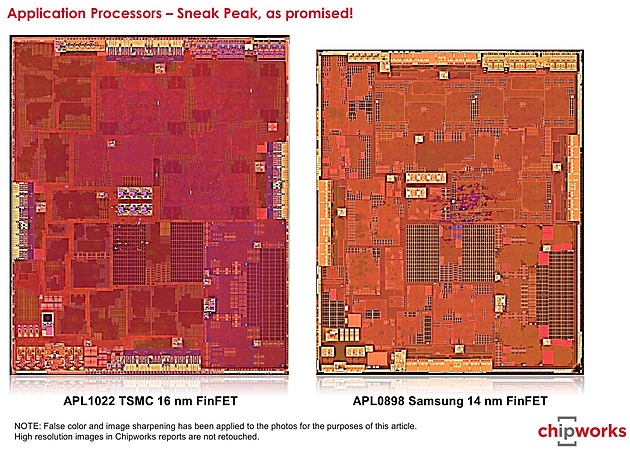

Avant de regarder l'A10, revenons un instant sur l'A9 inclus l'année dernière dans l'iPhone 6S. Il avait la particularité d'être sourcé en parallèle chez Samsung et TSMC, quelque chose de quasi unique pour des puces haut de gamme sur des process de dernière génération, ce qui nous avait permis d'effectuer quelques comparaisons.

Les deux A9 de l'iPhone 6S (2015)

La différence la plus visible était la densité des deux process : l'A9 "Samsung" mesurant 96mm2, contre 104.5mm2 pour la version TSMC. A l'époque nous n'avions pas de certitudes sur les variantes exactes des process utilisées. Depuis, Chipworks a confirmé qu'il s'agissait bien du 14LPE chez Samsung. Le cas de TSMC est plus compliqué, Chipworks ne répondant pas (gratuitement) à la question. Les rumeurs laissent penser qu'il ne s'agissait pas d'un simple 16FF, mais d'une version "custom" empruntant en partie au process 16FF+.

Outre la densité, les tests pratiques avaient suggéré une différence de consommation à pleine charge avec un avantage pour la puce de TSMC. De quoi laisser penser que son process avait besoin de tensions inférieures à celui de Samsung pour obtenir les mêmes performances.

Depuis, Chipworks a la aussi répondu partiellement à la question suggérant que le problème se situerait pour le process de Samsung sur le rapport puissance/performances de ses NMOS . On ne sait pas si le problème persiste sur la version 14LPP qui a remplacé le 14LPE.

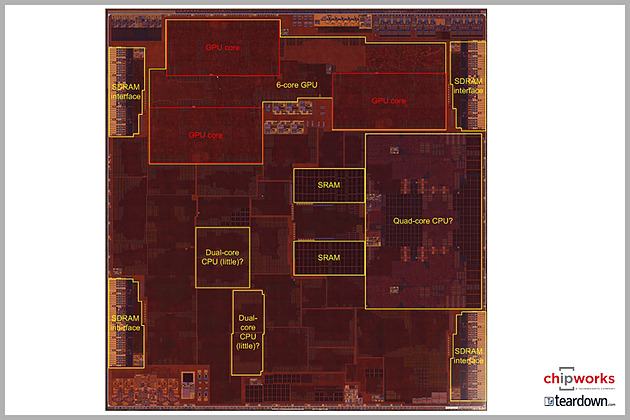

L'A10 : 16FFC TSMC

Première différence par rapport à l'année dernière, l'A10 semble produit cette année exclusivement par TSMC. Il est plus large que l'A9, mesurant 125mm2 pour 3.3 milliards de transistors annoncés. Côté process il s'agit du 16FFC (ou d'une variante) de TSMC, la troisième version "optimisée" du 16nm de TSMC. Annoncée en janvier dernier, le C signifie "Compact" et ce process vise avant tout les usages basses consommation tout en réduisant de manière significative les coûts de fabrication.

D'après Chipworks, l'utilisation des bibliothèques optimisées permet une bien meilleure utilisation du die, avec une compacité équivalente à celle des process TSMC précédents. Chipworks estime que la même puce aurait demandé 150mm2 en 16FF. Etant donné que 70 tapeouts de clients de TSMC sont attendus sur ce process cette année, les progrès de densité du 16FFC devraient profiter assez largement, on attendra de voir les constructeurs qui annonceront des puces l'utilisant.

Chipworks note également que l'A10 est beaucoup moins haut que les générations précédentes. Comme beaucoup de SoC, il est de type PoP et embarque la mémoire au dessus du die logique. Cependant plutôt que d'empiler les quatre dies de mémoire (2 Go de LPDDR4 Samsung sur l'A10 de l'iPhone 7), ils sont placés côte à côte.

Qui plus est, comme nous le supposions la puce utilise le nouveau packaging InFo de TSMC (dans sa version InFo-PoP) pour relier les dies entre eux.

big.LITTLE et performances

Côté performances les premiers benchmarks synthétiques évoquent 40% de gains pour le CPU ARM par rapport à l'année dernière, tout en restant en 16nm.

Pour arriver à ce gain, Apple augmente d'abord significativement la fréquence, passant de 1.85 GHz sur l'A9 à 2.35 GHz sur l'A10. Sur ce point, la marque exploite à la fois la marge notée de son process l'année dernière (on peut supposer facilement que l'A9 aurait eu une fréquence plus élevée s'il avait été sourcé uniquement chez TSMC) et les gains apportés par le 16FFC.

Ce gain de 27% de fréquence est accompagné de changements au niveau de l'architecture. Ceux ci ne sont pas encore connus, au delà du nom Hurricane, mais Chipworks note que le cluster CPU prend une place plus importante sur le die, 16mm2 face à 13mm2 sur l'A9, malgré l'utilisation d'un process plus compact.

Il est cependant difficile de se baser sur cette différence de taille étant donné que l'A10 est en réalité un quad core big.LITTLE dans la nomenclature ARM. En plus des deux coeurs hautes performances à 2.35 GHz (big), deux coeurs basse consommation à 1.05 GHz (LITTLE) sont également présents sur le die (leur emplacement exact est pour l'instant inconnu, ce qui vaut les points d'interrogation sur le diagramme au dessus).

Contrairement à d'autres implémentations dans l'écosystème ARM, les applications ne peuvent pas utiliser en simultanée les deux blocs de coeurs, le passage de l'un à l'autre étant transparent pour elles (géré par la puce et l'OS). L'intérêt de cet arrangement est bien entendu d'augmenter l'autonomie en ne sollicitant les coeurs haute performances que lorsque nécessaire.

Déjà largement en avance côté performances sur le reste de l'écosystème ARM, l'A10 commence à devenir embarrassant même pour Intel, dépassant un Core M Skylake en monothread sous Geekbench 4 (voir ici et là ), avec un "TDP" au moins deux fois inférieur (et sans mécanisme Turbo).

Intel se consolera tout de même de sa présence dans une partie des iPhone 7 car c'est l'autre information de Chipworks, la société confirme qu'une partie des modèles utilise un modem Intel XMM 7360 (certains modèles intègrent un modem Qualcomm X12). Très en retard, le XMM 7360 est un modem LTE 450 Mb/s Cat 10 certes dessiné par Intel, mais fabriqué selon toutes vraisemblances comme ses prédécesseurs... par TSMC.

7nm fin 2018 pour GlobalFoundries ?

GlobalFoundries a publié un communiqué de presse annonçant officiellement son prochain process FinFet, qui sera en 7nm. On rapellera que le process 14 FinFET actuel de GlobalFoundries, le 14LPP, a été développé par Samsung suite aux problèmes de développement du 14XM (la version interne du 14nm de GlobalFoundries, abandonnée).

Comme nous vous l'avions indiqué, GlobalFoundries ne proposera pas de 10nm, son prochain process sera donc un 7nm, baptisé tout simplement 7nm FinFET. Comme souvent, le communiqué du fondeur est particulièrement flou, indiquant à la fois que ce 7nm FinFET profitera des "années d'expérience d'IBM", tout en se "construisant sur le succès du 14LPP".

Le fondeur donne deux chiffres, tout d'abord une densité double par rapport "aux process 16/14", et un gain de performances de 30%. On notera avec circonspection que chez TSMC par exemple, le 10nm est annoncé comme 2.1x plus dense que son 16nm, et que son 7nm sera 1.63x plus dense que son 10nm. Autant dire que le 2x annoncé par GlobalFoundries ne semble pas vraiment au niveau d'un "7nm".

Techniquement le fondeur confirme qu'il s'agira d'un process FinFET optique, avec éventuellement la possibilité d'utiliser de l'EUV si disponible sur quelques couches.

Côté délais, GlobalFoundries annonce une production "risque" début 2018. A titre de comparaison, le 7nm de TSMC est annoncé en production risque début 2017, avec une production volume démarrant en Q1 2018.

Sur le papier donc, ce communiqué de presse de GlobalFoundries est tout simplement inquiétant, dévoilant un 7nm dont les caractéristiques techniques semblent assez lointaines de ce que proposera un TSMC ou un Samsung. Et qui sera disponible qui plus est avec un retard d'au moins 6 mois, et possiblement plus, par rapport au planning - certes incroyablement agressif - de TSMC.

Si la CEO d'AMD, Lisa Su, se satisfait dans le communiqué des développements "à long terme" de GlobalFoundries, cette annonce assez peu flatteuse du fondeur explique probablement pourquoi il a accepté de lâcher du lest auprès d'AMD. Nous vous en parlions en détail en début de mois, AMD et GlobalFoundries ont renégocié leur Wafer Supply Agreement avec pour résultat la levée de multiples clauses d'exclusivités qui liaient les deux sociétés.