Les contenus liés au tag 5nm

10/7nm en avance pour TSMC, EUV pour le 5nm

TSMC vient de publier ses résultats financiers pour le troisième trimestre. Le fondeur taiwannais enregistre une hausse séquentielle de 17% (+22% par rapport à la même période sur 2015), au dessus de ses prévisions. Des bons chiffres qui s'expliquent selon TSMC par une forte demande sur le marché des smartphones.

Ramenés par process, le 16/20nm représente 31% des revenus de la société (contre 23% le trimestre précédent). Le 28nm voit sa part baisser à 24% des revenus, mais TSMC confirme que ses usines restent "pleinement utilisées".

En ce qui concerne les prochains nodes, TSMC a confirmé les informations publiées un peu plus tôt, à savoir l'avance prise par les process 10 et 7nm.

Le 10nm entre en production ce trimestre et les premiers produits finaux seront livrés au premier trimestre 2017. Ce node ne sera pour rappel utilisé que par les très gros clients de TSMC, à savoir Apple et possiblement Qualcomm. Les autres clients attendront le 7nm. La montée des yields est décrite comme "similaire" à celle du 16nm même si "techniquement plus difficile".

Le 7nm entrera en production "risque" au premier trimestre 2017 et TSMC s'empresse d'indiquer qu'il sera utilisé non seulement pour les smartphones, mais aussi pour des GPU, des puces serveurs, et des "PC et tablettes". TSMC décrit des tapeout aggressifs qui commenceront au début du second trimestre. 15 produits devraient être qualifiés en 2017.

La fondeur a également évoqué le 5nm, qui a quitté le stade de la recherche pure pour entrer dans une phase de développement. Et TSMC confirme qu'ils utiliseront de manière "extensive" la lithographie EUV. Cette dernière aurait fait des progrès sur tous les plans, que ce soit en fiabilité, ou sur les problèmes techniques complexes (masques, photo resist, etc). La production "risque" reste prévue pour la première moitié de 2019 (la production volume suit en général de 3 à 4 trimestres).

Lors de la présentation des résultats aux analystes financiers, le CEO de TSMC, Mark Liu, a réitéré une fois de plus voir "l'informatique haute performance" comme un marché sur lequel TSMC espère voir une progression de ses ventes. Les serveurs et les PC clients sont mis en avant, et on a du mal a ne pas y voir un lien avec les annonces d'AMD sur sa renégociation du contrat WSA qui les lie à GlobalFoundries.

Dans la séance de questions/réponses posées, on notera qu'a la question de savoir si la prise de licence ARM par Intel est un risque, Mark Liu estime surtout que cela renforce le rôle d'ARM, tout en ne négligeant pas le rôle qu'Intel pourrait jouer. Reste que sur ce trimestre, la part de marché de TSMC chez les fondeurs (hors activité propre comme Intel pour ses propres puces donc) était de 55%.

Un transistor 1nm fonctionnel

La revue scientifique Science a publié la semaine dernière un papier de l'université de Berkeley évoquant leur recherche sur de nouveaux types de transistors.

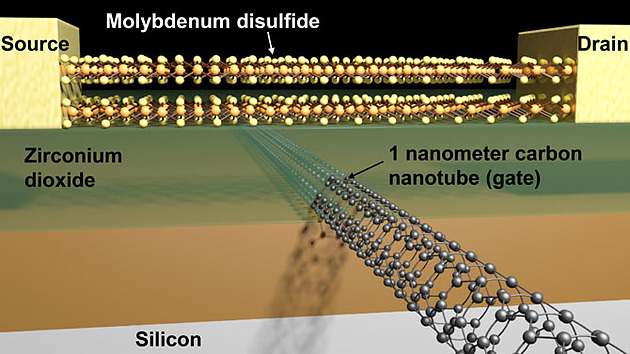

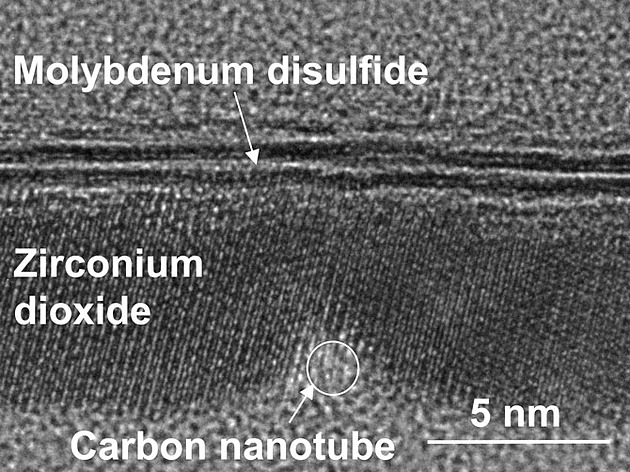

Réalisé par un laboratoire de l'université de Berkeley (en partenariat avec le département américain de l'énergie), le papier évoque un transistor utilisant de nouveaux matériaux pour remplacer le silicium.

Le laboratoire utilise du disulfure de molybdène (MoS2) pour remplacer le silicium pour la construction principale du transistor. La partie diélectrique de la grille est en dioxyde de zirconium (ZrO2) et la grille en elle même ("l'interrupteur" du transistor) est remplacée par un nanotube de carbone. En pratique la largeur de la grille est d'environ 1 nm.

Théoriquement le MoS2 apporte plusieurs avantages par rapport au silicium, avec une réduction de deux ordres de grandeur des courants de fuites sous les 5nm (on considère en général que 5nm est la limite à partir de laquelle il sera indispensable de changer de matériaux pour les semi conducteurs).

Pour ce prototype, un long nanotube de carbone a été placé par dépôt chimique en phase vapeur. Le procédé de fabrication reste excessivement complexe (en mettant de côté la fabrication également complexe des nanotubes de carbone), et les auteurs de la recherche admettent que la quantité de barrières techniques à surmonter pour imaginer une fabrication en volume est très élevée. Malgré tout, le transistor fabriqué était fonctionnel.

Si la prouesse doit être saluée, on doit noter que le MoS2 n'est pas forcément le matériau idéal pour remplacer le silicium. Si les courants de fuite sont fortement en baisse, c'est aussi parce que les électrons y ont une masse effective largement plus élevée. En pratique, la mobilité des électrons dans le MoS2 est généralement considérée comme très mauvaise ce qui se traduit par une vitesse des transistors réduite. Un point qui n'est pas nouveau mais qui est mis de côté par les auteurs du papier.

D'autres matériaux plus prometteurs sont considérés par les acteurs du marché, on sait par exemple qu'Intel a effectué beaucoup de recherche sur l'Arséniure de Gallium-Indium (InGaAs) ou le Phosphore d'Indium (InP) qui pourraient apparaître dans l'un des prochains process du constructeur. TSMC et Samsung s'intéressent également de près à ces nouveaux matériaux que l'on attend probablement autour de 5nm.

L'EUV possiblement pour le 7nm ?

Le site SemiWiki nous rapporte quelques informations sur l'état de la fabrication EUV, en provenance de la conférence SPIE Advanced Lithography qui se tient actuellement à San José.

Lors de la même conférence l'année dernière, les nouvelles étaient pour rappel plutôt bonnes (voir le lien pour un rappel complet sur la fabrication des processeurs et l'importance capitale de l'EUV !) et l'on espérait une introduction en cours de process pour le 10nm, et une introduction complète à 7nm. Malheureusement, on le rappelait en janvier, TSMC avait calmé les ardeurs en indiquant qu'il faudrait attendre le 5nm pour une éventuelle introduction de cette technologie.

SemiWiki confirme certains chiffres donnés lors de la dernière conférence aux investisseurs de TSMC, à savoir que la machine avait atteint sur une période de quatre semaines une production de 518 wafers/jour, un niveau encore largement insuffisant. Intel a partagé également quelques chiffres, un peu inférieurs à ceux de TSMC, à savoir entre 2000 et 3000 wafers par semaine (285-428 par jour).

On notera quand même que le taux de disponibilité des scanners de la société ASML a augmenté, passant de 55 à 70% chez TSMC (Intel rapportant une disponibilité identique) ! On notera que s'il est question d'une introduction en début de node à 5nm, TSMC laisse la porte ouverte pour le 7nm si jamais des progrès étaient effectués. Intel de son côté n'a pas donné d'information. Samsung envisagerait l'introduction à 7nm selon les présentations, sans plus de précisions.

Si la question de la disponibilité est importante, celle de la puissance de la source lumineuse l'est encore plus. Après avoir été limité à 40 watts l'année dernière, les machines actuellement en évaluation chez TSMC disposent désormais de sources 80 watts. C'est mieux, mais cela reste loin des 250 watts promis par ASML pour fin 2015. Les dernières prédictions sont désormais de 250 watts en 2016-2017, et au delà en 2018-2019, des plages particulièrement larges.

Atteindre les 250 watts de puissance permettrait d'augmenter significativement la cadence de production, atteignant 170 wafers/heure en théorie. ASML a effectué des démonstrations que TSMC et Intel semblent juger prometteuses de 185 et 200 watts. Reste à les voir en production, bien évidemment. Les challenges de cette technologie restent complexes et ne se limitent pas à ces deux points cruciaux, la question des défauts dans les masques est elle aussi importante même si là aussi TSMC et Intel ont visiblement noté quelques progrès. Vous pouvez retrouver plus de détails sur ces points dans l'article de SemiWiki .

TSMC vise 2020 pour le 5nm via l'EUV

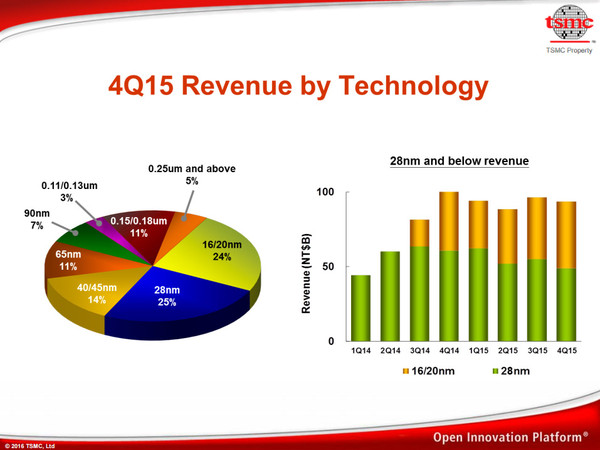

TSMC a présenté ses résultats pour le dernier trimestre 2015, pour une fois ils sont en baisse avec des ventes et un bénéfice qui baissent respectivement de 8.5 et 8.9%. La part du 16/20nm dans les revenus est en hausse, passant sur trois mois de 21 à 24%, ce qui se fait surtout au dépend du 28nm qui passe de 27 à 25%.

Le fondeur se montre confiant pour l'année à venir, indiquant qu'il devrait passer de 40% de parts de marché sur les process 16/14nm à plus de 70% en 2016. Cela se fera via 16FF+ (FinFet+) destiné aux produits les plus performants mais aussi nouveau 16FFC (FinFet Compact) pour le moyen de gamme et la basse consommation.

Pour le reste TSMC a confirmé le 10nm pour 2017, sans donner de date précise. Il y a trois mois il était question d'un début de la production en volume au dernier trimestre 2016 et de premiers revenus au premier trimestre 2017. La production en volume en 7nm a été annoncée pour le premier semestre 2018, et il faudra attendre 2 années supplémentaires avant de voir débarquer le 5nm. Le 5nm devrait finalement être le premier à utiliser l'EUV, mais TSMC travaille encore avec ASML à fiabiliser les machines : il a ainsi pu atteindre sur une période de 4 mois une moyenne de 500 wafer exposés par jour on est assez loin des 1000 wafer qu'elle peut atteindre en pointe.