Les contenus liés au tag 10nm

Afficher sous forme de : Titre | FluxIntel densifie sa SRAM 14nm et parle du 10 et 7nm

TSMC, résultats et point sur les 20nm, 16nm et 10nm

Le 16nm de TSMC en avance sur son retard

TSMC et ARM partenaires pour le 10nm

Le 16nm en retard chez TSMC

16nm à l'heure, EUV en retard pour TSMC

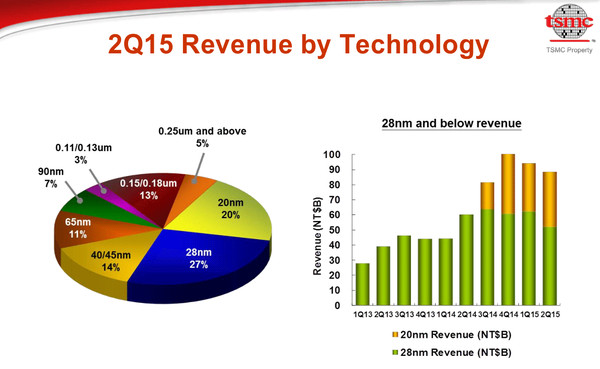

TSMC a également annoncé ses résultats financiers. La société a enregistré pour le second trimestre un chiffre d'affaire de 6.62 milliards avec une marge brute atteignant 48.5%. Par rapport au même trimestre l'année dernière, cela représente une hausse de 12.2% du CA (et 33% pour les bénéfices).

Au-delà des chiffres, TSMC a donné quelques détails intéréssants, confirmant d'abord la cession de sa participation dans ASML qui avait été annoncée en janvier, en assurant que cela ne changeait strictement rien à ses liens avec la société basée aux Pays-Bas. TSMC a également cédé 5% de sa participation dans Vanguard (VIS), un spinoff de TSMC proposant des services spécialisés. TSMC garde malgré tout le contrôle de 28% de VIS, étant toujours l'actionnaire majoritaire.

Le 28nm continue de représenter 27% des revenus tandis que le 20nm aura représenté 20% des revenus sur le second trimestre. TSMC note cependant que côté smartphones, les inventaires chez les constructeurs sont importants, particulièrement sur les produits d'entrée et milieu de gamme faute d'augmentation de la demande en Chine et dans les marchés émergeants. Le dollar elevé est l'une des causes mises en avant, tout comme les situations économiques locales. Tous ces facteurs font que TSMC s'attend à voir une hausse de son activité possiblement plus mesurée qu'ils ne le pensaient.

La nouvelle la plus importante est la confirmation que le 16nm est bel et bien en cours de production et que les premières puces ont été livrées ce mois-ci. Sur le 16nm, TSMC indique que la montée en puissance de son process sera extrêmement rapide, plus rapide que le 20nm profitant du BEOL (la seconde partie du process qui gère les interconnexions, plus de détails ici ) commun. Les taux de défauts sont annoncés comme extrêmement bas, et la courbe de réduction des défauts est la meilleure jamais obtenue par TSMC.

La société pense rafler en 2016 la majorité du marché 16nm. Les premiers clients en volume de TSMC sur le 16nm sont très probablement Apple (qui utiliserait aussi Samsung selon les rumeurs pour son A9) et Qualcomm qui ont en général la priorité sur les nouveaux nodes, même si AMD a annoncé avoir effectué deux tapeout sur ce process (sans préciser s'il s'agissait bien de TSMC, ou de GlobalFoundries).

TSMC a également profité de l'occasion pour parler du 10 et du 7nm. Selon TSMC les progrès réalisés sur le 10 nm sont « très encourageants » et continue de prévoir un début de la production en volume fin 2016. Une date qui, si elle est effectivement tenue, placerait potentiellement la sortie de produits 10nm en volume chez les très bons clients de TSMC avant même la sortie de Cannonlake chez Intel. Encore faut-il que TSMC tienne ses délais, bien évidemment, mais sur les deux derniers nodes cela a plutôt été le cas. Techniquement par rapport au 16 FinFET+ (la version la plus avancée de son process FinFET), le 10nm apporte 15% de vitesse à puissance égale, ou 35% d'économie d'énergie à vitesse égale. La densité est 2.2x celle du 16 FinFET+.

On notera avec intérêt que pour le 10nm, TSMC annonce des tape out sur un tas de secteurs, y compris ce qu'ils appellent high-performance computing, sous-entendu des CPU/SoC. Morris Chang, le chairman de TSMC est même allé un peu plus loin indiquant qu'il pense que TSMC va jouer un rôle important sous peu dans les marchés notebook et serveur, à condition de lier trois acteurs. Non seulement une fonderie (TSMC), ARM, mais aussi des sociétés capables de faire des designs custom « haute performance ».

TSMC a également évoqué le 7nm, s'attendant à lancer la qualification de son process au premier trimestre 2017, soit seulement cinq trimestres après la qualification attendue du 10nm. Le fondeur n'est pas très précis sur la technique, indiquant profiter de la maturité du 10nm pour mettre en place le 7nm, ce qui sous entends peut être que de la même manière qu'ils l'ont fait pour le 16nm avec le 20nm, TSMC pourrait garder le BEOL du 10nm sur le 7nm. Cela expliquerait très certainement le délai très réduit entre les qualifications.

Concernant l'EUV, Mark Liu, l'un des Co-CEO a indiqué que la porte était toujours ouverte et qu'ils travaillaient activement avec ASML, mais qu'il restait encore des challenges à résoudre, particulièrement autour des masques. Il a également indiqué que le 7 nm n'utiliserait « probablement pas » l'EUV dans un premier temps mais qu'il pourrait être introduit dans un second temps, et qu'il serait introduit dès le début à 5nm. Un changement de position et une mauvaise nouvelle pour ASML - par rapport au discours habituel qui indiquait que l'EUV serait possiblement introduit dans un second temps à 10nm et dès le début à 7nm.

Intel abandonne le Tick-Tock, confirme Kaby Lake

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

Au milieu de l'annonce de nouveaux retards sur sa roadmap mobile (notamment SoFIA LTE qui est désormais attendu pour la première moitié de 2016), Brian Krzanich a indiqué que la transition d'un node à l'autre ne tenait plus réellement le rythme des 24 mois que le constructeur souhaitait s'imposer, mais que sur les deux générations précédentes, il était plus proche des deux années et demi. En conséquence, la stratégie du Tick-Tock doit s'adapter et il aura confirmé l'arrivée d'un troisième produit 14 nm, Kaby Lake qui sera lancé durant la seconde moitié de 2016 (comme on le pressentait le mois dernier) !

Le CEO d'Intel décrit Kaby Lake comme « bâti sur les fondations de la micro architecture Skylake », mais « avec des améliorations clefs de performances ». Un phrasé relativement vague qui laisse entendre qu'il s'agirait d'un peu plus que d'un « Skylake refresh », sans vraiment s'engager (possiblement un nouveau GPU seulement ?). Le lancement de Cannonlake est lui bel et bien repoussé à la seconde moitié de 2017, en 10nm.

Interrogé (légèrement) sur le sujet par les analystes, Brian Krzanich a qualifié le retard par la complexité croissante de mise au point des process et que les difficultés du 10nm, si elles étaient similaires en pratique à celles rencontrées pour le 14nm, n'étaient pas directement liées au retard du 14nm. Intel est sur le sujet dans une position délicate puisque le constructeur a toujours clamé que le retard du 14nm n'aurait aucun impact sur le 10nm. Selon le CEO, la lithographie continue à être de plus en plus complexe, notamment à cause de l'augmentation des étapes de multi-patterning. En marge de cela, il aura rappelé que le 10nm d'Intel sera une solution sans EUV (le reste de l'industrie ne s'attends pas non plus à disposer de l'EUV pour le 10nm).

Pour le CEO, rajouter Kaby Lake à la roadmap permet d'améliorer la « prévisibilité » pour ses partenaires. Un argument qui ne manque pas d'ironie quand l'on connait l'historique du Tick-Tock chez Intel. La stratégie du Tick-Tock avait été mise en place en interne chez Intel au début des années 2000 par Pat Gelsinger dans le but de mettre de l'ordre dans le développement parfois anarchique des architectures qui a conduit à de nombreux projets et architectures repoussés et abandonnés. En interne, il s'agissait de délimiter clairement le périmètre de deux équipes de développement d'architectures, une située en Oregon et l'autre en Israël. Le tout articulé autour des changements de process tous les deux ans.

Ainsi chaque nouveau passage à un process (65 vers 45 nm, etc) serait un Tick. Une version légèrement modifiée de l'architecture précédente, portée vers le nouveau node (ce que l'on appelle un die shrink), tandis que la « nouvelle architecture », le Tock serait lancé l'année suivante, lorsque le process de fabrication serait arrivé à maturité.

Historiquement, ce n'est qu'avec beaucoup de créativité que le constructeur aura pu compter 24 mois entre chaque node, des retards de plusieurs mois ayant été observés au fil des années mais globalement jusqu'ici Intel s'était imposé de tenir le modèle de deux produits principaux (on met de côté les produits/architecture dédiées spécifiquement à la mobilité) par node sur environ deux ans.

Avec le 14nm le modèle n'était plus tenable, obligeant en 2014 Intel à proposer un Haswell refresh, simple « speed bump » d'Haswell, lancé en juin 2013 en lieu et place de Broadwell. En pratique si Intel s'est targué d'avoir « lancé » le 14nm en 2014, il s'agissait d'un seul processeur, le Core M, qui plus est dans un stepping remplacé avant même sa sortie ! Et pour le desktop, la gamme Broadwell aura été réduite au minimum avec seulement deux modèles, lancés le mois dernier pour tenir les annonces. Avec au final un retard d'un an sur la cadence que s'imposait jusqu'ici Intel.

En pratique Skylake (le tock original 14nm) est toujours attendu pour cette année même si Intel n'a pas encore confirmé de quelle manière s'effectuerait son lancement. Il a été indiqué par Intel qu'une des conséquences du ralentissement de l'activité en Q2 était un inventaire encore important, laissant penser que le constructeur pourrait repousser certains SKU de Skylake. Le lancement des modèles K était prévu pour rappel pour le 5 aout, tandis que le reste de la gamme 4 curs était attendue entre le 30 aout et le 5 septembre. On ne s'étonnerait pas de voir ces références repoussées de plusieurs semaines afin d'écouler les inventaires existants, même si Intel ne l'a pas dit clairement.

On notera également qu'au détour d'une question, Brian Krzanich a confirmé que le 10nm d'Intel utiliserait toujours des FinFET, et non un autre type de structures comme certaines rumeurs avaient pu le laisser entendre. Il a indiqué que le 10nm serait la troisième génération de FinFET d'Intel. A une autre question il a indiqué que des changements de matériaux étaient par contre attendus sans les préciser.

Interrogé enfin sur l'impact de ces retards sur « l'avance » d'Intel en matière de process par rapport au reste de l'industrie, Brian Krzanich s'est voulu rassurant, indiquant que l'avance d'Intel ne diminuerait pas sur le reste de l'industrie. De notre point de vue, il est probable que TSMC, et possiblement Samsung lancent une production en volume autour, voir même un peu avant Intel. Ce qui serait, au moins pour l'image, un véritable drame pour la firme de Santa Clara.

Cannonlake 10nm retardé à 2017, Kaby Lake pour 2016 ?

Selon Benchlife.info , Intel sera en retard sur Canonnlake, qui est pour rappel un "tick" en 10nm de Skylake. Afin d'avoir tout de même une nouveauté à se mettre sous la dent en 2016, une nouvelle ligne de processeur 14nm, Kaby Lake, serait à l'ordre du jour.

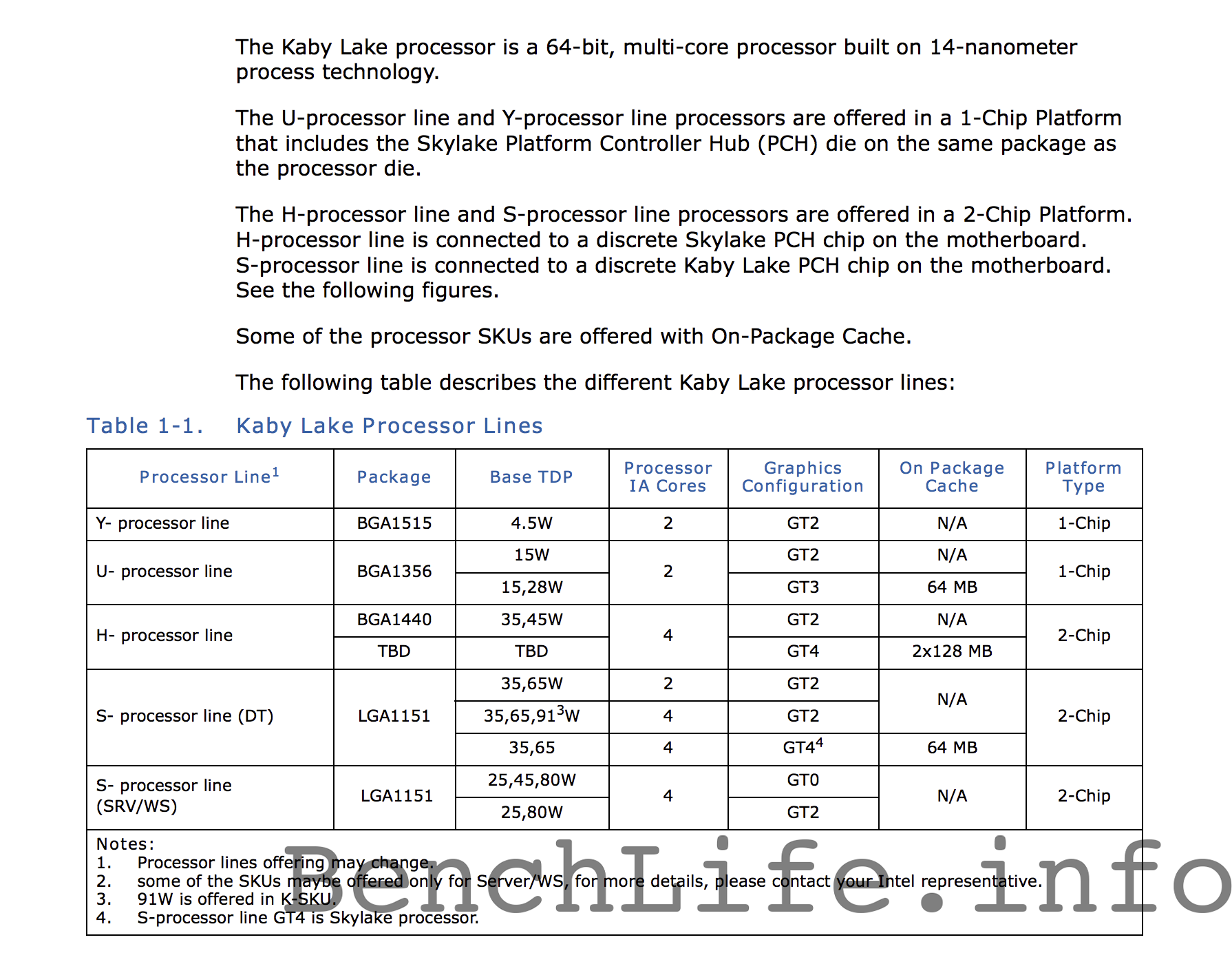

Comme d'habitude de nombreuses déclinaisons sont listées mais on ne sait pas vraiment en quoi ces processeurs seront différent des Skylake. S'agit-il d'un simple speed bump comme nous l'avons déjà connu avec Haswell Refresh ? Seule vraie nouveauté apparente, au format BGA en gamme H une puce est listée avec 2x128 Mo d'eDRAM embarquée, contre au mieux 128 Mo sur Broadwell et Skylake, ce qui devrait permettre d'augmenter les performances de l'iGPU.

Sur desktop on reste en LGA 1151 avec 2 à 4 curs, avec 35/65W en 2 curs et 35/65/91W en 4 curs. Le TDP de 91W concerne les processeurs en version K, ce chiffre est assez étrange puisqu'il est censé être de 95W sur le Skylake K. Intel prévoit également de sortir des versions 4 curs LGA 1151 accompagnées de l'iGPU soit GT4, qui intègre 72 Executions Units (soit 50% de plus que sur un GT3 Skylake ou Broadwell), et de 64 Mo d'eDRAM. Autre bizarrerie alors que ce tableau est censé représenter la ligne de processeurs Kaby Lake ces versions sont annotées comme étant des Skylake !

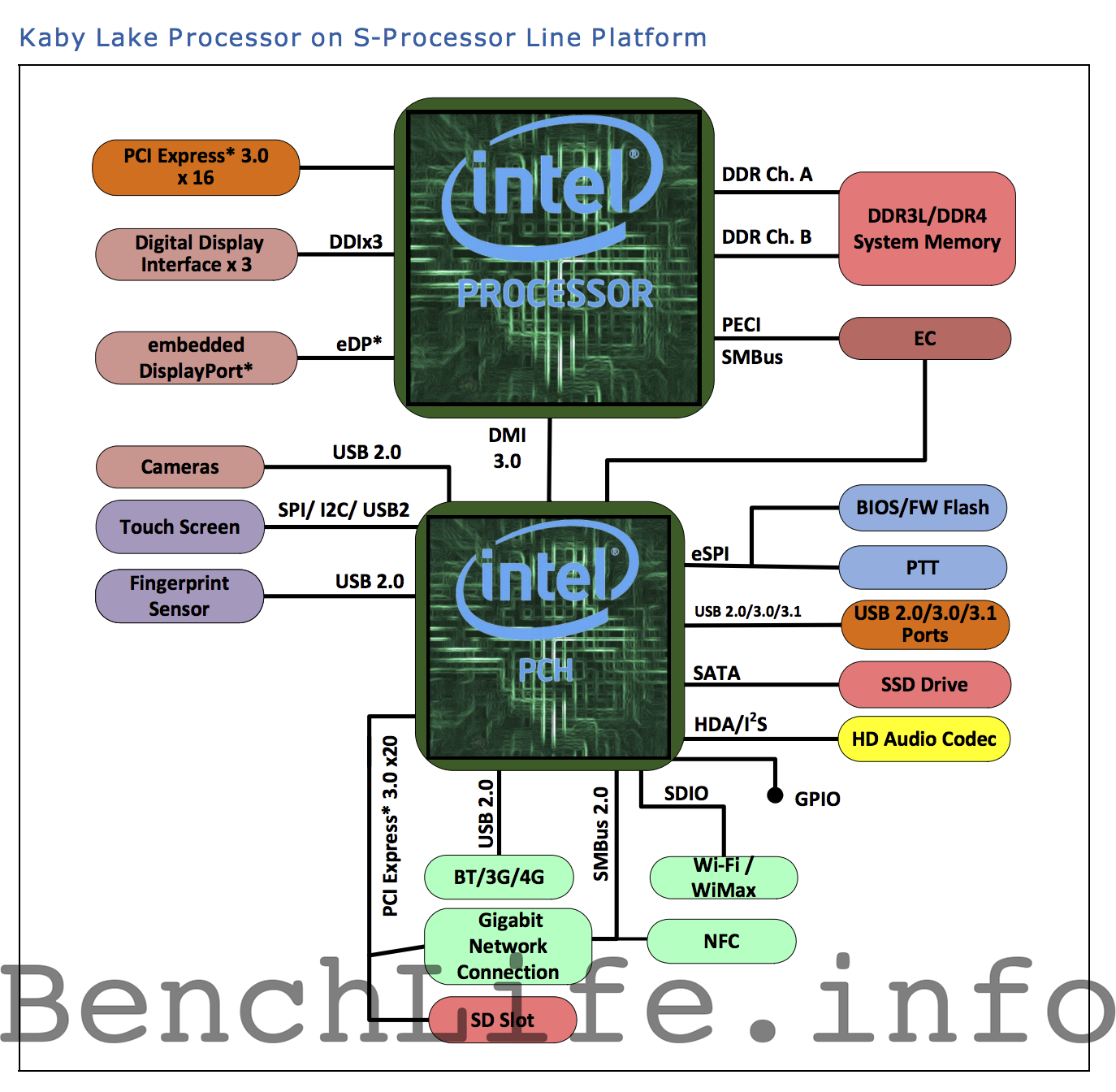

Côté chipset le diagramme laisse penser qu'on aura droit à une nouveauté avec l'arrivée de l'USB 3.1 qui pour rappel double les débits pour atteindre 800 Mo /s en pratique (cf. notre focus). Une mise à jour mineure mais qui permettra à tous les fabricants de cartes mères de sortir leur nouvelle gamme annuelle même en l'absence de nouveauté importante, comme ce fut le cas à l'époque du Z97.

Après un passage au 14nm retardé, Intel connaitrait-il des déboires sur le 10nm ? C'est ce qu'on peut penser si le retard de Cannonlake se confirme, ce qui augure d'une année 2016 assez morose côté CPU chez Intel, alors qu'on attend dans le même temps le retour sur le devant de la scène d'AMD avec Zen !

ASML vend 15 machines EUV à Intel

La société ASML s'est fendu hier d'un communiqué de presse pour indiquer avoir signé un accord important pour la vente de machines de lithographie EUV. Nous étions revenus sur le sujet à la fin du mois dernier, après de long et multiples retards, cette technologie de lithographie nouvelle génération avait effectué quelques progrès substantiels, notamment chez TSMC, qui avait commandé deux machines NXE:3350B livrables cette année, des machines dédiées au 10nm.

Le communiqué d'ASML indique que la firme néerlandaise a trouvé un accord avec un de ses « gros client américain » pour livrer, dans un délai non précisé, 15 machines EUV. Deux de ces machines au moins seront de type NXE:3350B (10nm) et seront livrées cette année.

Il ne faut pas trop d'imagination pour deviner que le client en question est Intel. La société avait investi de manière importante dans ASML en 2012 même si elle restait prudente sur l'utilisation à venir de la technologie. Cet accord semble montrer un regain d'intérêt autour de l'EUV, même si à l'image de TSMC on s'attend probablement à un déploiement initial autour du 7nm.

La cadence de production des machines sera en effet étalée dans le temps. Six (à huit) machines NXE:3350 devraient être vendues cette année (deux à Intel, deux à TSMC et possiblement deux à Samsung qui était le troisième à avoir investi dans ASML en 2012). La production devrait s'intensifier progressivement puisque ASML table sur la production de douze machines en 2016, vingt-quatre en 2017 et 48 en 2018.

On notera enfin que si l'intérêt autour de l'EUV se porte aujourd'hui pour la fabrication de circuits logiques (processeurs), ASML compte également déployer l'EUV auprès des fabricants de mémoire DRAM dans un second temps. La production de mémoire flash NAND en EUV pourrait suivre avec un décalage de deux à trois ans selon le CEO d'ASML.

Quelques (bonnes !) nouvelles de l'EUV

Il y a quelques semaines se tenait le symposium « Advanced Lithography » du SPIE , une organisation internationale qui se focalise sur les challenges des technologies optiques et photoniques. Antony Ten de TSMC y a tenu une présentation ou il est revenu sur les avancées de la technologie de lithographie EUV (Extreme Ultraviolet Lithography).

L'EUV représente une évolution majeure, attendue depuis très longtemps dans le monde de la fabrication des semi-conducteurs. Déjà en 2002, Intel passait sa première commande auprès d'ASML pour une machine destinée à être livrée de 2005. 10 ans après cette échéance, l'avènement de l'EUV ne s'est toujours pas fait même si les dernières nouvelles rapportées par TSMC semblent plutôt prometteuses.

ASML est le fabricant d'outil qui a misé depuis le début sur les EUV, les autres acteurs ayant jeté l'éponge

Pour rappel, les processeurs sont fabriqués via ce que l'on appelle la photolithographie , un mécanisme qui permet, via de multiples opérations successives de transférer un masque sur une galette de silicium (communément appelé wafer) en utilisant une source lumineuse. Une version high tech d'une photocopieuse utilisée pour effectuer des réductions en quelque sorte. Actuellement la source lumineuse utilisée pose problème à l'industrie. D'une longueur d'onde de 193nm, elle est générée par des lasers à exciplexe (Argon/Fluor). Elle traverse une série d'éléments optiques pour la focaliser et sert à exposer des solutions photorésistantes qui ont été déposées préalablement pour dessiner sur le wafer. Des étapes qui prennent individuellement un certain temps et qui se multiplient pour chacune des couches qui composent les semi-conducteurs. De bout en bout (et cumulé à toutes les autres étapes de la chaine) il faut entre 2 et 3 mois pour obtenir un produit final.

Les réductions de géométrie successives (on atteint aujourd'hui 14/16nm et bientôt 10nm) complexifient les systèmes de réduction ce qui fait que chaque node apporte ses challenges depuis quelques années tant il devient impossible d'atteindre une netteté parfaite sous les 50nm. Pour compenser cela, des techniques (lithographie à immersion, multiple patterning, etc) sont utilisées ponctuellement pour les couches les plus importantes des puces. A l'approche du 10nm, une généralisation du multi patterning (qu'on pourrait simplifier à passer deux fois une feuille dans une photocopieuse quand on a un toner défaillant pour la rendre lisible) devient obligatoire ce qui augmente les temps, crée de nouveaux problèmes (d'alignement notamment), impose des règles de design strictes dans la manière dont les ingénieurs doivent placer les transistors, et donc augmente les couts.

Avec une longueur d'onde de 13.5 nm, l'EUV promet de simplifier les systèmes optiques (bien qu'elle engendre de nouveaux problèmes, évidemment !) mais c'est la génération de cette lumière qui pose problème. La technique en elle-même est très complexe puisque des goutes microscopiques d'étain sont envoyées dans une chambre sous vide avant d'être vaporisées individuellement par un laser extrêmement puissant pour produire cette lumière UV extrême qui est enfin collectée et focalisée avant de pouvoir être utilisée. Le tout à une cadence de 50000 goutes par seconde. Une complexité qui empêchait d'atteindre en production de manière constante il y a un an de cela - une puissance dépassant les 10 watts d'après TSMC durant le même symposium SPIE.

Le rachat de la société Cymer (qui fournit des sources lumineuses a l'industrie) par la société ASML (qui développe pour rappel les outils EUV) en 2013 semble cependant enfin porter ses fruits puisque ASML avait annoncé en juillet, puis en septembre que deux de ses clients avaient réussis à exposer plus de 500 wafers sur une durée de 24 heures via leur machine NXE:3300B, équipée alors d'une source d'une puissance de 40 watts.

Mieux, TSMC a annoncé durant le symposium SPIE avoir pu faire fonctionner pendant 24 heures d'affilée sa machine NXE:3300B équipée d'une source de 80 watts (la seule au monde équipée aujourd'hui de cette source puissante). Durant cette période elle a pu exposer 1022 wafers ce qui donne un rapport wafer/heure de 42.58, un chiffre qui s'approche fortement des « 50 à 100 par heure » qu'évoquait Mark Bohr en 2012 pour commencer à considérer l'EUV.

L'imposante NXE :3300B d'ASML

Des progrès importants qui ont valu à TSMC d'indiquer que l'utilisation de l'EUV pour le 7nm était une possibilité, et qu'introduire l'EUV dans un second temps dans son process 10nm, pour certaines couches critiques n'était pas impossible. La roadmap d'ASML promet d'augmenter la puissance à 125 watts à la fin du second trimestre avec la source de lumière du NXE:3350B et même 250 watts avant la fin de l'année.

Si ces nouvelles sont dans l'absolu très bonnes, et un pas en avant très important pour l'EUV, d'autres problèmes restent à régler. Le site SemiWiki rappelle que dans cette même présentation, TSMC indiquait que le taux de disponibilité de leur machine NXE:3300B version 40 watts, sur un test prolongé de 8 semaines n'était « que » de 55%. Un chiffre que l'on doit là encore à la source lumineuse, le générateur de goutes d'étain devant être remplacé tous les 4 jours. La prochaine version de la source lumineuse fournie par Cymer promet de résoudre ce problème même s'il faudra voir dans quelle mesure. Un système de nettoyage automatique de la partie optique devrait également améliorer la disponibilité.

Dans tous les cas cette avancée de l'EUV est importante et si d'autres problèmes périphériques seront à résoudre, une des plus grosses épines dans le pied de l'EUV semble enfin s'envoler, laissant penser que la technologie pourrait enfin s'approcher d'une mise en production possible ! Quelque chose que l'on pourra confirmer au milieu de l'année, TSMC ayant commandé deux machines NXE:3350B dédiées au 10nm. Ses deux machines existantes seront également mises à jour. Le tout dans le but de les aider à préparer une introduction éventuelle sur leur process 7nm, possiblement à l'horizon 2017.