Les contenus liés au tag HBM

Afficher sous forme de : Titre | FluxFiji, HBM et interposer, un travail de longue haleine

IDF: Samsung lancera sa HBM en 2016

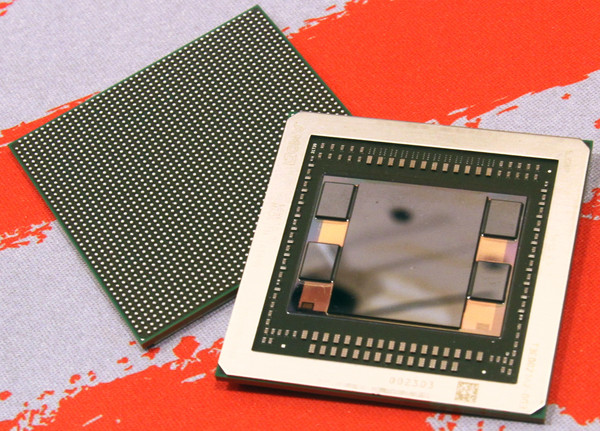

Dossier: AMD Radeon R9 Fury : Sapphire Tri-X et Asus Strix en test

Dossier: AMD Radeon R9 Fury X : le GPU Fiji et sa mémoire HBM en test

AMD annonce les Radeon R9 Fury X, Fury et Nano

La HBM2 4 Go Samsung en production

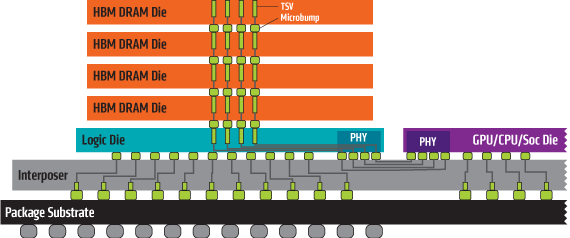

Samsung vient d'annoncer qu'il avait débuté la production en volume d'une puce HBM2 d'une capacité de 4 Go. Offrant une bande passante de 256 Go /s, elle est composée de 4 die de 1 Go empilés, chacun comprenant environ 5000 trous pour l'interconnexion via TSV. Par rapport à la HBM utilisée sur l'AMD Fury, la capacité est multipliée par 4 et la bande passante par 2. Le tout est gravé en process 20nm, Samsung indique qu'il devrait également produire une version 8 Go via 8 die empilés cette année.

Le JEDEC pose les bases de la HBM 2

Le JEDEC vient d'annoncer la publication d'une mise à jour de son standard concernant la HBM. Le document JESD235A, daté en fait de novembre 2015 remplace donc le JESD235 d'octobre 2013. Ce document pose les bases nécessaires à la HBM de seconde génération, avec des capacités par puce pouvant atteindre 8 Go via 8 dies empilés pour une bande passante de 256 Go /s via un bus 1024 bits. Pour rappel la HBM SK Hynix utilisée par AMD sur Fury est constituée de puces 1 Go à 128 Go /s.

Le standard intègre également un nouveau mode d'adressage qui permet de subdiviser les canaux 128 bits interne à la puce en sous-canaux de 64 bits ce qui permet de réduire la taille du prefetch et d'augmenter la bande passante effective. Ce mode de fonctionnement est optionnel pour les canaux de 1 à 4 Gb mais obligatoire en 8 Gb.

SK Hynix et Samsung sont sur les rails pour produire en volume de la HBM de seconde génération en 2016 afin d'offrir aux futurs GPU haut de gamme 14nm la bande passante qu'ils méritent.

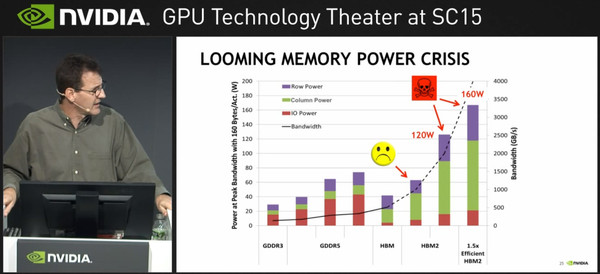

La VRAM des GPU trop gourmande dans quelques années ?

Lors du forum SC15, Nvidia a effectué une présentation concernant les pistes qu'il explorait afin d'arriver aux super-ordinateurs de type Exascale (capables d'effectuer au moins exaFLOPS) les plus efficaces possibles d'un point de vue énergétique. Si on n'apprend rien de précis concernant les architectures GPU à venir, le NVLink ou encore le support de la précision FP16 étant déjà connus, le constructeur a publié un graphique intéressant pour ce qui est de la consommation des différents type de mémoire.

Selon Nvidia, la HBM2 consommera ainsi jusqu'à 60 watts pour une bande passante de l'ordre de 1 To /s. Si son efficacité est en hausse par rapport à la HBM (40W pour 500 Go /s) et bien sûr la GDDR5 (75W pour 350 Go /s), il faut rappeler que la présence de la mémoire sur le même packaging fait que le GPU doit en contrepartie consommer moins sans quoi la densité de puissance à dissiper serait trop importante.

Si avec 60 watts pour la HBM2 la situation commencera à être problématique, Nvidia met en avant le fait que pour atteindre une bande passante de 2 To /s en HBM2 on arrivera à un niveau intenable de 120 watts. Même en envisageant une mémoire 1.5x plus efficace, pour atteindre une bande passante de 4 To /s qui devrait être nécessaire d'ici quelques générations de GPU on serait à 160 watts et il est bien entendu inimaginable d'attribuer autant de puissance à la mémoire.

S'il reste encore quelques années avant d'être confronté à ce problème grâce au remplacement de la GDDR5 par la HBM puis la HBM2, il faudra donc de nouvelles technologies mémoire pour accompagner l'augmentation en puissance des GPU. Le fabricant indique travailler sur le sujet, mais n'a dévoilé aucune piste à ce jour.

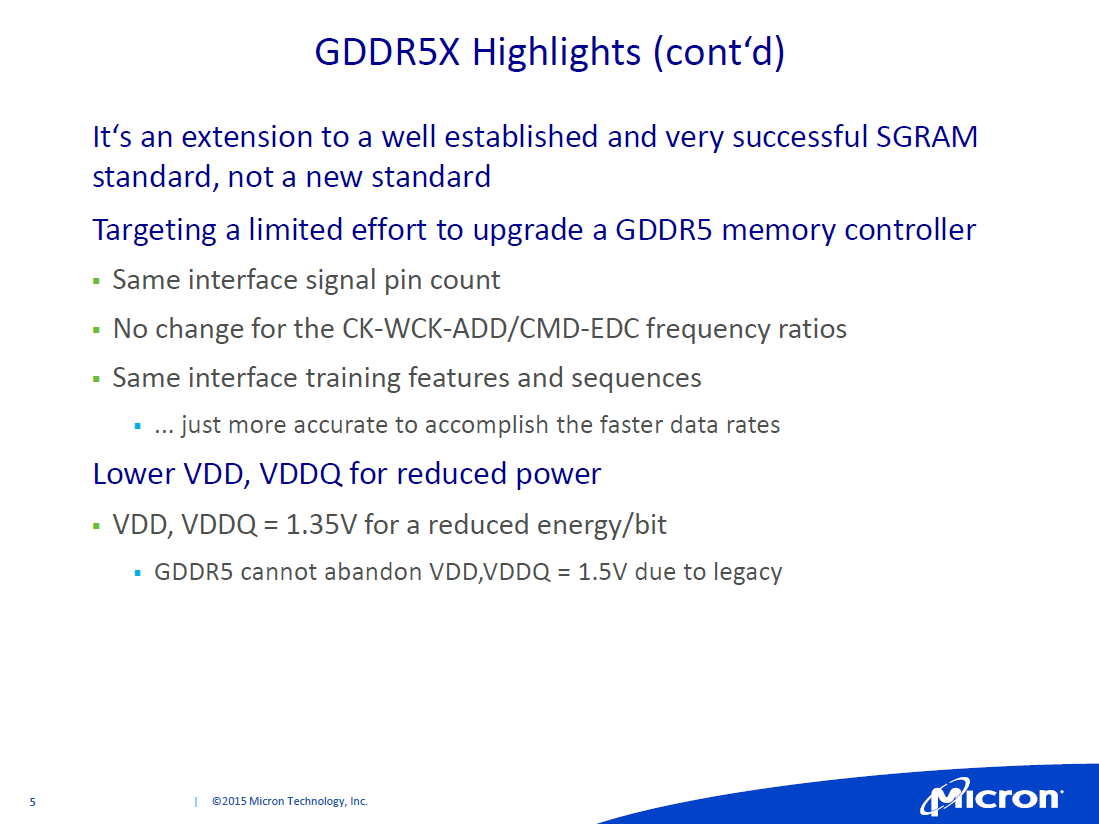

Micron mise sur la GDDR5X

Alors que Samsung a emboité le pas de Hynix sur la HBM pour ce qui est des mémoires proposant une bande passante élevée, Micron restait de son côté uniquement positionné sur la HMC, une mémoire plus coûteuse utilisant un bus moins large mais plus véloce mais qui a l'avantage de ne pas nécessiter d'interposer. Une alternative qui n'a ne semble-t-il pas réussi à convaincre sur le marché graphique.

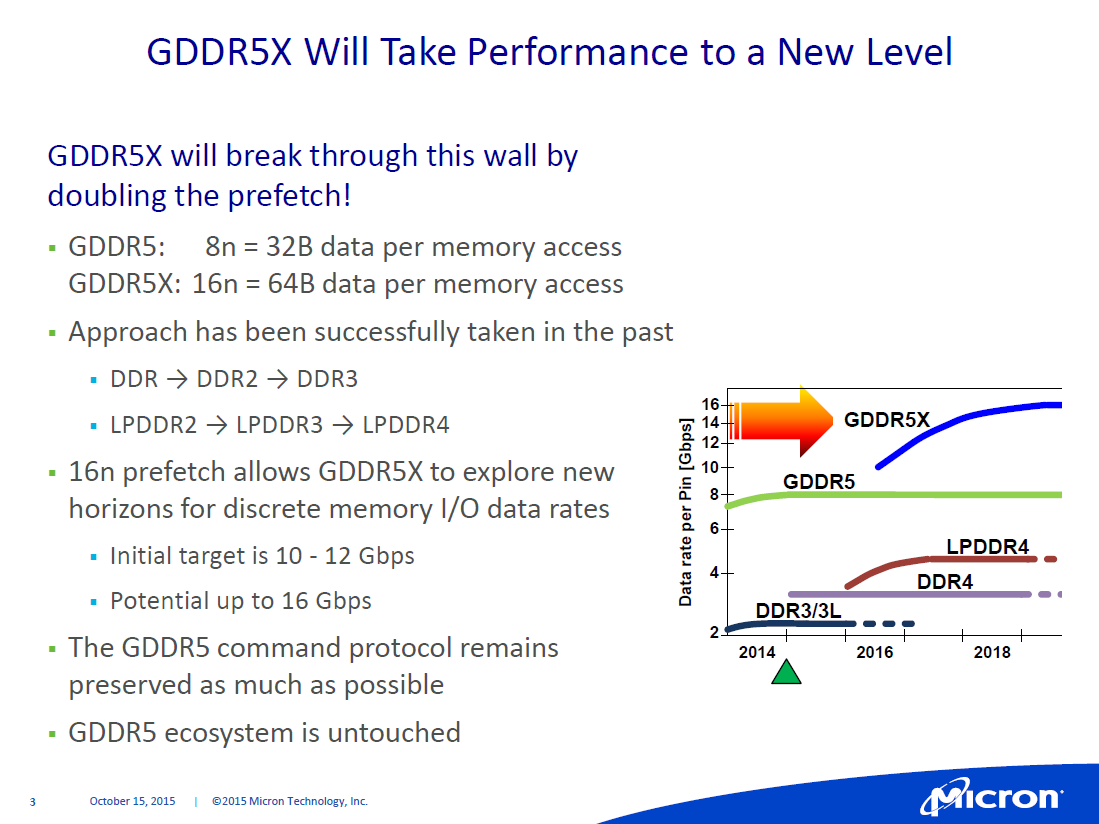

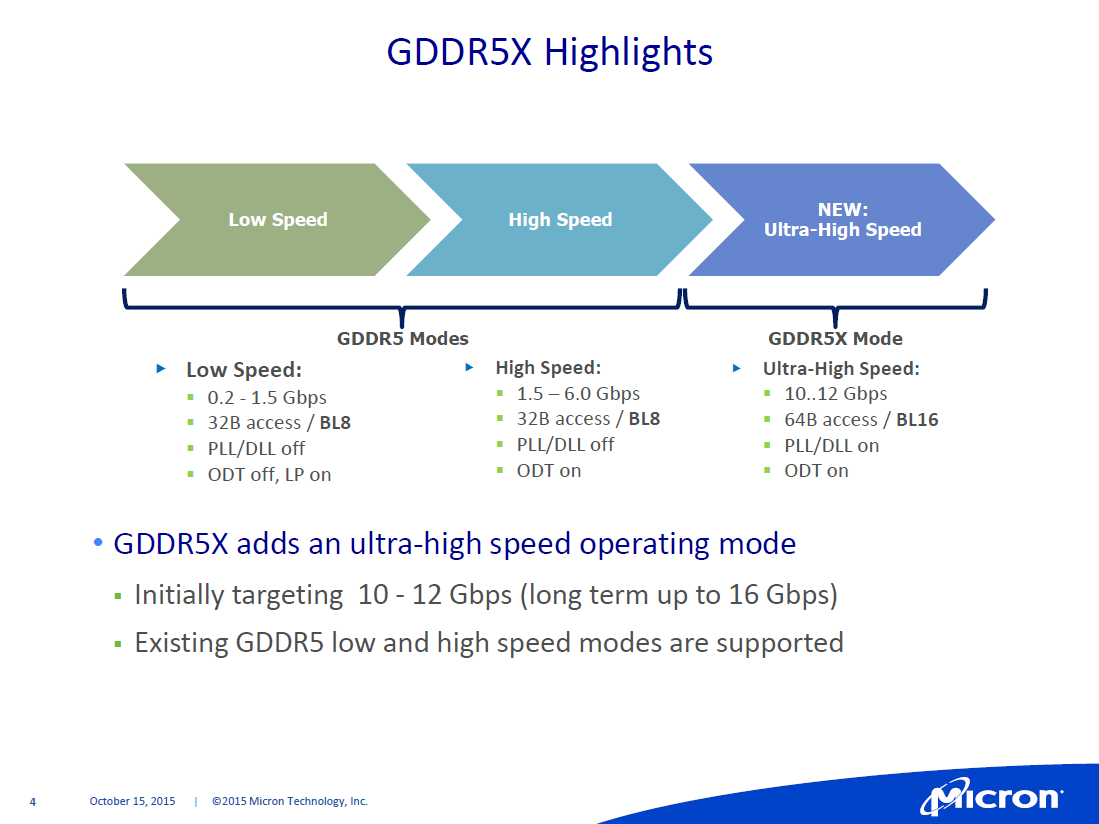

Micron se positionne du coup sur un nouveau type de mémoire dénommée GDDR5X dont le but est de doubler la bande passante par rapport à la GDDR5. Pour se faire Micron utilise la bonne vieille méthode du doublement du prefetch qui passe à 16.

La GDDR5X sera donc capable de lire 16 cellules mémoire en parallèle et de placer le tout dans un petit buffer qui déversera ses données en série et à très haute vitesse dans le bus mémoire. Cela augmente par contre la complexité de puces mémoire ainsi que la plus petite quantité de données qui peut être lue, une puce GDDR5 étant généralement 32-bit ce n'est qu'avec des accès de 512-bit par puce que les débits pourront être doublés.

Micron semble vouloir lancer la GDDR5X dès 2016, avec un débit de l'ordre de 10-12 Gbps alors que la GDDR5 atteint au mieux 8 Gbps à l'heure actuelle. D'ici 2018 Micron semble viser un doublement du débit par rapport à la GDDR pour atteindre 16 Gbps.

A terme avec un bus 256-bit on atteindrait donc les 512 Go /s, contre 1 To /s avec un bus 512-bit. Ces débits sont en fait comparable avec ceux qui seront offert par des configurations à 2 ou 4 puces utilisant les puces HBM de Samsung ou Hynix prévues pour 2016 qui seront moins gourmandes en énergie mais qui nécessiteront un interposer et pour lesquelles on peut se demander si elles pourront être produites dans les volumes nécessaires. Micron semble ouvrir une voie plus conservatrice pour l'augmentation de la bande passante pour les GPU, reste à voir si AMD ou Nvidia l'utiliseront l'an prochain.

Dossier : AMD Radeon R9 Nano, la carte Fiji compacte en test

AMD compte bien se démarquer de la concurrence en proposant pour la première fois une carte graphique haut de gamme ultra compacte destinée aux mini-PC. Cette Radeon R9 Nano trouvera-t-elle sa niche ?

[+] Lire la suite