Les derniers contenus liés aux tags HBM et GDDR5X

Samsung évoque la GDDR6

HMC, DDR5 et 3D XPoint pour Micron

La GDDR5X standardisée par le JEDEC

Micron mise sur la GDDR5X

Samsung évoque la GDDR6

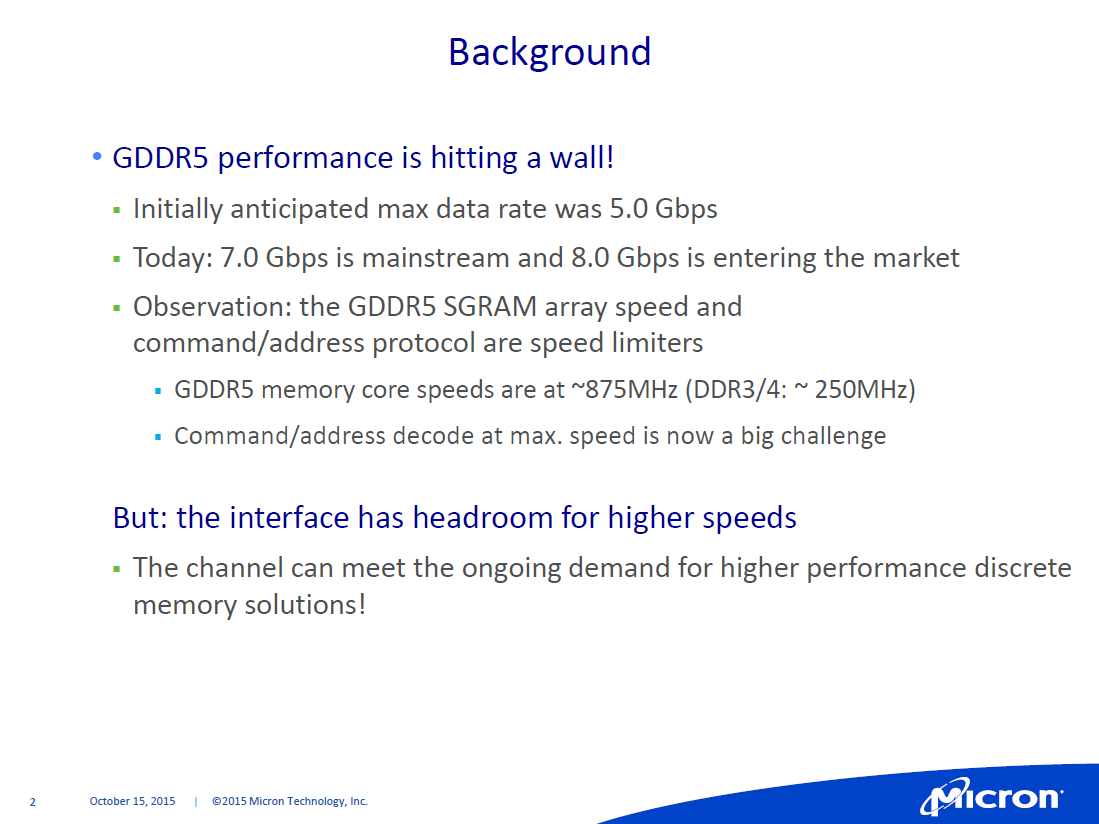

En parallèle à la mémoire HBM, Samsung à évoqué le futur de la GDDR5, ignorant quelque peu l'existence de la GDDR5X de Micron qui, bien que standardisée par le JEDEC, n'a pas été adoptée par ses concurrents.

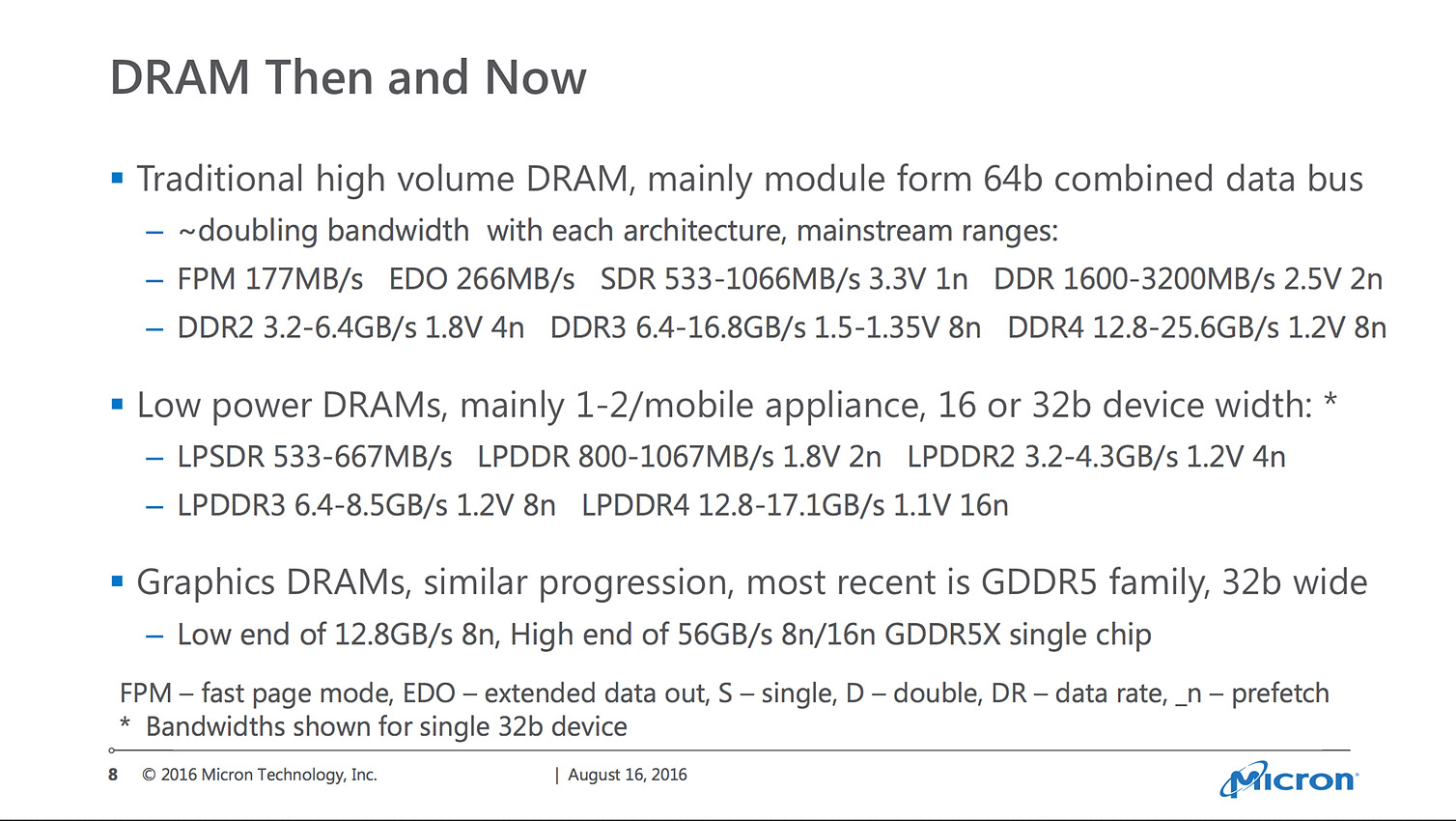

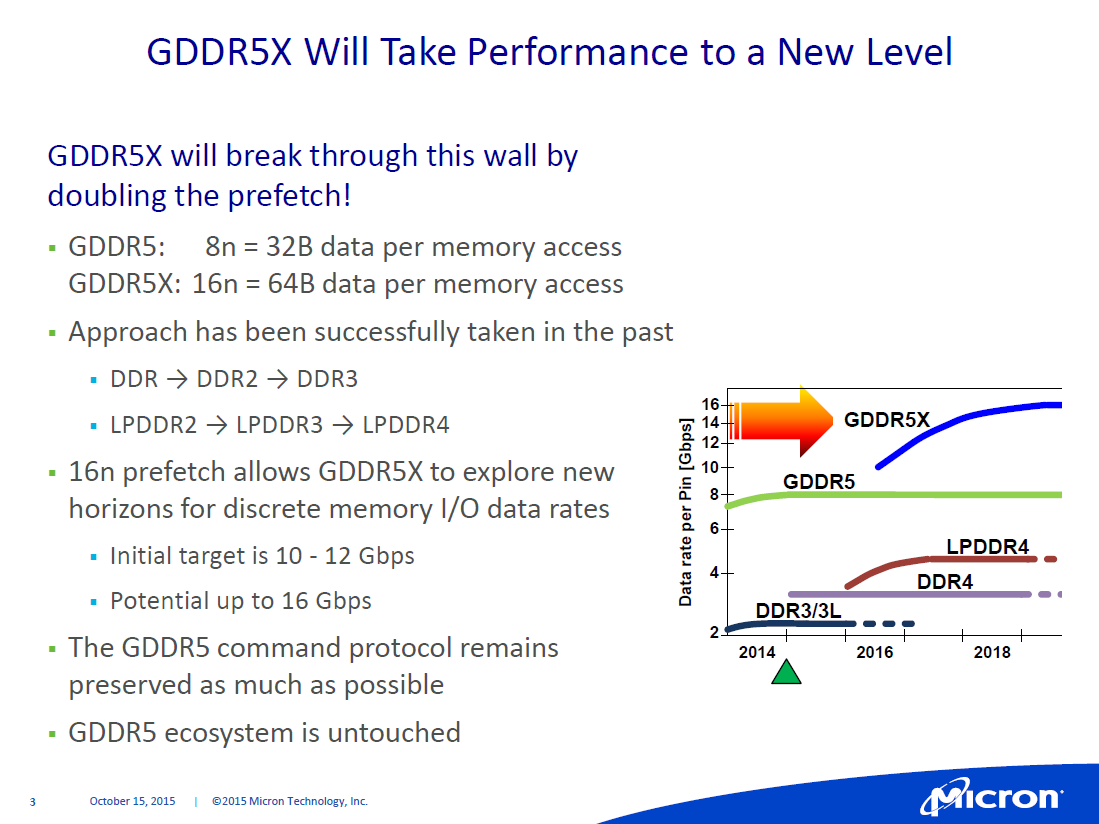

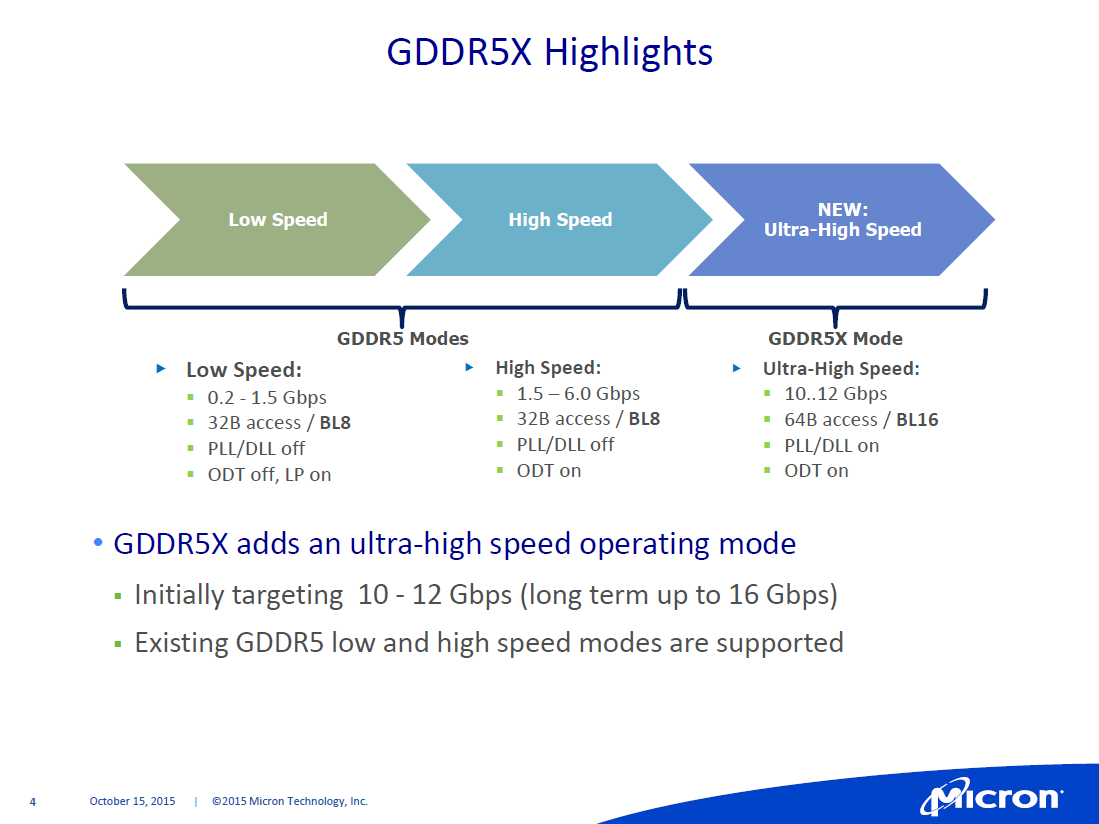

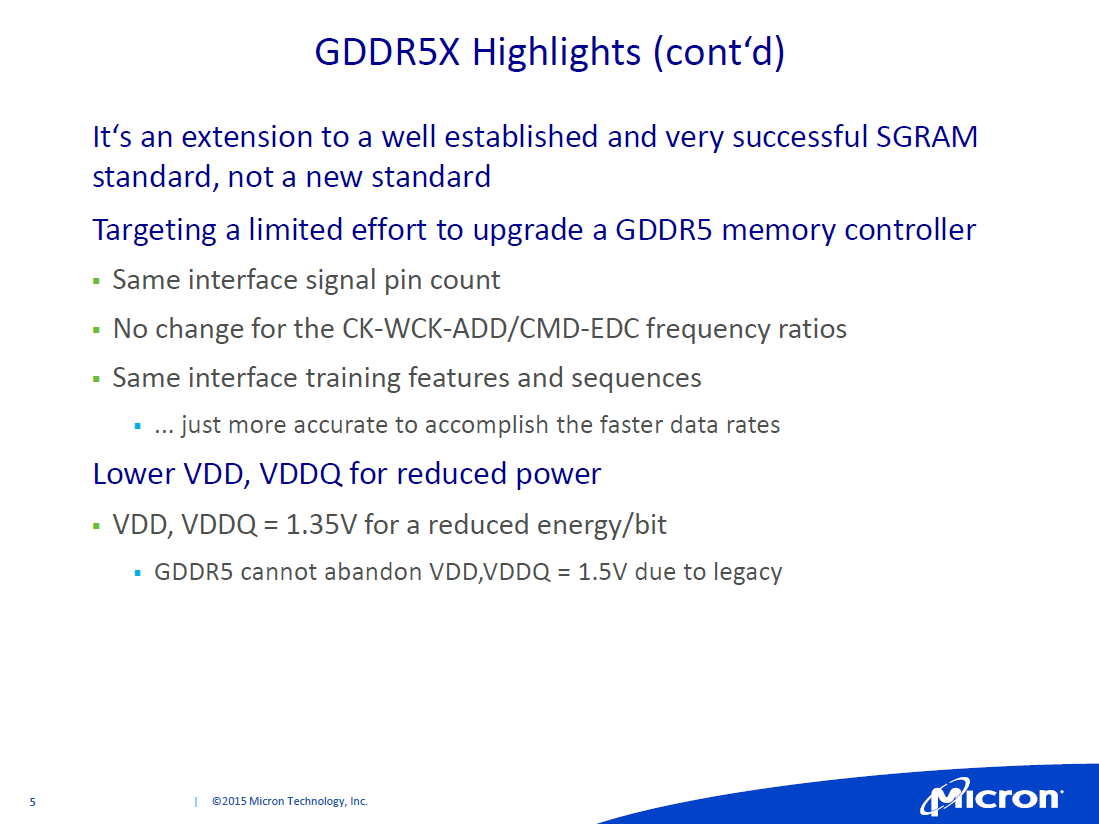

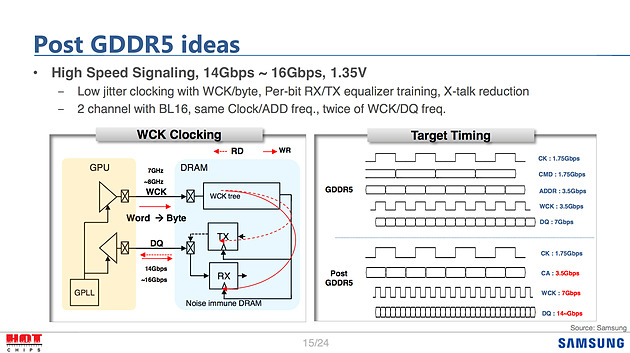

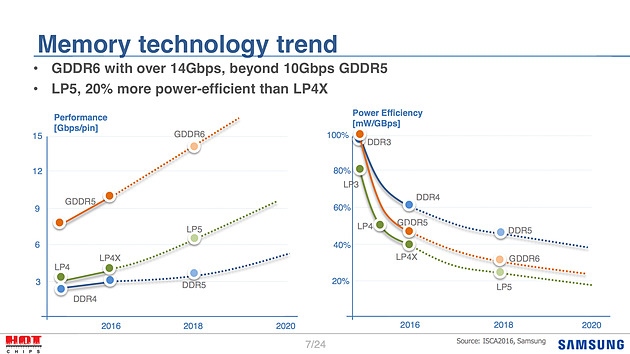

Pour la GDDR6, Samsung évoque certaines des pistes de travail envisagées. Côté objectifs la mémoire visera dans un premier temps 14 à 16 Gbps, ce qui était la cible haute pour rappel de la GDDR5X lors de sa présentation par Micron. Lors de la certification de la GDDR5X par le JEDEC, 14 Gbps est devenu le maximum visé. On notera que la GTX 1080 utilise pour rappel de la GDDR5X 10 Gbps. Techniquement, la GDDR5X abaissait la tension de la GDDR5 à 1.35V et doublait la bande passante en doublant le prefetch.

Samsung donne ici quelques idées sur la GDDR6, reprenant par exemple l'idée de la tension à 1.35V. L'élaboration de la spécification finale se fera au sein du consortium JEDEC dans les mois à venir.

Côté timing, Samsung évoque 2018, aligné avec la DDR5 et la LPDDR5, et un gain d'efficacité énergétique autour des 30%. On notera au passage que Samsung continue lui aussi de pousser son propre standard "X" avec la LPDDR4X, une variante de la mémoire mobile LPDDR4 qui fait "seulement" baisser la tension VDDQ à 0.6V pour obtenir un gain d'efficacité de 20%. Si le JEDEC n'a pas encore ratifié la LPDDR4X, on notera que SK Hynix avait annoncé en juin qu'il produirait lui aussi ce type de mémoire.

HMC, DDR5 et 3D XPoint pour Micron

Micron a également pris la parole pendant la première matinée de Hot Chips, comme nous le rapportent une fois de plus nos confrères de ComputerBase . Ces derniers qualifient d'une honnêteté rafraîchissante la présentation de Micron, ne cherchant pas forcément à annoncer des chiffres extravagants. La société aurait même regretté, si l'on en croit nos confrères, que son partenaire Intel ait annoncé beaucoup trop tôt la mémoire 3D XPoint !

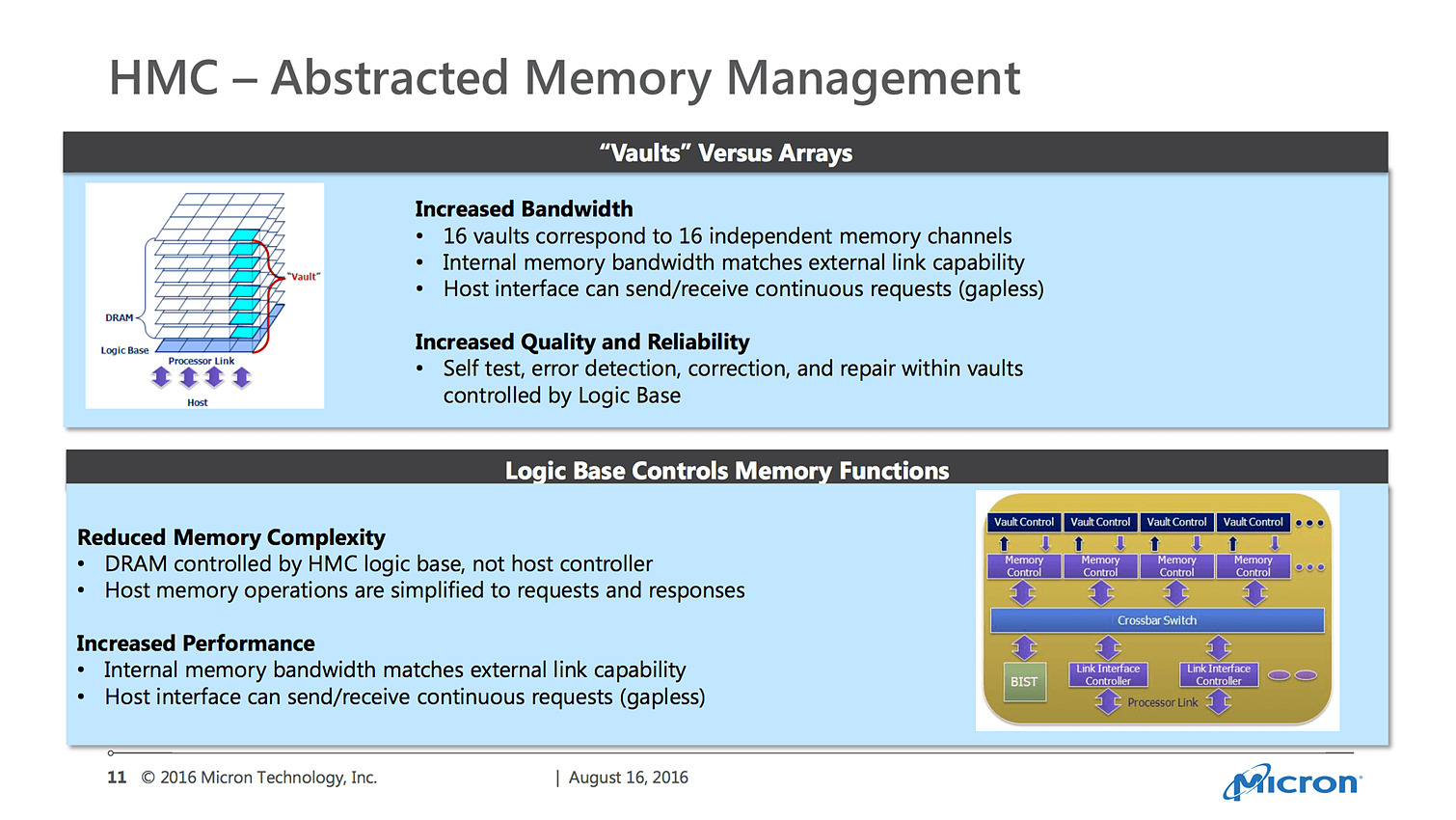

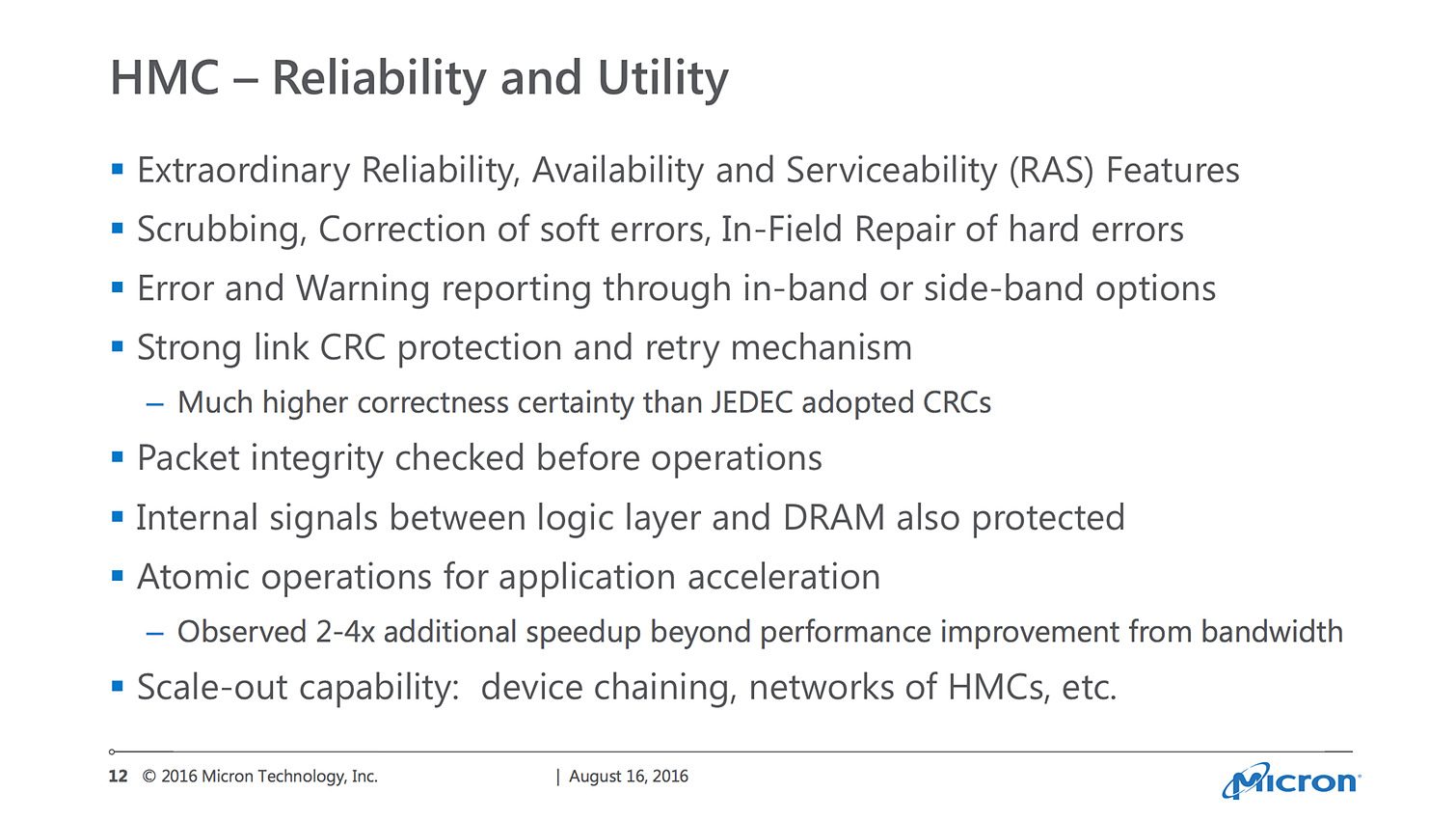

Dans le détail, Micron n'aura pas pu s'empêcher tout de même de qualifier la HBM de "mauvaise copie" de sa propre technologie Hybrid Memory Cube, plus complexe, coûteuse, et surtout assez peu disponible (elle devrait être présente sur le prochain Xeon Phi d'Intel, Knights Landing). Micron estime que la HMC dispose de nombreux avantages pour le marché du HPC, avec par exemple un meilleur algorithme de CRC que celui utilisé par le JEDEC pour la HBM.

Micron aura également évoqué la DDR5 qui aura pour objectif de doubler la bande passante par rapport à la DDR4. Micron estime produire ses premiers échantillons courant 2018, avec une production en volume possiblement en 2019, mais plus probablement pour 2020.

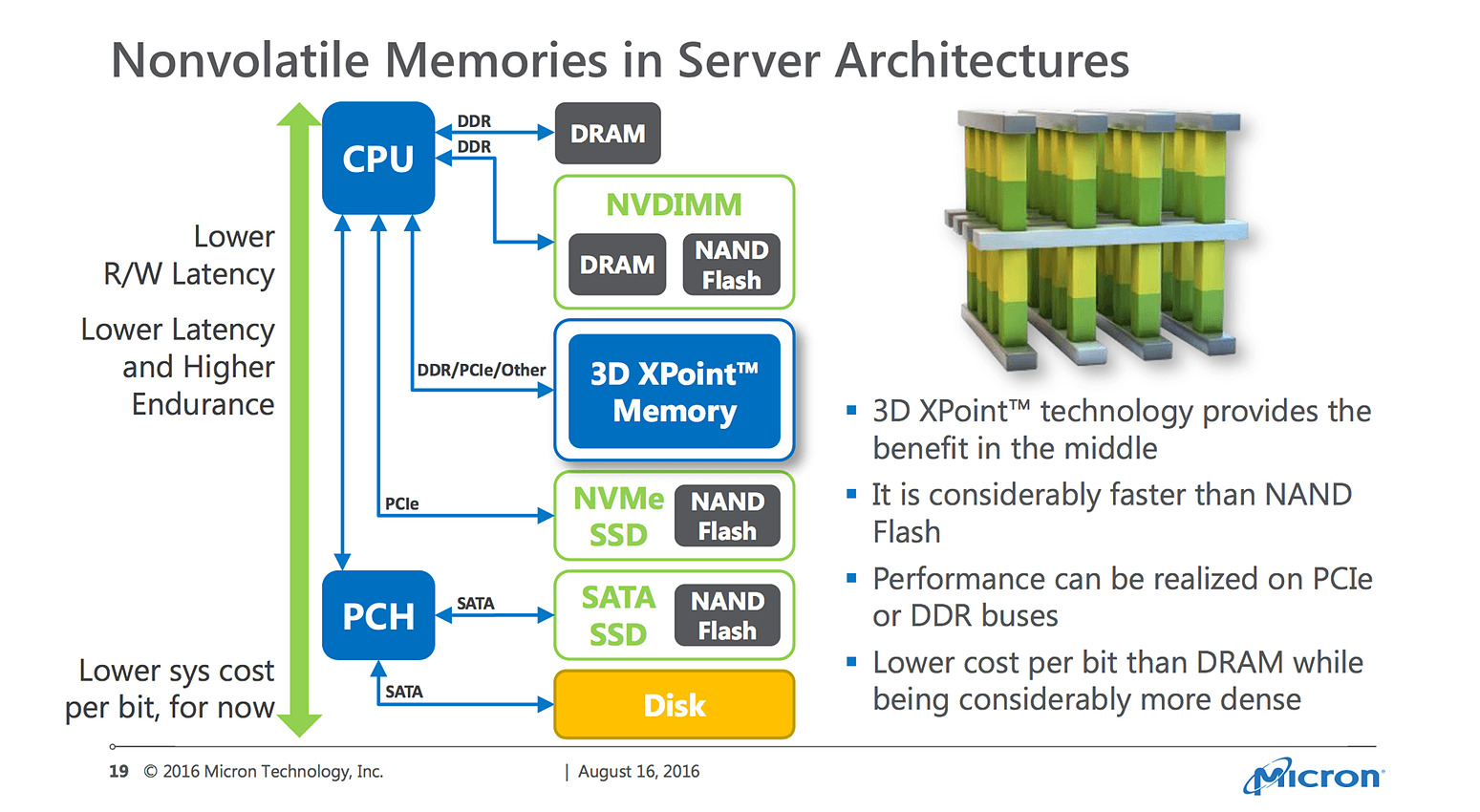

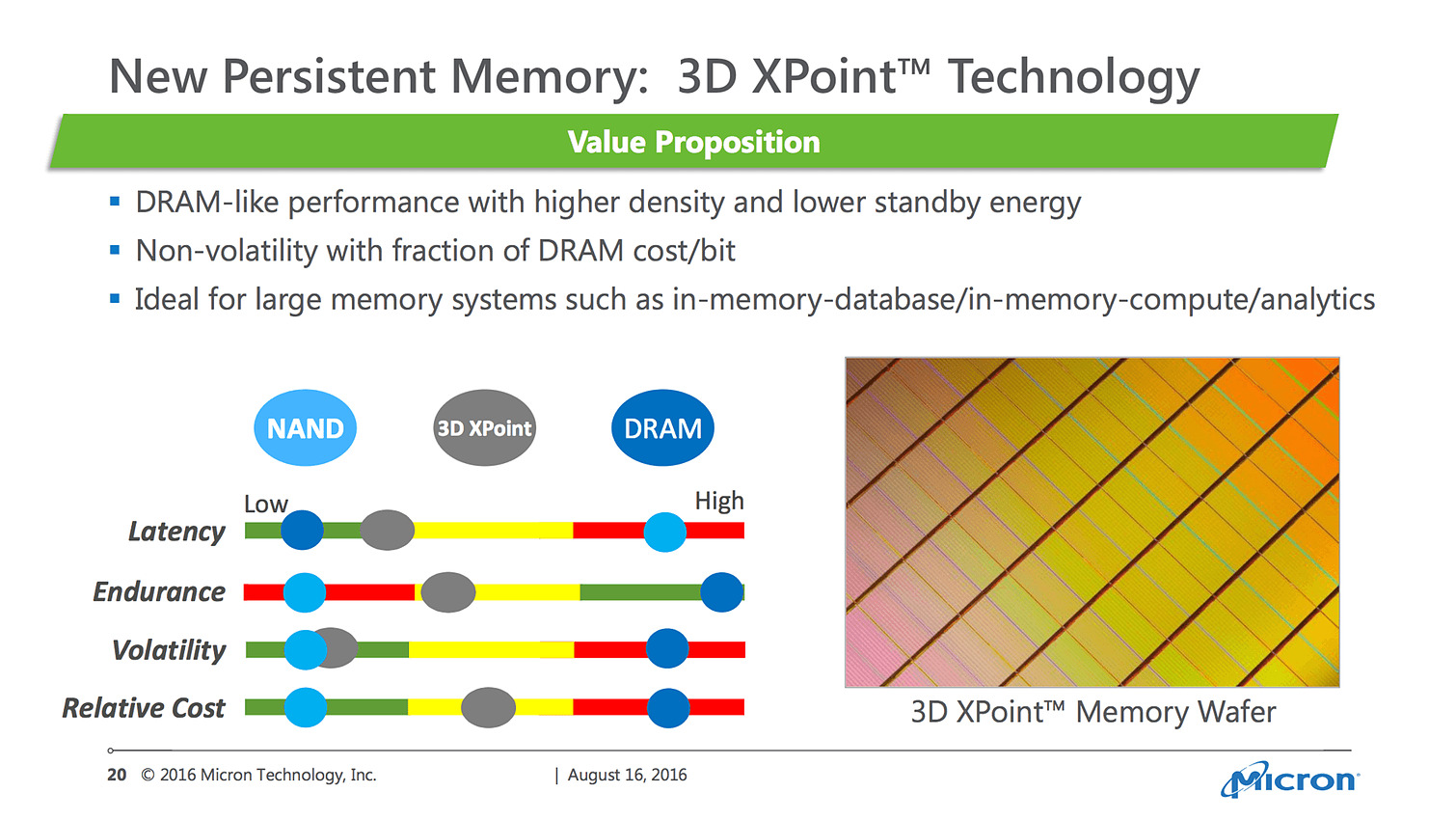

Outre le tacle envers son partenaire Intel sur la mémoire 3D XPoint, on ne retiendra pas beaucoup d'informations, si ce n'est que Micron confirme que ce nouveau type de mémoire sera en production avant la fin de l'année.

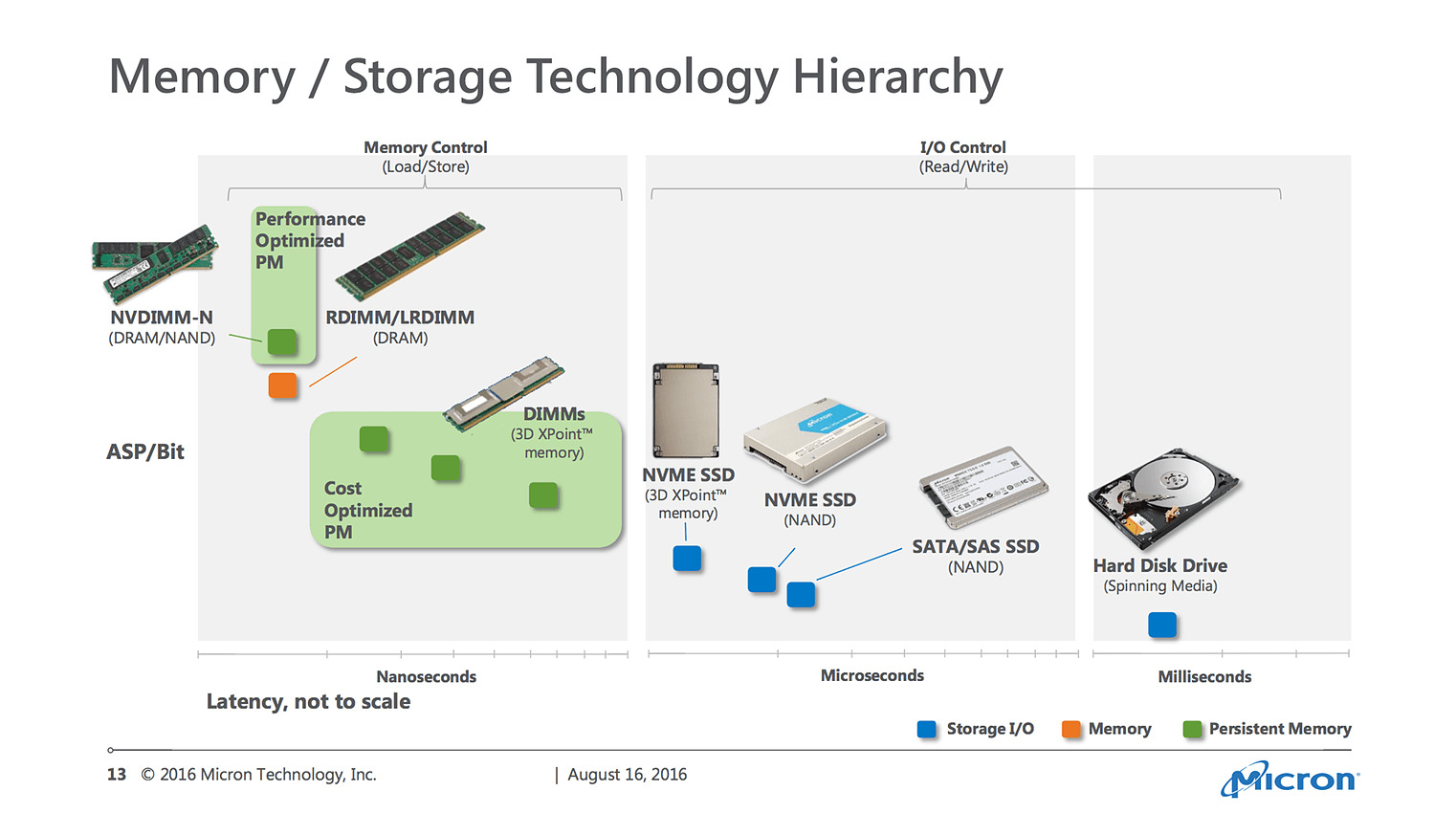

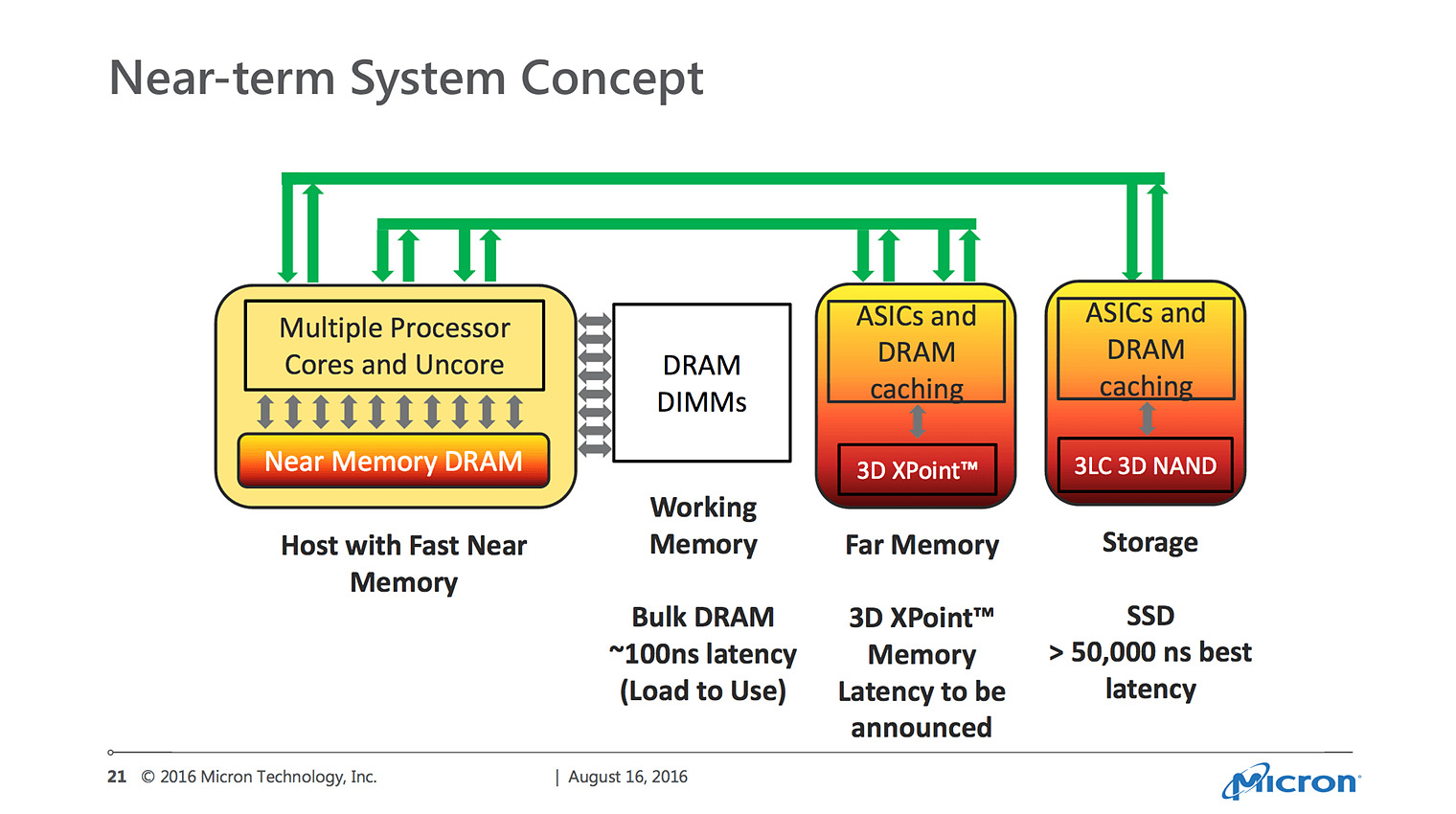

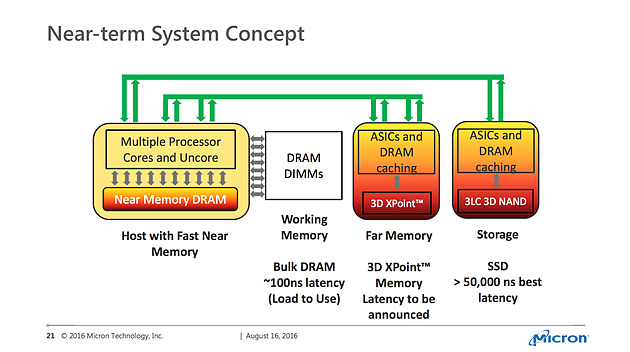

On retiendra ce dernier slide qui préfigure de ce que l'on devrait voir arriver sous peu sur les serveurs, avec deux tiers de mémoire DRAM. D'un côté une mémoire "proche", intégrée au processeur et rapide (HBM, ou plutôt HMC dans la vision de Micron) qui s'adjoint à la mémoire DRAM en barrettes plus classique. 3D XPoint et la 3D NAND proposant de leur côté deux tiers de stockages persistants.

Micron continue dans sa voie de l'originalité, dans un marché de la mémoire certes très concurrentiel. La société continue de mettre en avant sa GDDR5X, certes standardisée par le JEDEC mais qui n'a pas été adoptée par ses concurrents, mais aussi des solutions plus propriétaires comme l'Hybrid Memory Cube et 3D XPoint. Avec les ambitions de SK Hynix et de Samsung de pousser la HBM sur le terrain des PC clients, on peut cependant se demander si le pari d'ignorer la mémoire HBM ne se retournera pas contre Micron dans les mois à venir.

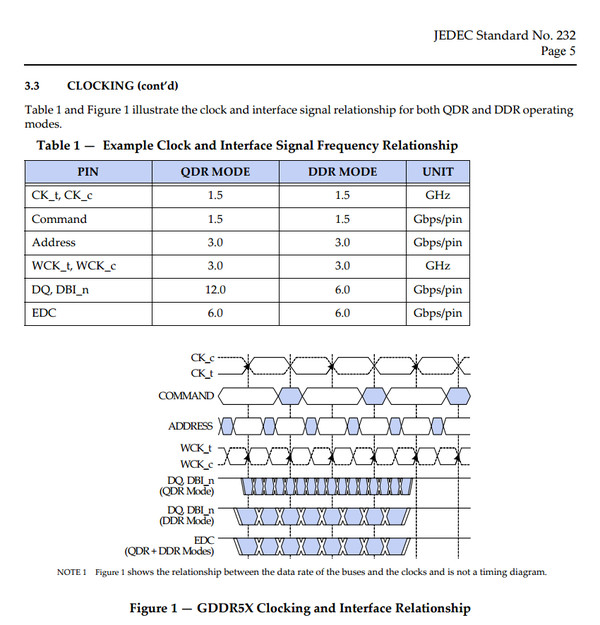

La GDDR5X standardisée par le JEDEC

Le JEDEC vient d'annoncer la publication des spécifications de la GDDR5. Le standard JESD232, daté de novembre 2015, définit la GDDR5X telle qu'elle a déjà été présentée par Micron. La GDDR5X supporte deux modes pour les données, un DDR similaire à celui de la GDDR5 fonctionnant avec un prefetch de 8n et des accès de 256 bits, et un QDR permettant de doubler à fréquence égale le débit avec en contrepartie un prefetch de 16n et des accès de 512 bits. Côté capacité le standard intègre des versions 12 et 16 Gbits là ou la GDDR5 se limitait à 8 Gb.

Le JEDEC indique que la GDDR5X cible des débits allant de 10 à 14 Gbps, soit 320 à 448 Go /s en bus 256 bits, mais Micron avait déjà évoqué la possibilité à terme d'atteindre 16 Gbps soit 512 Go /s. Ce dernier débit sera atteint avec seulement 2 puces de HBM2, une consommation moindre et probablement une meilleure bande passante effective du fait d'accès plus petits de 256 bits (voir 128 bits en mode Pseudo Channel), mais la GDDR5X devrait avoir l'avantage en terme de coût d'autant qu'elle évite de passer par un interposer.

Pour l'instant seul Micron, qui ne s'est pas positionné sur la HBM2 a contrario de SK Hynix et de Samsung, a annoncé qu'il allait produire de la GDDR5X mais rien n'empêche d'autres fabricants membre du JEDEC de se lancer.

Micron mise sur la GDDR5X

Alors que Samsung a emboité le pas de Hynix sur la HBM pour ce qui est des mémoires proposant une bande passante élevée, Micron restait de son côté uniquement positionné sur la HMC, une mémoire plus coûteuse utilisant un bus moins large mais plus véloce mais qui a l'avantage de ne pas nécessiter d'interposer. Une alternative qui n'a ne semble-t-il pas réussi à convaincre sur le marché graphique.

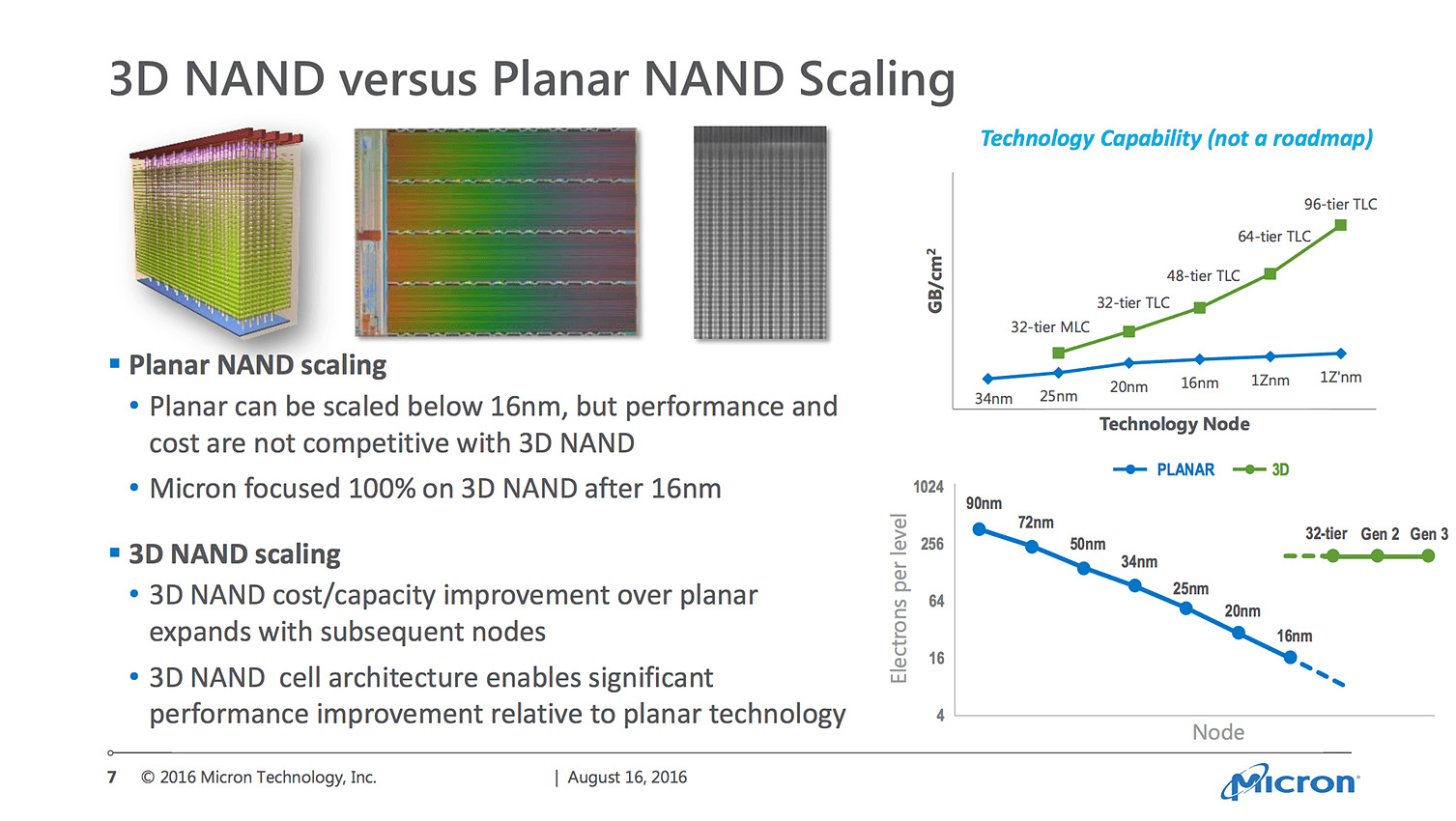

Micron se positionne du coup sur un nouveau type de mémoire dénommée GDDR5X dont le but est de doubler la bande passante par rapport à la GDDR5. Pour se faire Micron utilise la bonne vieille méthode du doublement du prefetch qui passe à 16.

La GDDR5X sera donc capable de lire 16 cellules mémoire en parallèle et de placer le tout dans un petit buffer qui déversera ses données en série et à très haute vitesse dans le bus mémoire. Cela augmente par contre la complexité de puces mémoire ainsi que la plus petite quantité de données qui peut être lue, une puce GDDR5 étant généralement 32-bit ce n'est qu'avec des accès de 512-bit par puce que les débits pourront être doublés.

Micron semble vouloir lancer la GDDR5X dès 2016, avec un débit de l'ordre de 10-12 Gbps alors que la GDDR5 atteint au mieux 8 Gbps à l'heure actuelle. D'ici 2018 Micron semble viser un doublement du débit par rapport à la GDDR pour atteindre 16 Gbps.

A terme avec un bus 256-bit on atteindrait donc les 512 Go /s, contre 1 To /s avec un bus 512-bit. Ces débits sont en fait comparable avec ceux qui seront offert par des configurations à 2 ou 4 puces utilisant les puces HBM de Samsung ou Hynix prévues pour 2016 qui seront moins gourmandes en énergie mais qui nécessiteront un interposer et pour lesquelles on peut se demander si elles pourront être produites dans les volumes nécessaires. Micron semble ouvrir une voie plus conservatrice pour l'augmentation de la bande passante pour les GPU, reste à voir si AMD ou Nvidia l'utiliseront l'an prochain.