| Mars 2007 | ||||||

|---|---|---|---|---|---|---|

| L | M | M | J | V | S | D |

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 | |

SiS: FSB 1333MHz pour Core 2 Quad

SiS vient d'annoncer avoir obtenu une licence auprès d'Intel pour produire des chispets supportant officiellement un FSB de 1333MHz avec les processeurs Core 2 Quad. Curieusement, si Intel introduira bien dès le troisième trimestre des processeurs bénéficiant d'une telle fréquence de FSB, il ne s'agit que des Core 2 Duo E6550, E6750 et E6850, or le communiqué du taiwanais ne mentionne que les versions quad cores du Core 2. Incohérence de l'annonce? Accord alambiqué avec Intel? La question reste posée. Dans l'hypothèse où SiS aurait effectivement renoncé à une licence FSB 1333MHz pour Core 2 Duo, ce ne serait de toute façon pas dramatique puisque les gains engendrés par une augmentation du FSB de 1066MHz à 1333MHz sur dual core sont plutôt réduits.

SiS vient d'annoncer avoir obtenu une licence auprès d'Intel pour produire des chispets supportant officiellement un FSB de 1333MHz avec les processeurs Core 2 Quad. Curieusement, si Intel introduira bien dès le troisième trimestre des processeurs bénéficiant d'une telle fréquence de FSB, il ne s'agit que des Core 2 Duo E6550, E6750 et E6850, or le communiqué du taiwanais ne mentionne que les versions quad cores du Core 2. Incohérence de l'annonce? Accord alambiqué avec Intel? La question reste posée. Dans l'hypothèse où SiS aurait effectivement renoncé à une licence FSB 1333MHz pour Core 2 Duo, ce ne serait de toute façon pas dramatique puisque les gains engendrés par une augmentation du FSB de 1066MHz à 1333MHz sur dual core sont plutôt réduits.

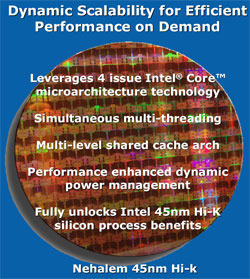

Intel parle de son Nehalem

Intel a livré quelques informations sur le Nehalem, la seconde génération de processeurs mettant à profit le couple High-K et gravure 45 nm. Nehalem est présenté comme une nouvelle micro-architecture, contrairement à Penryn qui est principalement un die-shrink, mais elle reprend tout de même les bases de larchitecture Core. Il ne fonctionnera a priori pas sur les cartes mères Socket 775 mais sur un nouveau Socket LGA1336, bien que cette information ne soit pas confirmée.

Au menu des nouveautés, le nombre de core tout dabord, puisque lon pourra atteindre les 8 (2 die de 4 core chacun), ce qui permettra dexécuter de manière simultanée 16 threads. En effet, chacun des cores pourra traiter deux threads en parallèle, un retour du SMT donc (Simultaneous Multi-Threading) avec un concept similaire à l'HyperThreading du Netburst. Tout comme l'HT des Pentium 4, le SMT du Nehalem a pour vocation d'optimiser l'utilisation des ressources du processeur, mais cette fois davantage dans le but d'augmenter le rapport performance / consommation d'énergie. Aux dires d'Intel, le gain apporté par le SMT concernera principalement les environnements serveurs.

Intel parle également dun « multi level shared cache », ce qui sous entendrait la présence dun cache L3 partagé, en sus du cache L2. La gestion de lénergie devrait être dynamique et indépendante entre les core, alors que le contrôleur mémoire sera intégré au CPU, comme chez AMD ! Intel changera au passage le bus processeur pour un nouveau bus série (que l'on connaît sous le nom CSI, pour Common System Interface) semblable dans le principe à lHyper-Transport, et qui servira entre autre à interconnecter les CPU dans un environnement multi CPU. Le nombre de ces connections sera, comme chez AMD, variable selon la gamme, tout comme le sera la taille du cache, le nombre de core ou encore le type de contrôleur mémoire (DDR3 classique ou FB-DIMM a priori), ce qui permettra à Intel de s'adapter le mieux possible à chaque marché.

Intel jette également un gros pavé dans la marre en annonçant quil sera possible en option davoir un contrôleur graphique intégré au processeur ! Bien entendu même si la présentation fait état dun « High Performance Integrated graphics » il est très probable que le niveau soit celui du bas de gamme Intel qualifiait bien ses IGP de « Extreme Graphics » jusqu'à il y a peu ! Voilà donc la réponse dIntel à linitiative Fusion dATI et AMD qui vise à regrouper GPU et CPU au sein dun même die, et à terme cette annonce laisse penser que le marché de lIGP à des jours difficiles devant lui.

Intel indique que la production devrait débuter en 2008, pour une production en volume en 2009. Il sera alors temps de river nos yeux sur le Westmere, die-shrink 32nm, puis sur la nouvelle architecture qui porte le nom de Gesher. Pour finir, nous devons ajouter que même si il est toujours agréable de voir un constructeur qui communique avec autant davance sur les fonctionnalités de ses futurs produits, il ne faut pas être dupe : cette opération sert à occuper le terrain alors que tout le monde sattend plutôt à des nouvelles dAMD et de ses Athlon 64 X4.

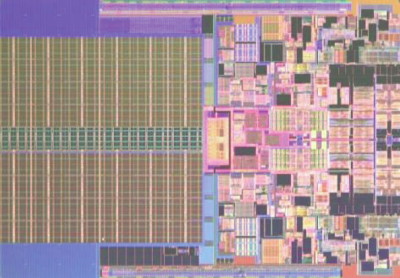

Intel donne des détails sur le Penryn

Intel sest décidé ce jour à donner quelques détails supplémentaires concernant les prochaines évolutions de sa gamme processeur, à commencer par le Penryn. On connaissait déjà de manière officielle quelques détails (cf. ici ou encore là)sur ce qui est avant tout présenté comme un « die-shrink » des processeurs actuels : une gravure en 45nm avec technologie high-k, et un nombre de transistor passant de 290 à 410 millions du fait du passage de 4 à 6 Mo de cache L2.

Le core Penryn et ses 6 Mo de cache L2

Première chose, Intel confirme être dans les temps pour commencer la production durant le second semestre, même si cela ne signifie pas pour autant que toute la gamme sera disponible cette année. Les fréquences sont annoncées comme supérieures à 3 GHz, ce qui en soit nest pas une surprise. Pour rappel, il faudra sur desktop au moins de nouvelles plates-formes, à base du chipset P35 qui sera lancé en juin ou du X38 qui arrivera à la rentrée.

Côté consommation, Intel a choisi de ne pas abaisser le TDP au profit dune augmentation de performances : du coup, on restera à 65 watts sur les dual core Wolfdale, et 95 à 130 watts sur les quad core Yorkfield (contre 105 à 130 actuellement). Le FSB ne devrait pour sa part pas augmenter sur desktop, soit 1333 pour le dual core et 1066 pour le quad core, mais il atteindra 1600 sur serveur.

Quid des améliorations architecturales ?

1/ Des divisions plus rapidesIntel n'a pas jugé utile de toucher aux unités de calcul déjà très performantes de l'architecture Core, exception faite de l'unité responsable de la division. La division reste une des opérations arithmétiques effectuée le plus lentement par un processeur, et il est intéressant de noter à ce sujet qu'Intel et AMD utilisent des techniques radicalement différentes. Les processeurs Intel utilisent, tout comme nous, la méthode euclidienne : à un diviseur et un dividende sont associés un quotient et un reste. Les processeurs opèrent la division par morceau, c'est-à-dire qu'à chaque cycle ne sont traités qu'un nombre fini de bits. L'opération est relativement lente (le nombre de cycles nécessaire dépend de la taille du dividende), mais est exacte.

Les processeurs AMD utilisent quant à eux une méthode d'approximation basée sur des tables et des multiplications. L'opération est beaucoup plus rapide, mais les tables micro-codées sont consommatrices de ressources. Les processeurs AMD n'emploient ainsi la technique que pour les divisions flottantes, et les divisions entières passent par une phase préalable de conversion de type (ce qui réduit notablement leur efficacité). L'opération est rapide (tout du moins en flottants), mais approximée. AMD semble cependant décider à abandonner cette méthode sur le K10 pour adopter la méthode euclidienne.

Intel a-t-il eu peur que le dernier né d'AMD soit plus performant sur les divisions ? Quoiqu'il en soit, là où Core traite deux bits par cycle (on parle de Radix-4), Penryn en traite quatre (Radix-16). La technique bénéficie également à d'autres opérations plus complexes faisant intervenir des divisions, telles que le calcul de la racine carrée qui a fait l'objet d'optimisations toutes particulières. Signalons que les moteurs 3D géométriques font une utilisation assez intensive de ce type d'opération.

2 / Super Shuffle et SSE4Le SSE se voit améliorer en deux points, le premier étant laccélération des instructions de shuffle, cest-à-dire les instructions qui mélangent les données de plusieurs registres SSE et qui sont grandement utilisées dans le codage et le décodage vidéos.

De plus, une nouvelle série dinstructions fait pour rappel son apparition, le SSE4 dont vous pouvez lire les détails dans ce document . Une cinquantaine dinstructions sont au menu du jour, dont une bonne partie pourrait apporter des gains très généraux, et dautres dans des domaines plus spécifiques tels que le calcul dune valeur CRC. Bien entendu il faudra que les programmes soient écrits ou compilés pour prendre en compte ces instructions, elles napporteront rien aux programmes actuels.

3/ Energie : IDA (Intel Dynamic Acceleration) et Deep Power DownLa technique d'accélération dynamique IDA n'est pas réellement propre au Penryn, car déjà implémentée sur les futurs modèles de Core 2 Duo Merom sur la plate-forme mobile Santa Rosa qui est prévue pour mai. Elle est à ce titre présentée comme relative à la gestion de l'énergie, bien que son utilisation nous semble intéressante au delà de cette seule perspective.

L'idée d'IDA consiste à booster la performance d'un des deux cores lorsque l'autre est inactif. Par exemple, sur un processeur double coeur cadencé à 2,2 GHz, l'inactivité d'un core se traduit par une accélération du second à 2,4 GHz. L'enveloppe thermique globale reste inférieure à ce qu'elle serait si les deux cores tournaient à 2,2 GHz, tout en assurant une performance supérieure du thread traité par le core actif. Par cette astuce, les applications mono-thread sont accélérées, tout en conservant une dissipation thermique globale dans des limites raisonnables. Il est fort dommage que cette technique ne soit implémentée que sur les plateformes mobiles, même si bien entendu dans le cadre dune machine overclockée il faudrait pouvoir la désactiver !

Notons pour finir que la version Mobile du Penryn bénéficie en outre d'un état supplémentaire appelé Deep Power Down, destiné à prolonger encore un peu l'autonomie des batteries des laptops. Dans ce mode, les caches L1 & L2 seront purement et simplement coupés, ce qui nétait pas le cas auparavant.

Et les performances ?Vous devrez vous contenter des chiffres avancés par Intel.

En environnement ludique, les améliorations micro-architecturales, l'inflation de la taille du L2, et les fréquences supérieures de Penryn se traduisent, selon Intel, par un gain de performance de l'ordre de 20% entre un Penryn 3.2 GHz et un Conroe 3.0 GHz. Les optimisations apportées aux instructions Shuffle et le SSE4 permettrait, par rapport au SSE3, datteindre un chiffre de lordre de 40% en encodage vidéo. Wait & See !