Intel dévoile l'AVX-512

Publié le 24/07/2013 à 18:45 par Guillaume Louel

C'est par le biais d'un de ses blogs qu'Intel vient d'annoncer la prochaine version d'AVX, que l'on connaissait précédemment sous le nom de code 3.1 et 3.2. Il s'agira finalement d'AVX-512.

Comme son nom l'indique, AVX-512 est une extension du jeu d'instruction AVX qui rajoute des instructions SIMD (une instruction qui s'applique à de multiples données) 512 bits, soit le double de l'AVX actuel, pouvant cibler aussi bien des données entières que flottantes. Ce n'est pas la première fois que l'on voit un jeu d'instructions 512 bits chez Intel car c'est précisément ce que proposait le jeu d'instruction de Larrabee, et plus récemment de Knights Corner que l'on connait sous la dénomination commerciale Xeon Phi.

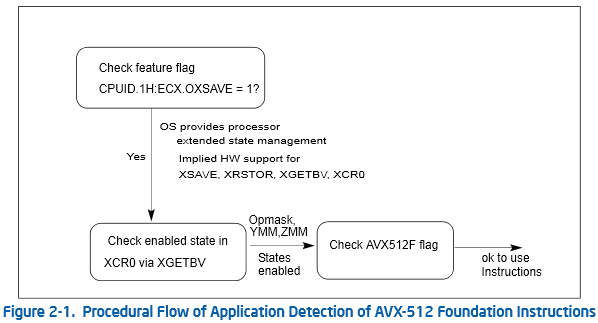

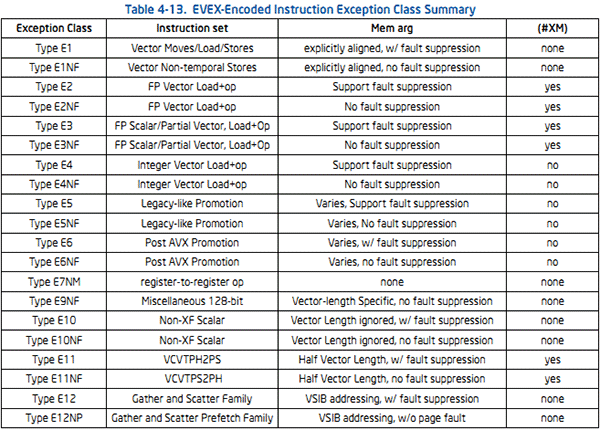

AVX-512 apporte une série de changements détaillés dans ce document PDF, on notera en premier lieu le nombre de registres qui passe de 16 à 32, tandis que les nouvelles instructions sont préfixées EVEX (au lieu de VEX pour AVX2). Ces dernières concernent aussi bien les entiers que les flottants et vous pourrez retrouver ci-dessous les grandes familles (classes) d'instructions disponibles.

La liste des classes d'instructions d'AVX-512. Vous retrouverez dans le PDF la liste complète des instructions à la page 75.

Notez qu'Intel parle dans son document "d'AVX-512 Foundation", sous entendant qu'il s'agit là du socle commun et que certains produits pourraient proposer des instructions supplémentaires. Ce n'est pas forcément surprenant puisque ces slides indiquaient que Knights Landing (la prochaine version de Xeon Phi) utiliserait AVX3.1, tandis que Skylake (la prochaine nouvelle architecture CPU d'Intel qui apparaitra après Broadwell en 14nm) utilisera AVX 3.2.

Il sera intéressant de voir ce qu'Intel fera exactement de ces unités AVX 512 bits dans le processeur Skylake. Le directeur du Visual and Parrallel Architecture Group d'Intel, Ofri Wechsler est en effet à la fois en charge des projets Xeon Phi du constructeur (l'actuel Knights Corner, le suivant Knights Landing, et le futur Knights Hill) mais aussi de l'architecture graphique qui sera utilisée dans Skylake.

Sa biographie sur le site d'Intel indique également qu'il était responsable du projet qui tentait de construire un pipeline de rendering 3D logiciel fonctionnant sur Larabee, l'ancêtre des actuels Xeon Phi. Si des rumeurs laissaient penser qu'Intel pourrait un jour utiliser ce type de solution pour remplacer un GPU, l'échéance de Skylake est probablement encore trop proche pour que l'on voit arriver ce type de solution pour remplacer l'iGPU intégré aux processeurs. Skylake dans sa version desktop est en effet prévu pour 2015.

Vos réactions

Contenus relatifs

- [+] 27/04: Xeon Platinum pour accompagner les ...

- [+] 22/08: HMC, DDR5 et 3D XPoint pour Micron

- [+] 17/11: 76 coeurs sur le die de Knights Lan...

- [+] 24/06: Micron en charge de la mémoire des ...

- [+] 26/11: Des détails sur les (monstrueux) Xe...

- [+] 24/07: Intel dévoile l'AVX-512

- [+] 04/07: AVX3 et PCI Express 4.0 chez Intel

- [+] 26/03: GTC: Les Tesla K20X dans le Piz Dai...

- [+] 12/11: Intel lance les Xeon Phi 5110P

- [+] 08/11: Cray XC30 avec processeurs Intel