Actualités mémoires

SK Hynix et Samsung parlent de HBM

AMD dans le vert, Zen en 2017 ?

La HBM2 Hynix dispo ce troisième trimestre

Computex: NVDIMM Micron: 8 Go de DDR4 + 16 Go de SLC

Computex: GeIL EVO X: DDR4 double PCB et LED RGB

Les prix de la DRAM remontent fortement

Après une longue chute, qui avait vu entre autre la DDR4 et la DDR3 arriver à parité côté prix, la situation du marché de la DRAM a commencé à se stabiliser au début de l'été.

Alors qu'en février le prix "contractuel" pour la fabrication d'un module de SO-DIMM de 4 Go frôlait les 15 dollars, il était descendu fin juin à 12.50. Une légère remontée avait été amorcée au courant de l'été, ce même prix contractuel atteignant fin août 13.50.

A compter de la mi-septembre, les prix sont repartis significativement à la hausse, une hausse qui a continué tout le mois d'octobre. Au point que le site DRAMexchange qui publie régulièrement les prix contractuels ne les a pas publiés fin septembre.

On peut cependant se reporter sur le prix des puces de mémoires 512 Mo (il en faut huit pour faire une barrette 4 Go, le prix contractuel couvrant également le coût du PCB et de l'assemblage). Autour de 1.804$ fin février, le prix des puces était descendu sous les 1.50 en juin. Aujourd'hui, au moment ou nous écrivons ces lignes, le prix moyen des puces est de 2.533$ pour la DDR4 (2.480$ pour la DDR3), soit une hausse de près de 69% en quatre mois !

Pour justifier cette hausse, on retrouve plusieurs facteurs. La demande saisonnière est évoquée par SK Hynix qui a publié aujourd'hui ses résultats financiers , indiquant que les OEM ont reconstitué leurs stocks avec une hausse des livraisons sur le trimestre de 8%. La forte demande de mémoire sur les smartphones joue également de manière indirecte, plusieurs acteurs préférant produire de la mémoire mobile (par exemple LPDDR4), plus rentable.

16 et 32 Go pour les premiers Intel Optane ?

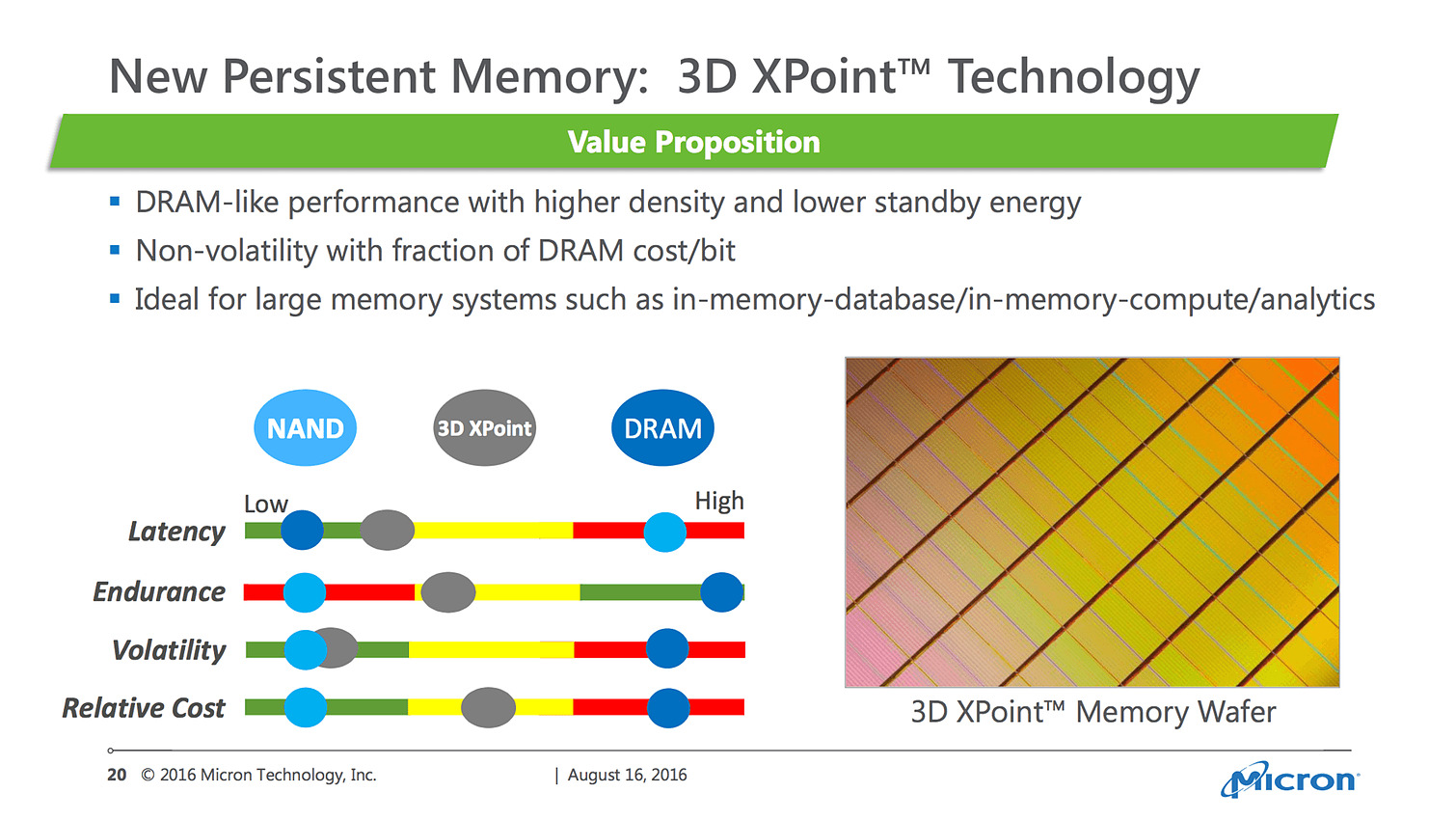

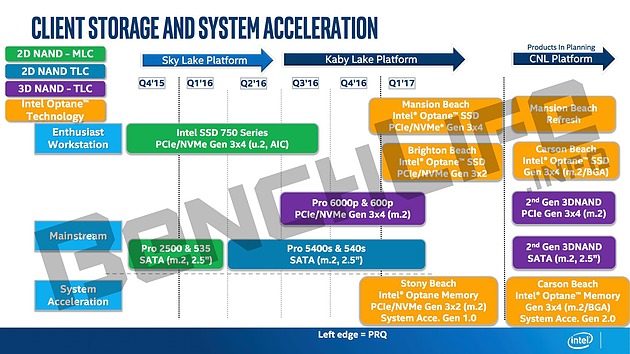

Nos confrères de Benchlife ont publié une actualité concernant l'arrivée de ce qui serait le premier produit Intel Optane grand public. Pour rappel, Optane est le nom commercial donné à la mémoire PRAM 3D Xpoint d'Intel, une mémoire non volatile à mi chemin entre la RAM et la NAND.

En juin dernier, ces mêmes confrères avaient publié un extrait de la roadmap d'Intel ou l'on pouvait voir les trois produits Optane qui seraient proposés. Le premier devant arriver sur le marché utilisant le nom de code Stony Beach. Il est décrit comme un "accélérateur système".

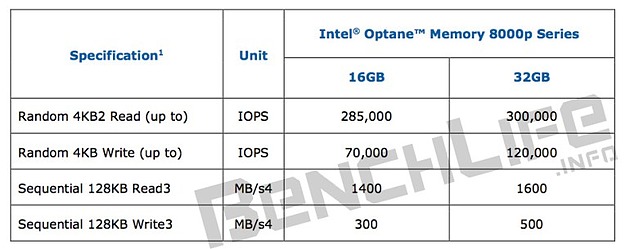

C'est sur ce dernier que nos confrères ont publié de nouvelles informations, ce Stony Beach prendra le nom d'Intel Optane 8000p. On les retrouvera au format M.2 dans des déclinaisons 2241 et 2280 (4.1 et 8cm de long).

Deux capacités sont annoncées, et c'est la première surprise : seulement 16 et 32 Go. Des chiffres particulièrement contenus, sachant qu'un des avantages mis en avant pour la technologie est sa densité 10x supérieure à celle de la mémoire DRAM traditionnelle.

L'autre surprise concerne les performances annoncées. Côté débits là aussi les chiffres annoncés pour ces accélérateurs ne sont pas révolutionnaires :

Les chiffres d'IOPS bruts sont même en dessous de ceux annoncés par les tous derniers SSD en M.2 comme le 960 Pro de Samsung par exemple.

La différence devrait se faire sur la latence, plus faible, mais on peut se demander comment ce tiers de mémoire supplémentaire s'intercalera dans les systèmes d'exploitations. L'hypothèse la plus probable est que ces modules seront vus comme des disques de stockage qui fonctionneront sous Windows via la technologie ReadyBoost (qui peut utiliser un périphérique USB comme cache disque). Un scénario d'utilisation qui ne profiterait pas forcément énormément de l'avantage de latence, surtout sur un système qui disposerait déjà d'un SSD. On se souviendra il y a quelques jours de l'annonce du consortium Gen-Z pour tenter de répondre, entre autre, à cette problématique.

On attendra de voir comment Intel mettra en avant ces produits, et s'il s'accompagnera d'une annonce d'un mode de support alternatif sous Windows. La question du prix sera également d'importance. Leur lancement est attendu avant la fin de l'année avec un support exclusif (on imagine pour des raisons marketing) de la plateforme Kaby Lake.

Alliance autour d'un nouveau bus mémoire

Plusieurs acteurs majeurs de l'industrie viennent d'annoncer une alliance dans le but de développer une nouvelle interface mémoire. Ils se sont regroupés au sein d'un consortium baptisé Gen-Z.

La page de description du consortium insiste sur un mode de fonctionnement transparent et ouvert. Le consortium en lui même est une organisation à but non lucratif (pour les puristes, une entreprise américaine de type "not for profit"). Le mode de développement sera transparent, et le standard final sera publié, disponible et utilisable gratuitement.

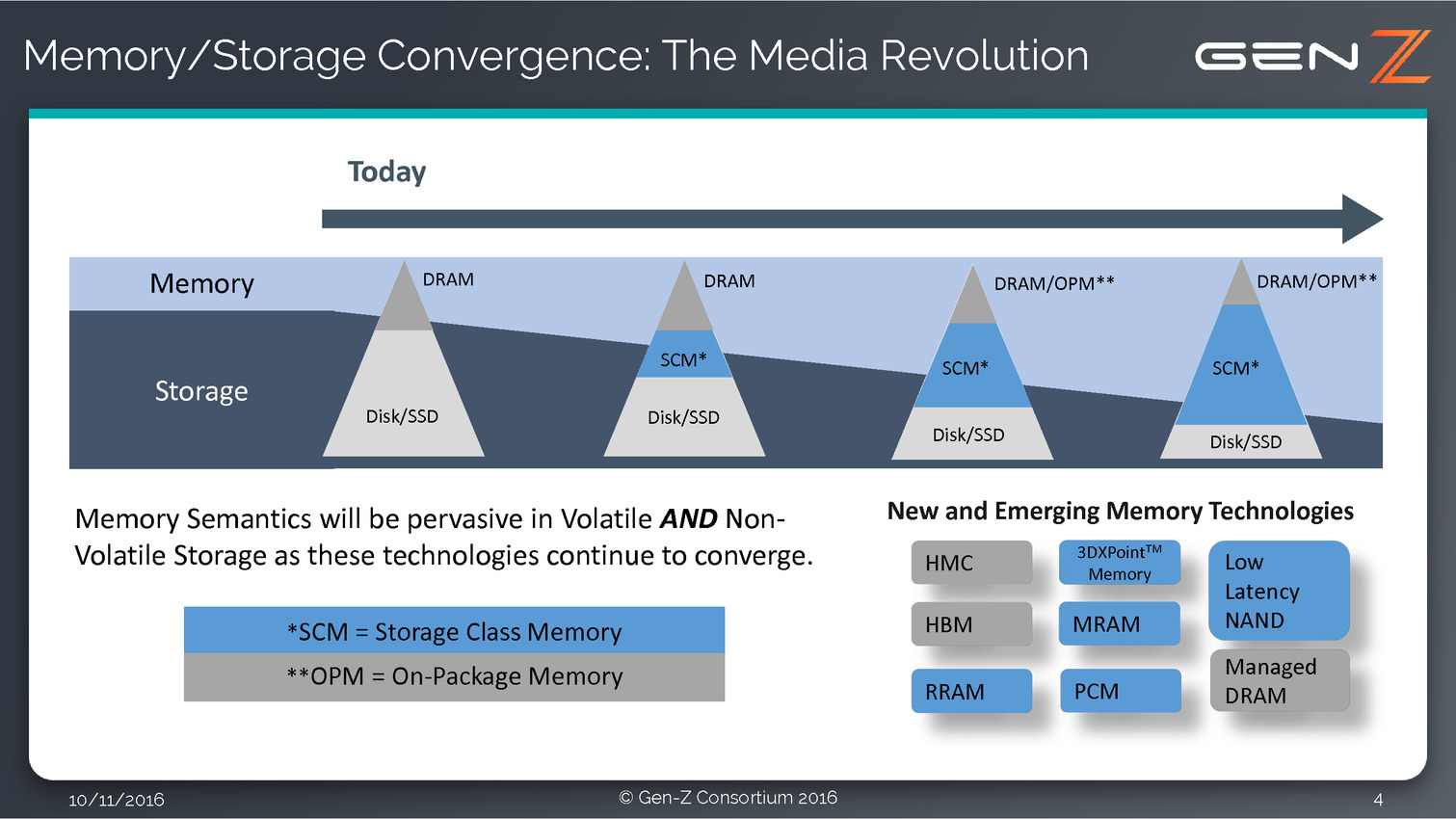

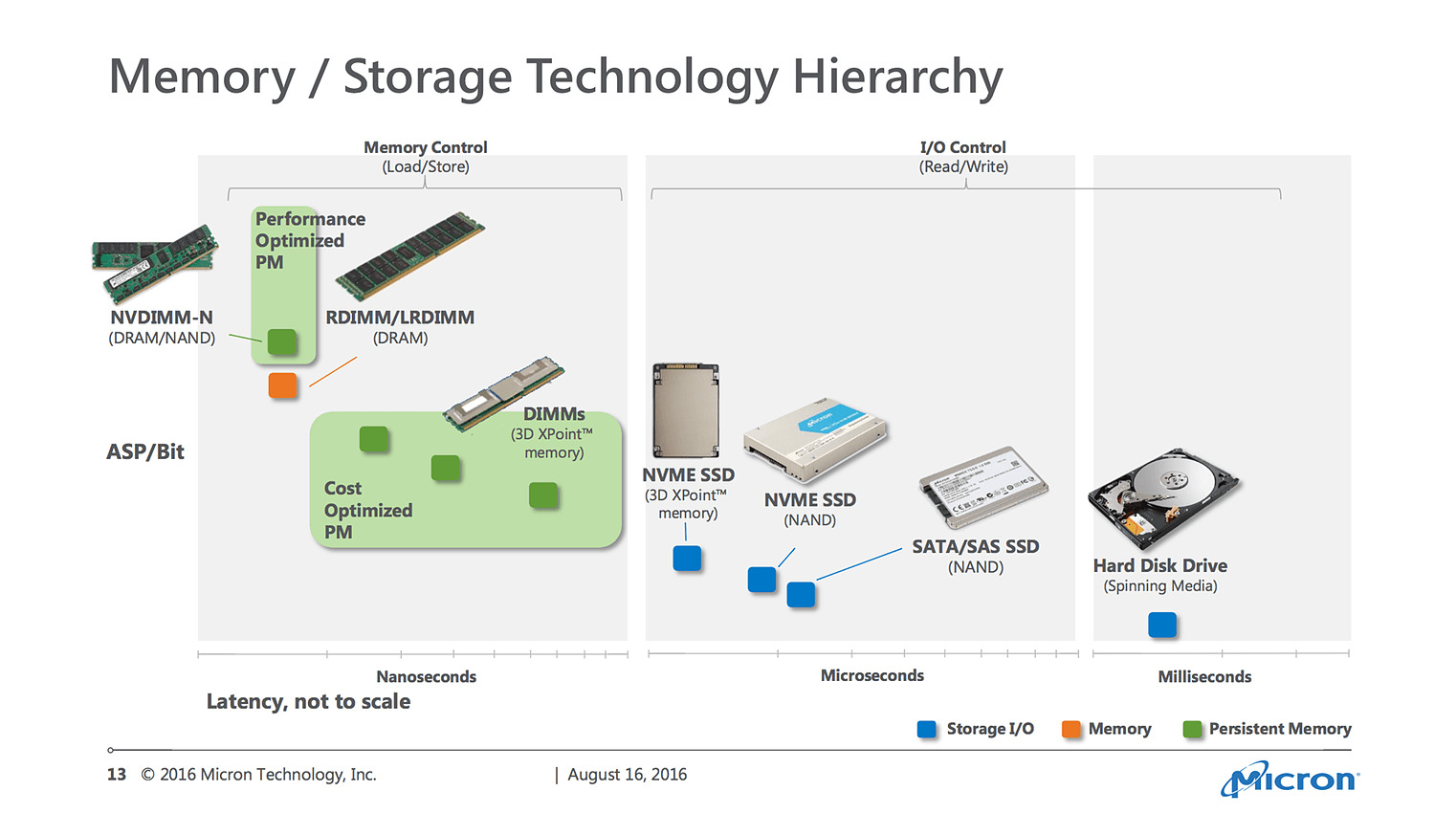

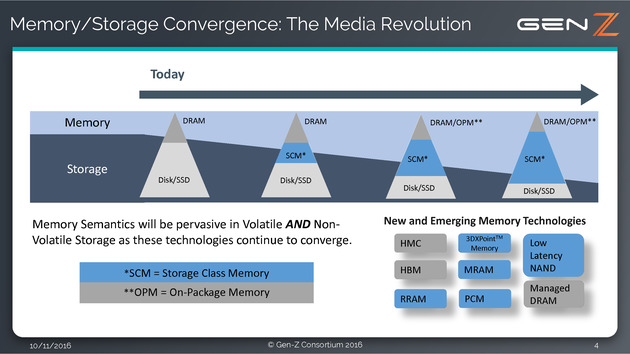

Techniquement il s'agit de proposer une nouvelle manière d'interconnecter la mémoire, ou plutôt les multiples types de mémoires qui pourront coexister à l'avenir.

Le consortium prend l'exemple des nouveaux "types" de mémoires, appelés SCM (Storage Class Memory) comme peuvent l'être les RRAM, MRAM, ou les implémentations commerciales annoncées comme 3D XPoint chez Intel/Micron ou la Z-NAND de Samsung. Ces nouveaux types de mémoires viennent s'ajouter à la mémoire traditionnelle (DRAM) qui voit aussi arriver de nouvelles variantes (HBM ou HMC).

L'idée de base du consortium est de proposer une interface avec des commandes très simples, proches de celles utilisées pour la DRAM, mais qui puissent être utilisées aussi bien au sein d'un package, sur la carte mère, ou au delà (communication entre serveurs dans un data center). Le tout se doit de rester compatible avec l'existant, y compris les systèmes d'exploitations qui pourront exploiter ces nouvelles mémoires de manière transparente. Un but assez noble tant la question de comment adresser ce nouveau tiers de mémoire avait été évitée jusqu'ici.

Le consortium annonce qu'il utilisera entre autre le protocole IEEE 802.3 (Ethernet) comme protocole de communication interne (on pourra aussi utiliser Ethernet pour la couche physique de transport). En plus des protocoles, un nouveau connecteur devrait être annoncé pour tenter de standardiser ces futurs types de mémoire, il supportera jusque 112 GT/s.

Les objectifs fixés sont particulièrement audacieux, et on ne pourra que se féliciter de voir tant d'acteurs majeurs de l'industrie s'associer pour tenter de proposer un nouveau standard :

L'absent le plus notable est Intel, et il est difficile de ne pas voir cette alliance comme formée contre la firme de Santa Clara qui a tendance à développer ses bus de manière propriétaires, particulièrement pour tout ce qui touche au monde serveur.

Il est tout de même intéressant de voir que Micron, partenaire d'Intel sur 3D Xpoint est présent dans le consortium (3D Xpoint est même mentionné dans les slides de présentation). Il sera intéressant de suivre l'évolution de ce standard qui pourrait apporter des solutions concrètes aux problématiques d'interconnexions.

Vous pouvez retrouver la présentation du consortium ci dessous :

Samsung évoque la GDDR6

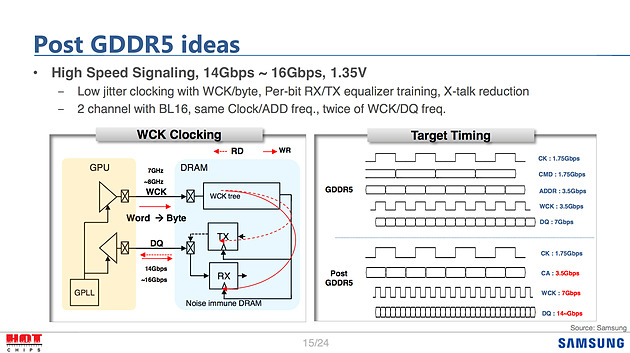

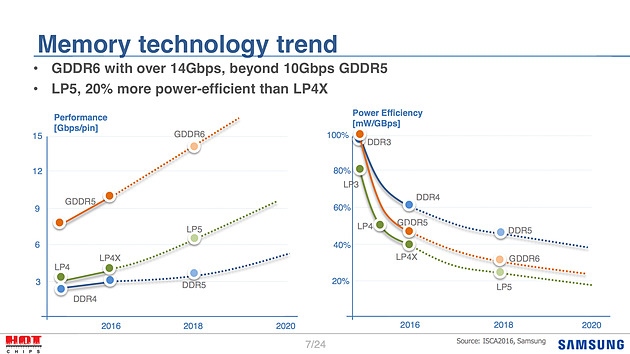

En parallèle à la mémoire HBM, Samsung à évoqué le futur de la GDDR5, ignorant quelque peu l'existence de la GDDR5X de Micron qui, bien que standardisée par le JEDEC, n'a pas été adoptée par ses concurrents.

Pour la GDDR6, Samsung évoque certaines des pistes de travail envisagées. Côté objectifs la mémoire visera dans un premier temps 14 à 16 Gbps, ce qui était la cible haute pour rappel de la GDDR5X lors de sa présentation par Micron. Lors de la certification de la GDDR5X par le JEDEC, 14 Gbps est devenu le maximum visé. On notera que la GTX 1080 utilise pour rappel de la GDDR5X 10 Gbps. Techniquement, la GDDR5X abaissait la tension de la GDDR5 à 1.35V et doublait la bande passante en doublant le prefetch.

Samsung donne ici quelques idées sur la GDDR6, reprenant par exemple l'idée de la tension à 1.35V. L'élaboration de la spécification finale se fera au sein du consortium JEDEC dans les mois à venir.

Côté timing, Samsung évoque 2018, aligné avec la DDR5 et la LPDDR5, et un gain d'efficacité énergétique autour des 30%. On notera au passage que Samsung continue lui aussi de pousser son propre standard "X" avec la LPDDR4X, une variante de la mémoire mobile LPDDR4 qui fait "seulement" baisser la tension VDDQ à 0.6V pour obtenir un gain d'efficacité de 20%. Si le JEDEC n'a pas encore ratifié la LPDDR4X, on notera que SK Hynix avait annoncé en juin qu'il produirait lui aussi ce type de mémoire.

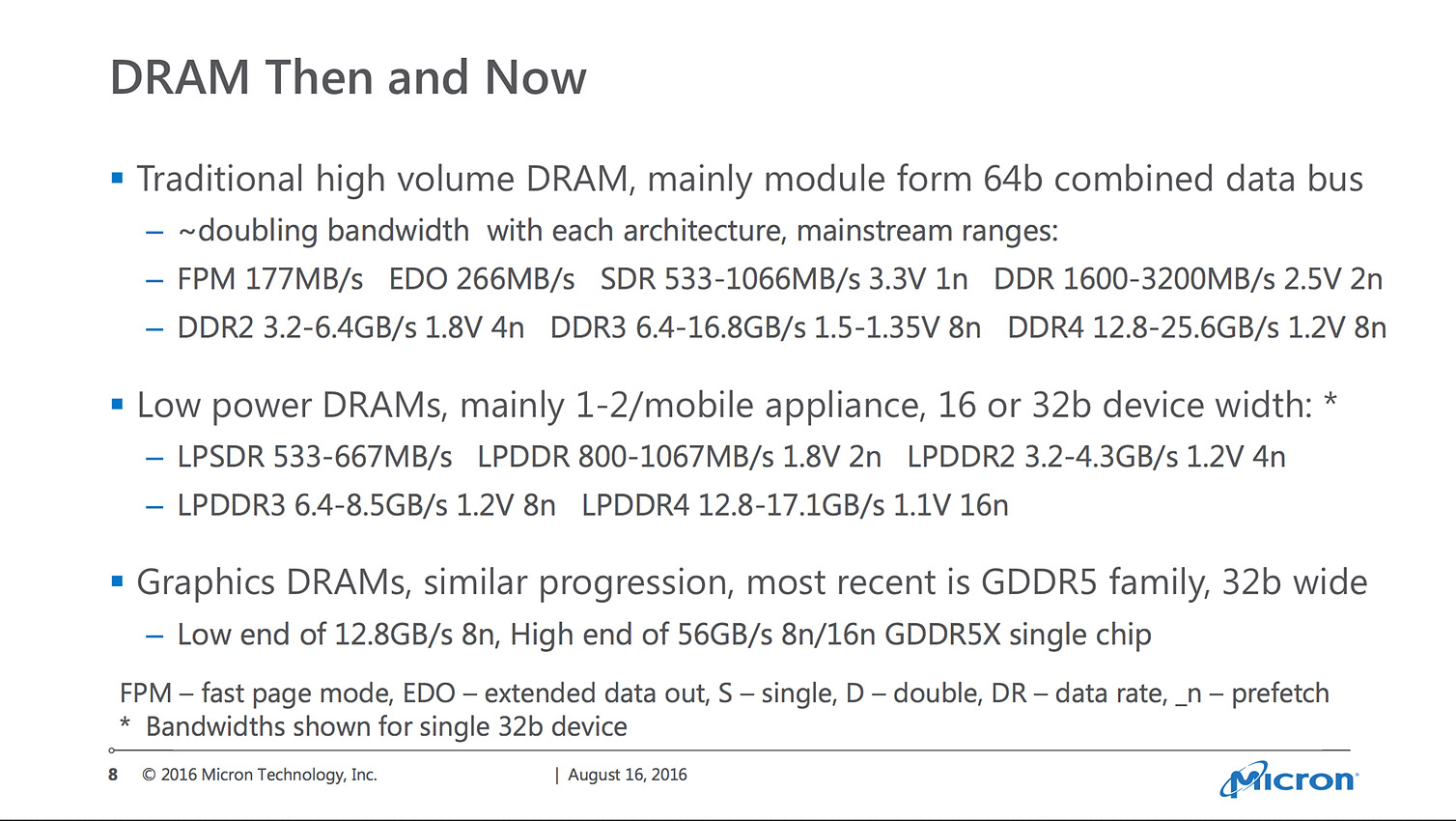

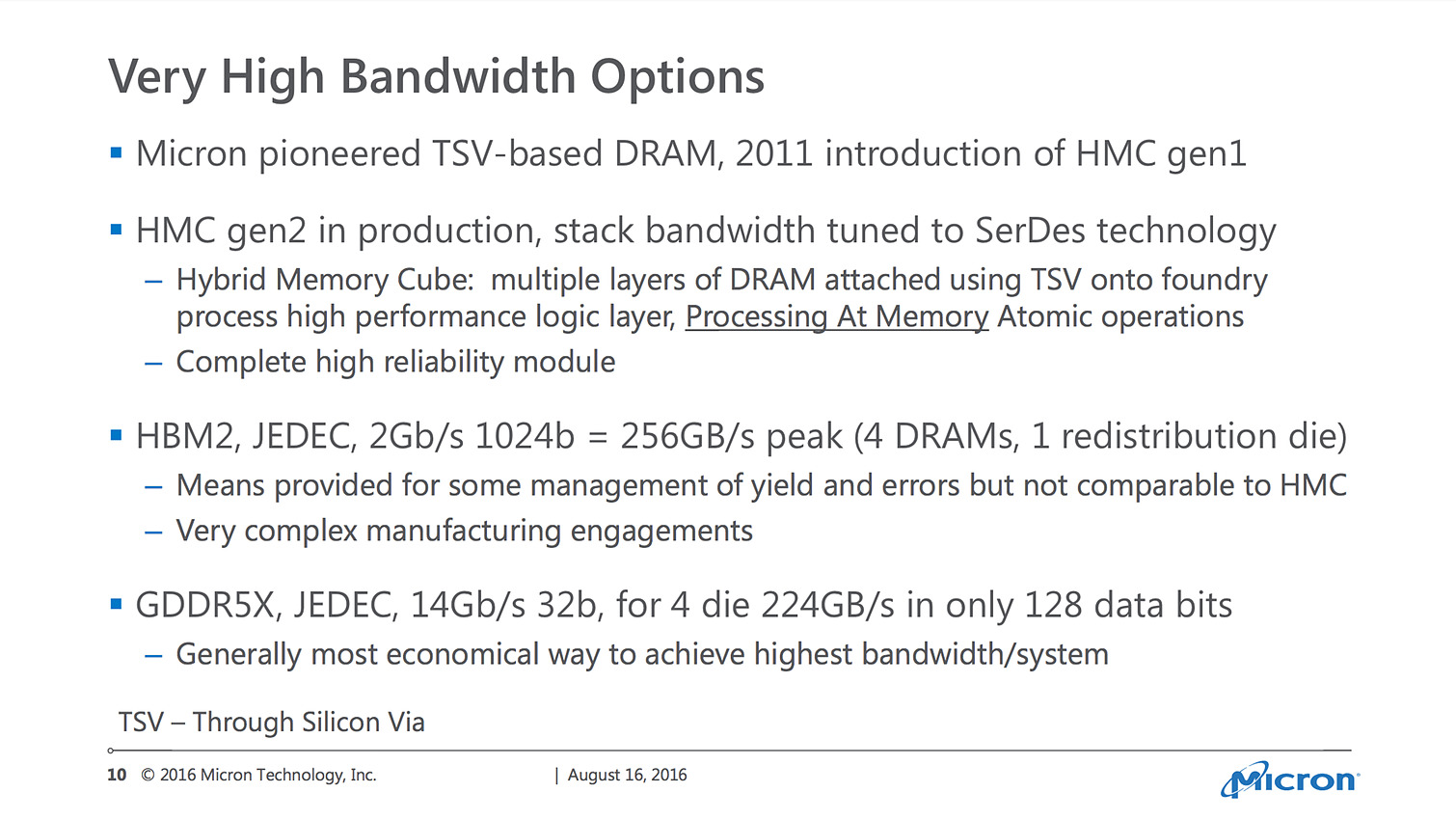

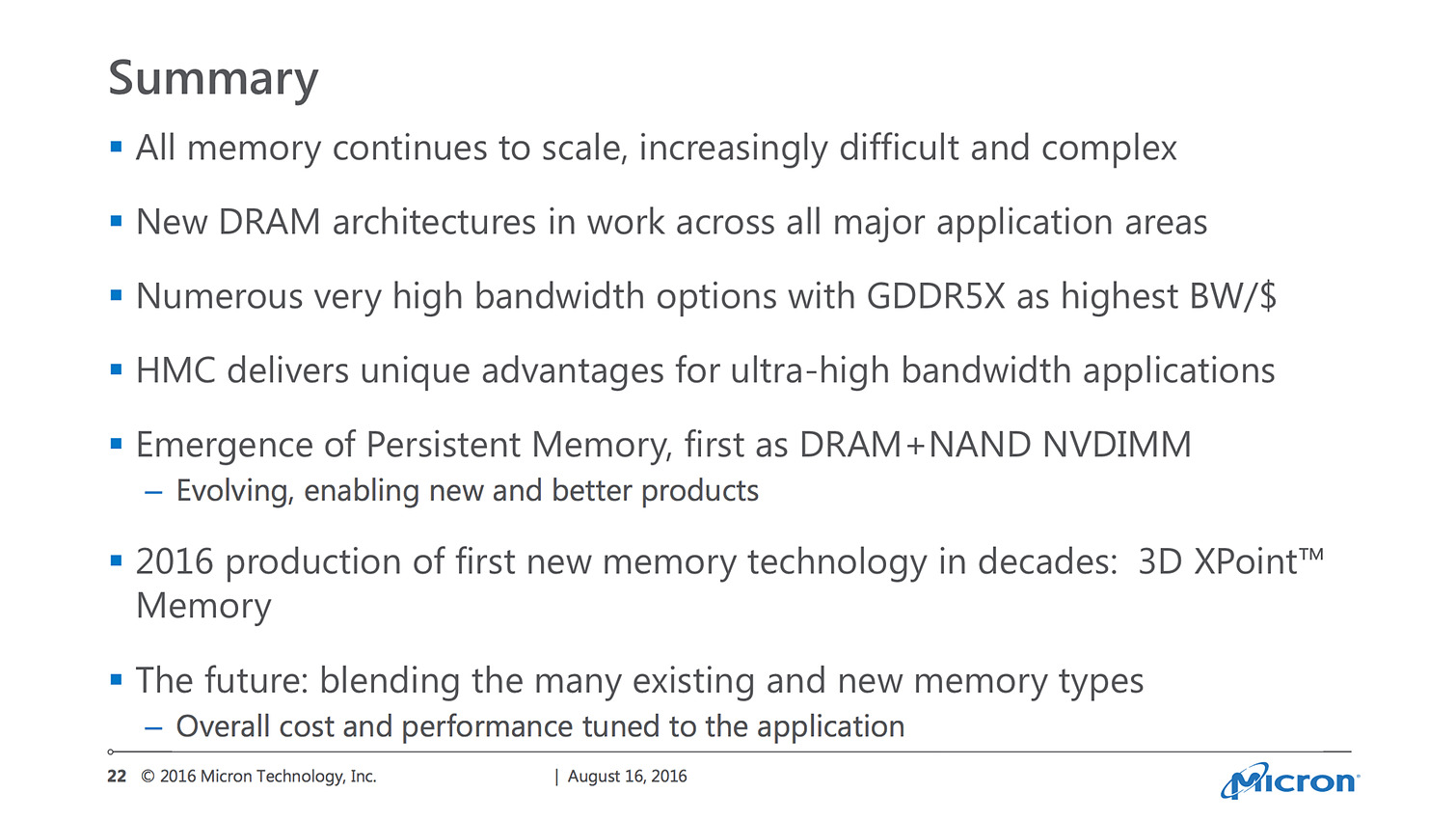

HMC, DDR5 et 3D XPoint pour Micron

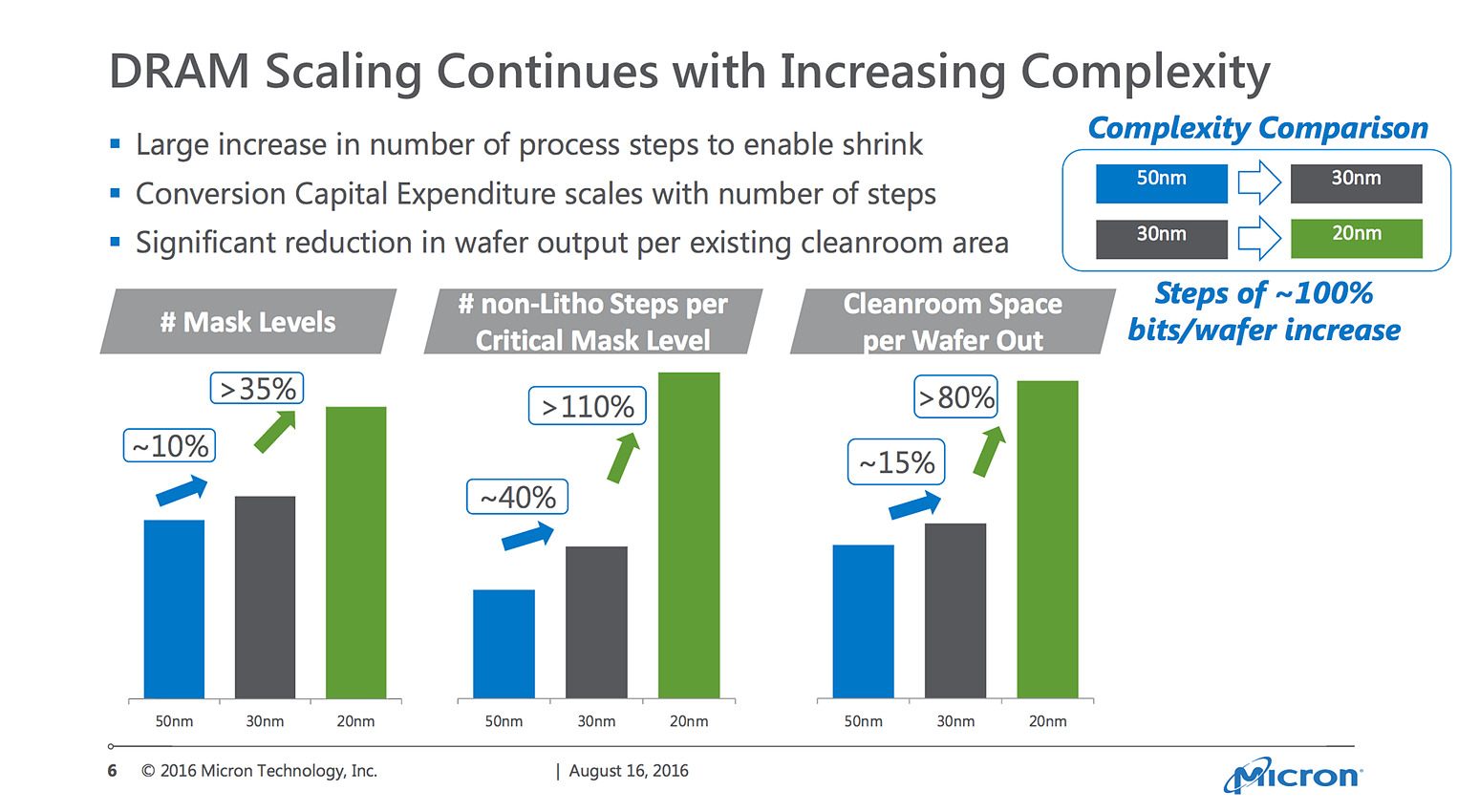

Micron a également pris la parole pendant la première matinée de Hot Chips, comme nous le rapportent une fois de plus nos confrères de ComputerBase . Ces derniers qualifient d'une honnêteté rafraîchissante la présentation de Micron, ne cherchant pas forcément à annoncer des chiffres extravagants. La société aurait même regretté, si l'on en croit nos confrères, que son partenaire Intel ait annoncé beaucoup trop tôt la mémoire 3D XPoint !

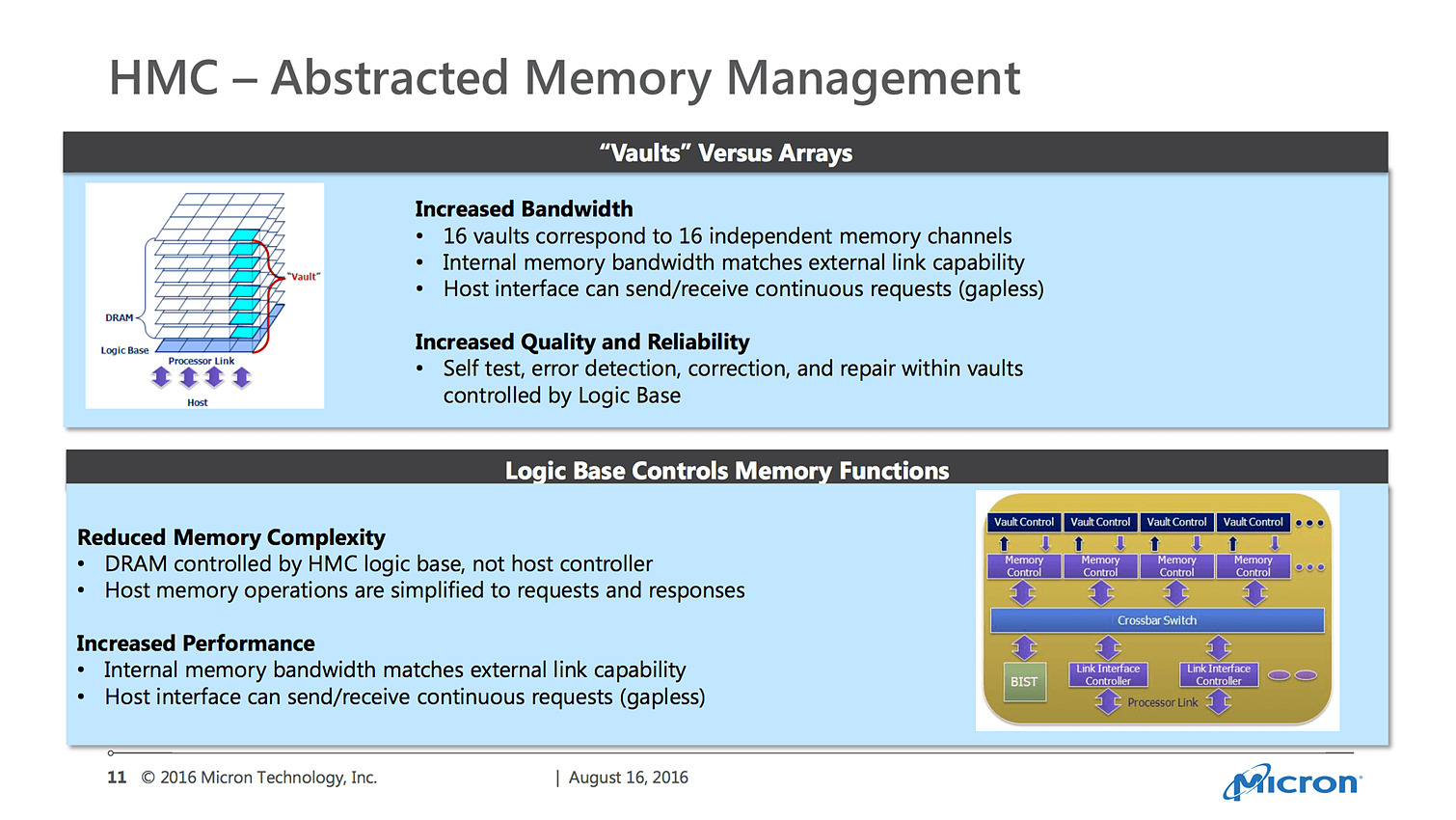

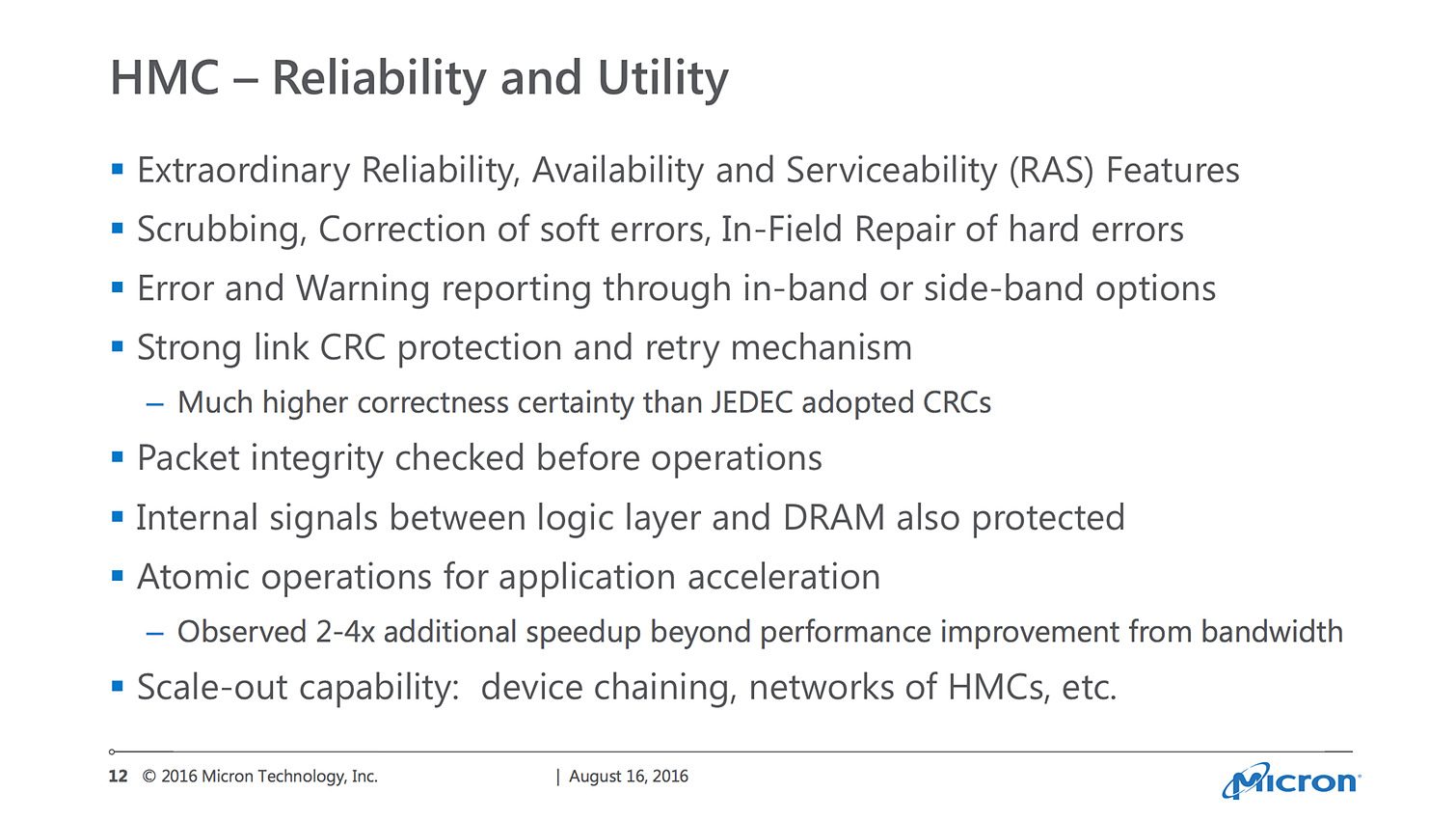

Dans le détail, Micron n'aura pas pu s'empêcher tout de même de qualifier la HBM de "mauvaise copie" de sa propre technologie Hybrid Memory Cube, plus complexe, coûteuse, et surtout assez peu disponible (elle devrait être présente sur le prochain Xeon Phi d'Intel, Knights Landing). Micron estime que la HMC dispose de nombreux avantages pour le marché du HPC, avec par exemple un meilleur algorithme de CRC que celui utilisé par le JEDEC pour la HBM.

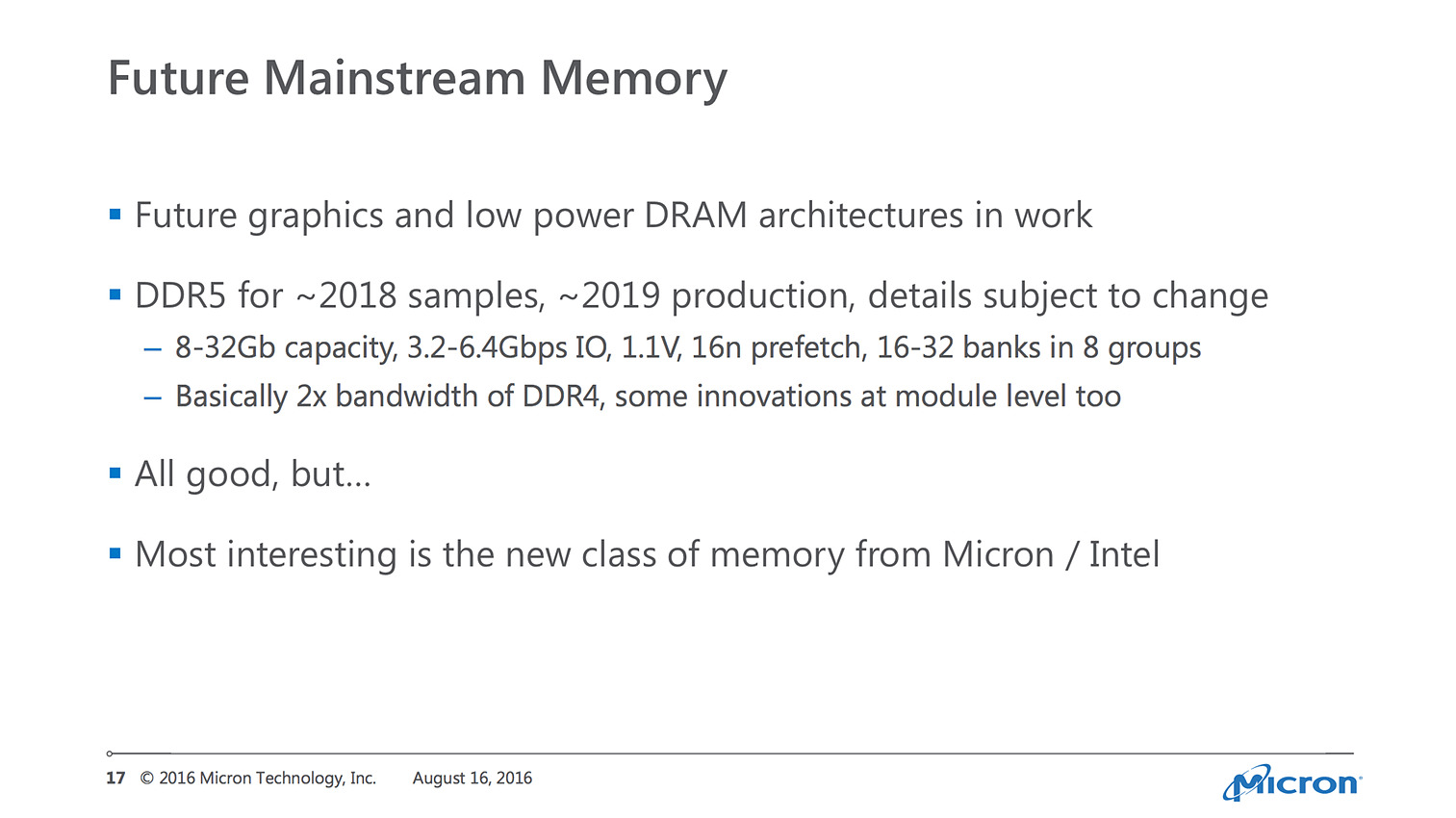

Micron aura également évoqué la DDR5 qui aura pour objectif de doubler la bande passante par rapport à la DDR4. Micron estime produire ses premiers échantillons courant 2018, avec une production en volume possiblement en 2019, mais plus probablement pour 2020.

Outre le tacle envers son partenaire Intel sur la mémoire 3D XPoint, on ne retiendra pas beaucoup d'informations, si ce n'est que Micron confirme que ce nouveau type de mémoire sera en production avant la fin de l'année.

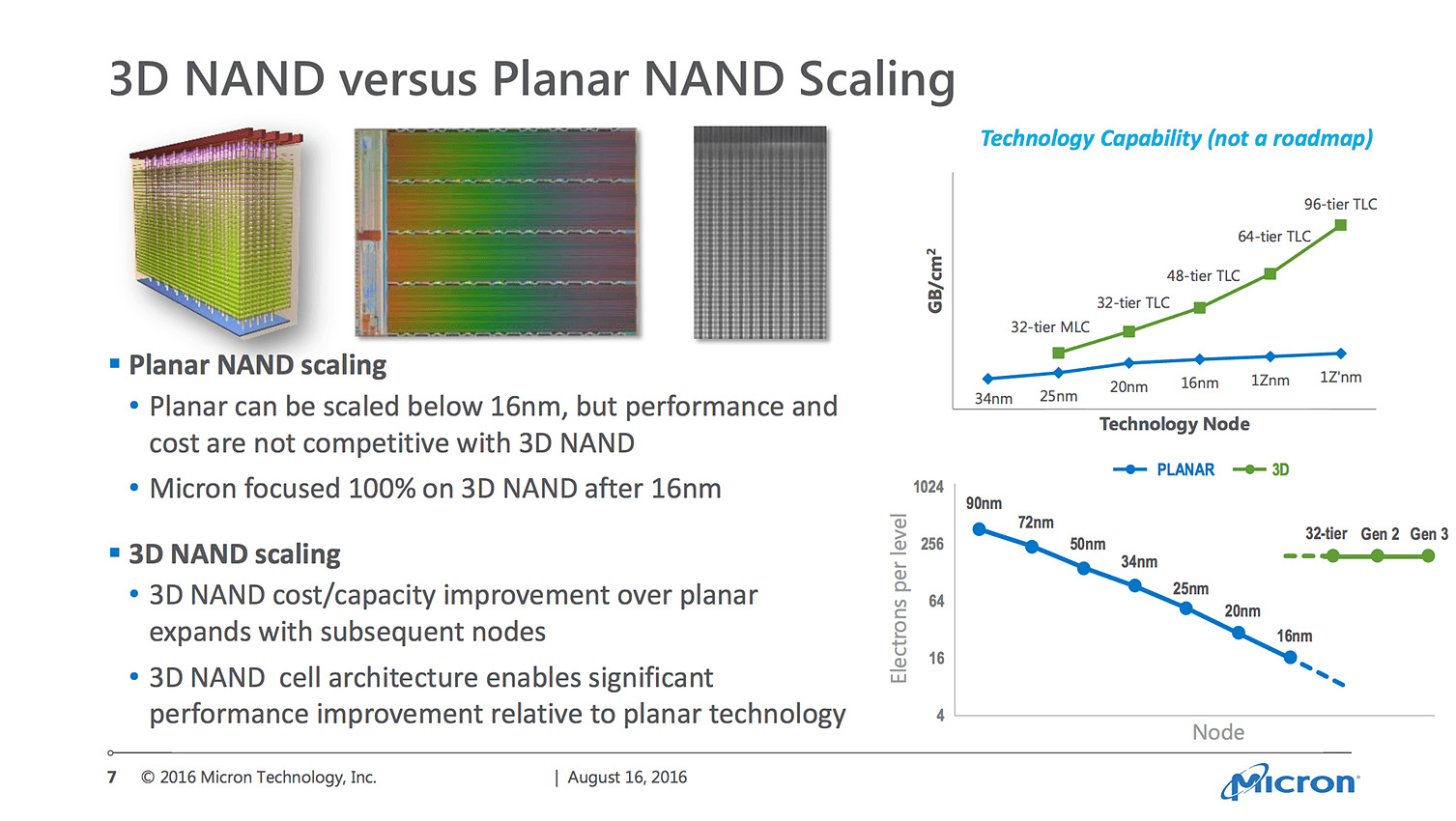

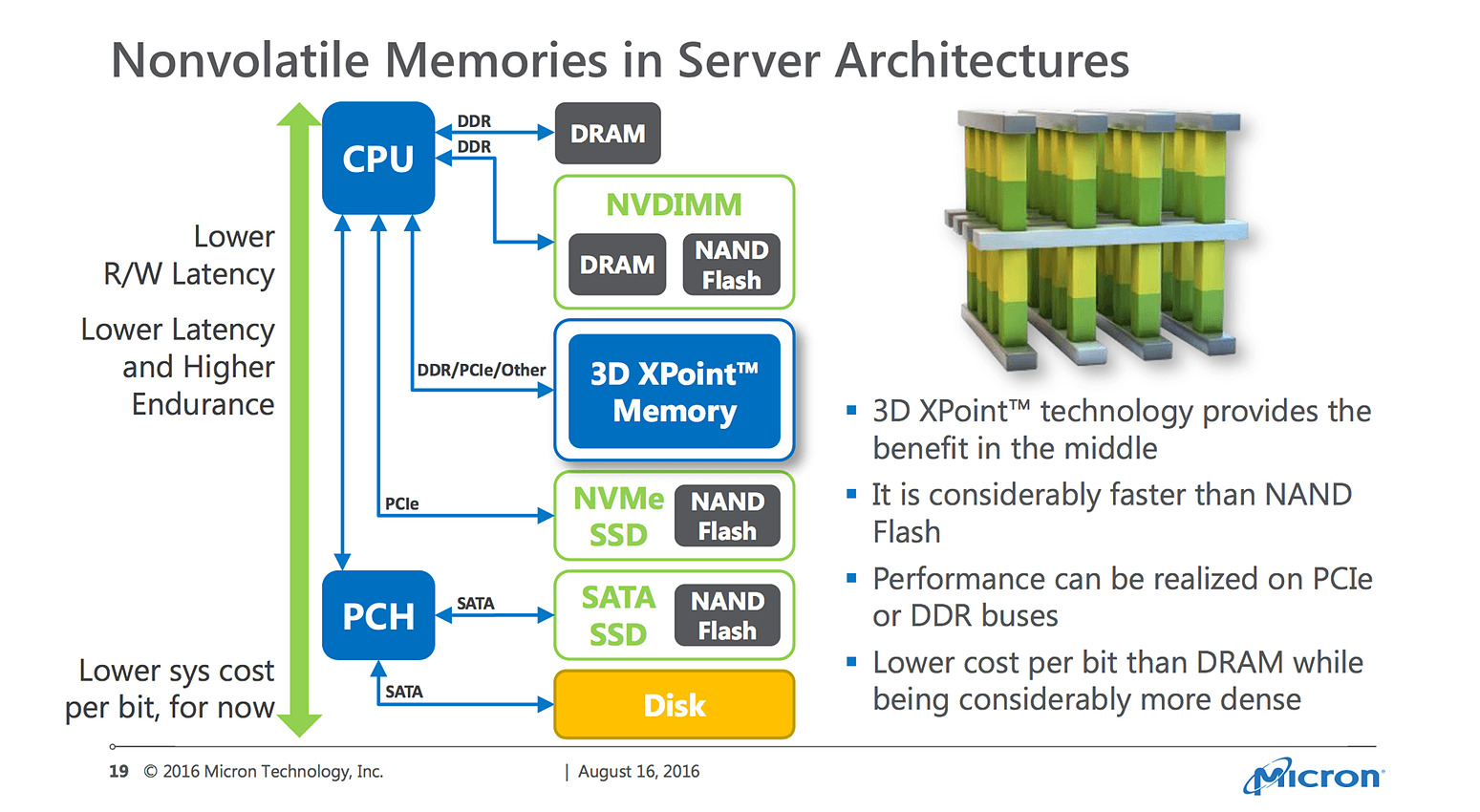

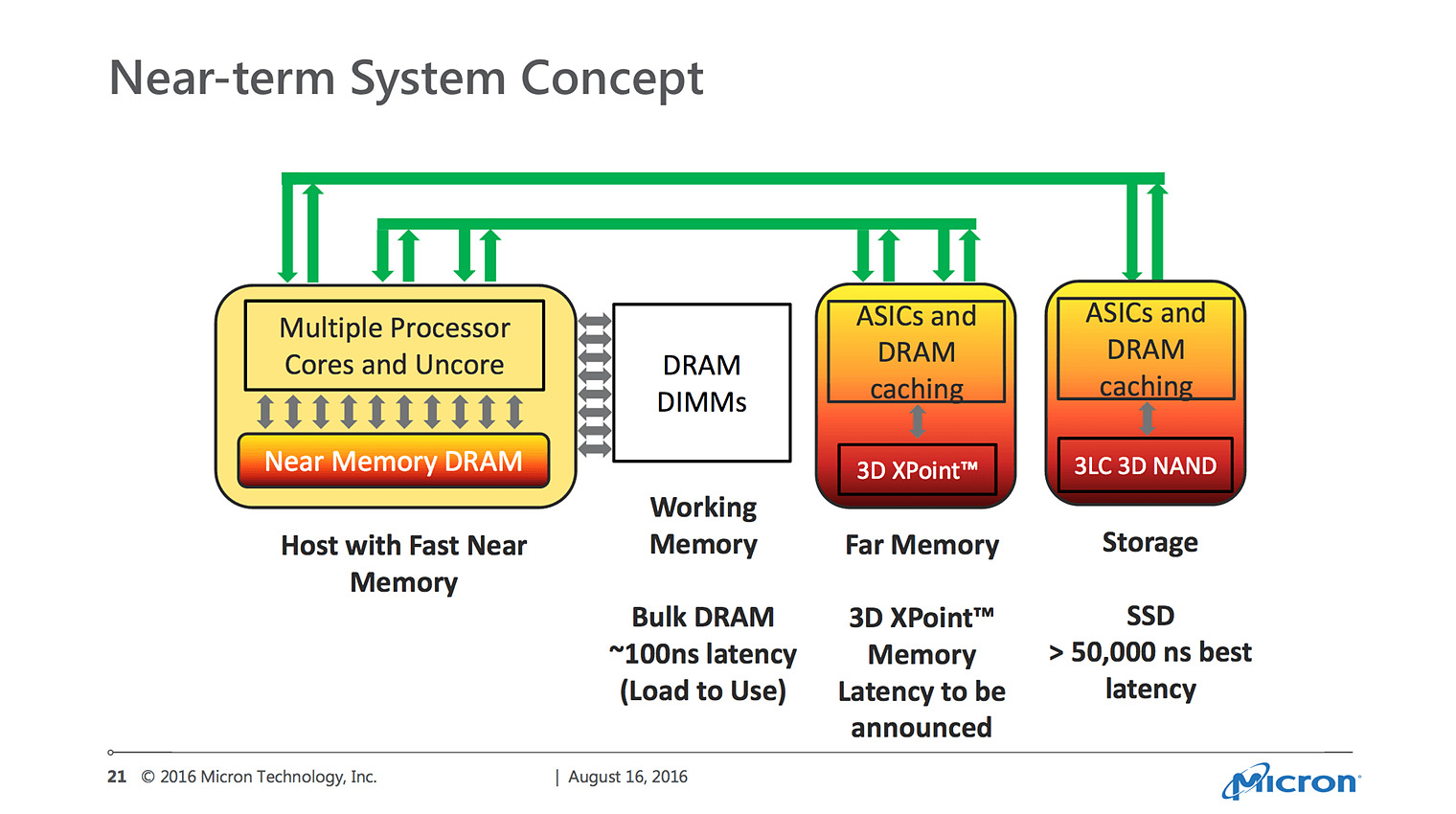

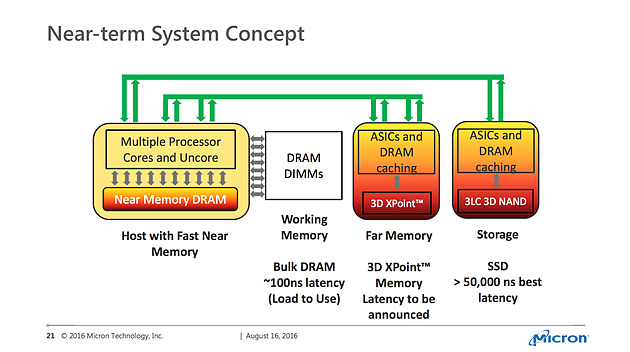

On retiendra ce dernier slide qui préfigure de ce que l'on devrait voir arriver sous peu sur les serveurs, avec deux tiers de mémoire DRAM. D'un côté une mémoire "proche", intégrée au processeur et rapide (HBM, ou plutôt HMC dans la vision de Micron) qui s'adjoint à la mémoire DRAM en barrettes plus classique. 3D XPoint et la 3D NAND proposant de leur côté deux tiers de stockages persistants.

Micron continue dans sa voie de l'originalité, dans un marché de la mémoire certes très concurrentiel. La société continue de mettre en avant sa GDDR5X, certes standardisée par le JEDEC mais qui n'a pas été adoptée par ses concurrents, mais aussi des solutions plus propriétaires comme l'Hybrid Memory Cube et 3D XPoint. Avec les ambitions de SK Hynix et de Samsung de pousser la HBM sur le terrain des PC clients, on peut cependant se demander si le pari d'ignorer la mémoire HBM ne se retournera pas contre Micron dans les mois à venir.