IDF printemps 2008 à Shanghai

Publié le 12/04/2008 par Damien Triolet

Nehalem et futur

Pour rappel, le core Nehalem est une évolution légère du core Penryn, le retour du multi-threading, quelques petites améliorations par-ci par-là, et l'ajout de quelques nouvelles instructions SSE. C'est du côté du "uncore", terme utilisé par Intel pour représenter le processeur dans son ensemble, qu'il y aura du neuf. Grossièrement nous pouvons dire que Nehalem s'inspire de la structure des Athlon 64 et autres Phenom. Ainsi, le contrôleur mémoire s'invite dans le CPU et la connectique évolue de l'antique FSB vers un bus plus moderne, QPI (Quick Path Interconnect). Nehalem gagne également en modularité. Cores, contrôleurs mémoire, cache L3, liens QPI, liens PCI Express, core graphique intégré sont ainsi tous des éléments modulables. Dans sa première incarnation, Bloomfield, Nehalem contiendra 4 cores équipés de 64 Ko de cache L1 et de 256 Ko de cache L2 qui se partageront 8 Mo de cache L3 et un triple contrôleur mémoire. Autrement dit, un Core 2 qui ne laissera plus aucun avantage structurel au Phenom d'AMD.

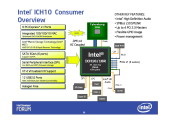

Nehalem était pourtant partout et fonctionnel sur le salon. Les samples tournaient à une fréquence de 3.2 GHz, mais les performances réelles n'ont pas encore pu être mesurées. Du côté du chipset, il sera réduit au strict minimum étant donné l'intégration du contrôleur mémoire. Le northbridge, l'IOH HEDT Tylersburg, n'est rien d'autre qu'un convertisseur QPI / PCI Express 2.0 qui gère 1 port 4x et 2 ports 16x qui peuvent être répartis en 4 ports 8x à l'aide de switchs sur la carte-mère. Le southbridge sera l'ICH10 qui par rapport à l'ICH9 n'apporte pas grand-chose pour ne pas dire rien, mais est plus écologique et ne contient plus de gaz halogène.

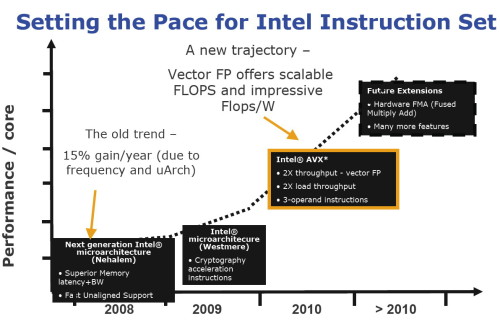

Et la suite ? Concernant l'après Nehalem, nous n'en avons là également pas appris beaucoup plus. La nouvelle architecture, Sandy Bridge, arrivera en 2010 et apportera un nouveau jeu d'instructions, AVX, destiné à remplacer le SSE. Contrairement à celui-ci qui travaille sur des registres 128 bits, AVX reposera sur des registres de 256 bits, et permettra donc de traiter des vecteurs plus grands et de gagner en flexibilité. Intel a précisé lors de cet IDF que la première implémentation d'AVX se ferait "à pleines performances". Entendez par là que Sandy bridge disposera d'unités de calcul vectorielles de 256 bits, alors qu'au départ, le SSE 128 bits était traité en plusieurs cycles par des unités de 64 bits.

Enfin Intel indique que la génération suivante, vers 2012, intègrera le FMA, Fused Multiply Add qui est le MAD dont il est souvent question lorsque nous parlons des GPUs. C'est en effet l'unité de calcul de base d'un GPU qui offre l'avantage de pouvoir de traiter 2 opérations en une seule. Une combinaison souvent utile en graphisme. Son intégration au cur des unités d'exécution des CPUs témoigne bien entendu de la convergence de leurs architectures.

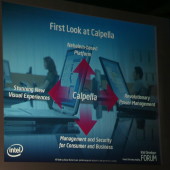

Plateforme mobileSi Intel a bien sûr évoqué sa future plateforme mobile Montevina, ou Centrino 2 "première version", qui débarquera dans la seconde moitié de l'année et qui apportera principalement l'utilisation d'un nouveau chipset avec core graphique de classe G45, le fabricant a également brièvement évoqué Calpbella. Cette plateforme mobile de 2009 reposera sur une toute nouvelle architecture puisqu'en son cur se trouvera un CPU dérivé de l'architecture Nehalem qui sauf surprise devrait être un CPU dualcore qui intégrera le core graphique, le contrôleur mémoire et la gestion du PCI Express.

Outre le gain de performance, on imagine aisément que sur le plan énergétique cette solution devrait apporter des avantages significatifs. Intel n'a cependant donné aucun élément concret au sujet de cette plateforme.

Sommaire

Vos réactions

Contenus relatifs

- [+] 09/12: Guide : Les PC HardWare.fr !

- [+] 14/11: Qualcomm dit non à Broadcom

- [+] 13/11: Thermaltake lance une chaise venti...

- [+] 11/09: Microsoft confirme des problèmes de...

- [+] 30/08: PCI Express 5.0 pour 2019, débit do...

- [+] 01/08: Les taux de retour des composants (...

- [+] 11/07: Le minage consommerait plus que Par...

- [+] 04/07: ASUS XG-C100C, le 10GBASE-T à 120

- [+] 26/06: Computex et le PC : changement et c...

- [+] 24/03: Corsair lance ses PC One avec deux ...