Preview : Ageia PhysX

Publié le 05/05/2006 par Damien Triolet

Le PPU

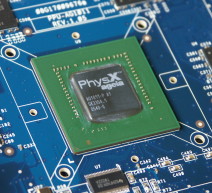

Première puce dédiée à la physique, le PPU dAgeia reste assez mystérieux étant donné que les détails techniques sont très peu nombreux à son sujet. Tout au plus sait-on que la puce embarque 125 millions de transistors pour une surface de +/- 190 mm². Ageia parle vaguement de 20 milliards dinstructions par seconde ce qui représente 530 millions de collisions sphère/sphère (les plus simples) ou 533 mille collisions entre objets convexes (plus complexes) par seconde.

Première puce dédiée à la physique, le PPU dAgeia reste assez mystérieux étant donné que les détails techniques sont très peu nombreux à son sujet. Tout au plus sait-on que la puce embarque 125 millions de transistors pour une surface de +/- 190 mm². Ageia parle vaguement de 20 milliards dinstructions par seconde ce qui représente 530 millions de collisions sphère/sphère (les plus simples) ou 533 mille collisions entre objets convexes (plus complexes) par seconde. La puce PhysX dispose dune interface PCI et dun bus mémoire 128 bits. Des choix assez conservateurs puisque le bus PCI est maintenant en train de disparaître au profit du PCI Express. Le bus mémoire correspond à ce que lon retrouve sur une carte graphique milieu de gamme mais est ici associé à de la mémoire DDR peu rapide : 366 MHz. Probablement par souci déconomie. Il en résulte une bande passante dédiée de 10.9 Go/s.

Ageia a défini 4 buts au processeur PhysX : Scale, Fidelity, Interaction et Sophistication. Soit une augmentation du nombre de détails physiques, de leur réalisme et de la manière dont ils interagissent ensemble. Le 4ème point est le bouche trou marketing habituel quon retrouve régulièrement en 3d : la qualité "Hollywood".

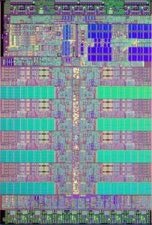

Pour atteindre ces buts, le processeur PhysX est équipé dun nombre important dunités de calcul de différents types : scalaires sur les entiers et vectorielles sur les flottants. Les premières devraient principalement servir à prendre en charge le flow control soit tout ce qui modifie le flux dinstructions : branchements etc. Ces unités sont organisées en groupes indépendants mais qui fonctionnent en interne à la manière dunités SIMD cest-à-dire que chaque unité de traitement effectue la même tâche, mais chaque groupe peut travailler sur un programme différent.

Pour en savoir plus la seule solution est de se plonger dans les brevets dAgeia. Cependant, ceux-ci définissent différentes approches au niveau du design et ceux-ci peuvent être étendus via lajout dunités de traitement supplémentaires. Nous ne pouvons donc pas savoir avec certitude sils représentent le design final de la puce PhysX ou simplement un exemple de design, le final ayant alors été adapté au niveau du nombre de chaque unité. Le design probable que lon retrouve dans ces brevets fait état de 4 blocs de calcul indépendants, les Vector Processing Engines qui comprennent chacun 4 Vector Processing Units. Il sagit donc de 4x 4 unités de calcul. Chacune de ces unités contient 6 MAD flottants (unité capable deffectuer une multiplication et une addition) et une ALU entière. Cela fait donc un total de 96 MADs à comparer aux 56 que lon retrouve dans les GPU haut de gamme dATI et Nvidia. Reste la fréquence qui est inconnue ! 366 MHz, comme la mémoire ? 250 MHz, 500 MHz ? Nous nen savons rien. Difficile donc dévaluer pour la forme la puissance de calcul brute du PPU et de la comparer à dautres puces. Bien entendu il ne sagirait de toute manière que dune image puisque la puissance brute na que peu dintérêt si elle nest pas utilisée efficacement.

Cest dailleurs là que se trouve toute la force de la puce dAgeia. Les calculs physiques ont des propriétés très différentes des calculs 3D. Lorsque les pixels sont calculés, ils le sont indépendamment les uns des autres et les accès mémoire sont dans la majorité des cas alignés dune manière optimale. Avec la physique, les objets interagissent entre eux, autrement dit, on ne peut pas connaître la position dun débris sans connaître celle des autres puisquils peuvent entrer en collision et ainsi modifier leur trajectoire. Etant donné que les résultats des autres unités ne peuvent pas être connus instantanément, un nombre importants de petits threads sont utilisés, comme le fait ATI, de manière à masquer la latence.

Ce mode de fonctionnement entraîne un déplacement massif de données entre les différentes unités de calcul du PPU mais également des écritures et lectures mémoire moins prévisibles. Pour ces raisons, Ageia a dû mettre au point un Data Movement Engine (DME) très évolué qui contient 5 Memory Control Unit (MCU). 4 dentre elles gèrent les transferts de données de et vers chacun des 4 VPE via un bus sur lequel chaque VPU vient se raccorder. Chaque VPU contient une petite mémoire à laquelle il peut accéder lui-même bien entendu, mais à laquelle le DME peut accéder également. Cette mémoire fonctionne à la manière dun double buffer. Le VPU accède au premier buffer pendant que le DME accède au second. Dès que les lectures / écritures sont terminées, les buffers sont inversés. Ce système permet au VPU et DME daccéder à la mémoire en même temps, à pleine vitesse. La cinquième MCU se connecte au PCE (PPU Control Engine), le chef dorchestre du processeur PhysX.

Ageia parle dune bande passante interne bidirectionnelle de 250 Go/s ce qui est impressionnant. Le DME semble au final être la partie la plus importante du PPU. Sans lui, les unités de calcul ne pourraient pas être alimentées correctement. Cest également lui qui prend en charge laccès à la mémoire dédiée via la Memory Interface Unit ainsi que la gestion du bus PCI. Notez à ce sujet quAgeia précise que sa technologie est capable dêtre interfacée en PCI Express, en USB et en FireWire. Mais lexemple de design que nous supposons correspondre à limplémentation actuelle du PPU est basée sur le bus PCI. Autrement dit pour supporter le bus PCI Express Ageia devra mettre à jour le DME et fabriquer une puce différente.

Au final, cette architecture nous fait directement penser à un autre processeur : le Cell. Lui aussi dispose dun cur dexécution principal / de gestion, dun nombre important dunités de calcul spécialisées et dun système mémoire avancé. Le parallèle est évident et il est probablement juste de voir le PPU comme un Cell spécialisé en physique.

Au final, cette architecture nous fait directement penser à un autre processeur : le Cell. Lui aussi dispose dun cur dexécution principal / de gestion, dun nombre important dunités de calcul spécialisées et dun système mémoire avancé. Le parallèle est évident et il est probablement juste de voir le PPU comme un Cell spécialisé en physique.Il est possible quAgeia désactive certaines unités de traitement de manière à améliorer le yield. Au vu de cette architecture, la seule partie désactivable et qui ferait augmenter significativement le yield par sa taille serait un VPE. Difficile de savoir si cest le cas ou pas mais cette supposition est renforcée par le fait quAgeia indique dans son SDK que le PPU ne peut gérer que 3 scènes physiques en même temps. Bien entendu il est possible que cette limitation ait une autre source que le nombre de VPE actifs.

Sommaire

Vos réactions

Contenus relatifs

- [+] 09/12: Guide : Les PC HardWare.fr !

- [+] 14/11: Qualcomm dit non à Broadcom

- [+] 13/11: Thermaltake lance une chaise venti...

- [+] 11/09: Microsoft confirme des problèmes de...

- [+] 30/08: PCI Express 5.0 pour 2019, débit do...

- [+] 01/08: Les taux de retour des composants (...

- [+] 11/07: Le minage consommerait plus que Par...

- [+] 04/07: ASUS XG-C100C, le 10GBASE-T à 120

- [+] 26/06: Computex et le PC : changement et c...

- [+] 24/03: Corsair lance ses PC One avec deux ...