Les derniers contenus liés au tag Xeon Phi

Afficher sous forme de : Titre | FluxIntel dévoile l'AVX-512

AVX3 et PCI Express 4.0 chez Intel

GTC: Les Tesla K20X dans le Piz Daint suisse

Intel lance les Xeon Phi 5110P

Cray XC30 avec processeurs Intel

Xeon Platinum pour accompagner les Xeon Gold

HMC, DDR5 et 3D XPoint pour Micron

76 coeurs sur le die de Knights Landing

Micron en charge de la mémoire des Knights Landing

Des détails sur les (monstrueux) Xeon Phi de 2015

Xeon Platinum pour accompagner les Xeon Gold

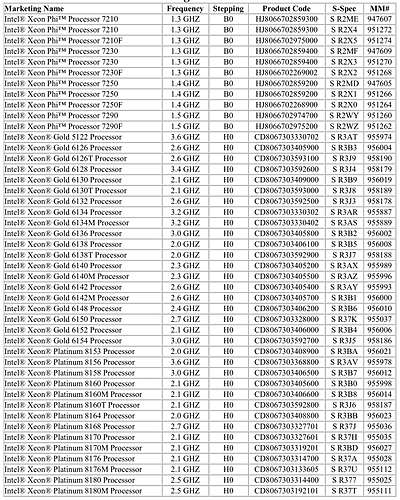

Il y a quelques semaines de cela, nous vous indiquions que la nomenclature Xeon Gold devrait faire son apparition à l'occasion du lancement des Skylake-EP, nous faisant nous poser pas mal de question sur ce qui se cachait derrière.

On comprend un peu mieux la question du Gold aujourd'hui grâce à un PCN (PDF) . En pratique, ce PCN (Product Change Notification, un document qui indique un changement au niveau du produit) indique simplement l'ajout d'un marquage supplémentaire sur l'IHS pour pouvoir repérer plus facilement le sens dans lequel insérer ces (bien larges) puces dans les sockets.

Mais en donnant la liste des produits affectés, Intel nous dévoile en parallèle la liste de ses futurs Xeon :

Toutes ces puces utiliseront le futur socket LGA 3647 qui représentera l'offre serveur très haut de gamme du constructeur. Le nombre colossal de broches s'explique par le fait que chaque socket pourra gérer jusque 6 canaux mémoires (avec 3 DIMM par canal). On devrait retrouver des configurations jusque 8 sockets qui pourront accueillir ces nouvelles puces.

La marque Xeon Gold représentera donc les Xeon 6000 tandis qu'une nouvelle marque, Xeon Platinum (!) sera réservée aux modèles 8000. On ne connaît pas encore les différences de cette segmentation (le PCN n'indique que les numéros de modèles, pas encore les caractéristiques) mais historiquement le premier numéro permettait de distinguer le nombre de sockets gérés.

On peut supposer que les modèles 8000 seront réservés pour les modèles 8 sockets, et les 6000 possiblement pour les 4 sockets, même si Intel pourrait changer ses habitudes. Le plus gros des Xeon 8000 intégrera 28 coeurs, soit quatre de plus que l'actuel Xeon E7-8894 v4.

On notera que des Xeon Phi en version socket seront là aussi disponibles, mais ils n'ont pas droit à un métal, on imagine pour éviter toute confusion. Si Intel suit sa logique, on devrait voir arriver des Xeon Silver et Bronze, possiblement pour le socket LGA 2066 qui remplacera l'actuel LGA 2011v3 avec le lancement des Xeon Skylake-W.

La version desktop du LGA 2066 (Skylake-X) a vu son lancement avancé à fin juin/début juillet, avec une introduction probable aux alentours du Computex comme nous vous l'indiquions il y a quelques jours.

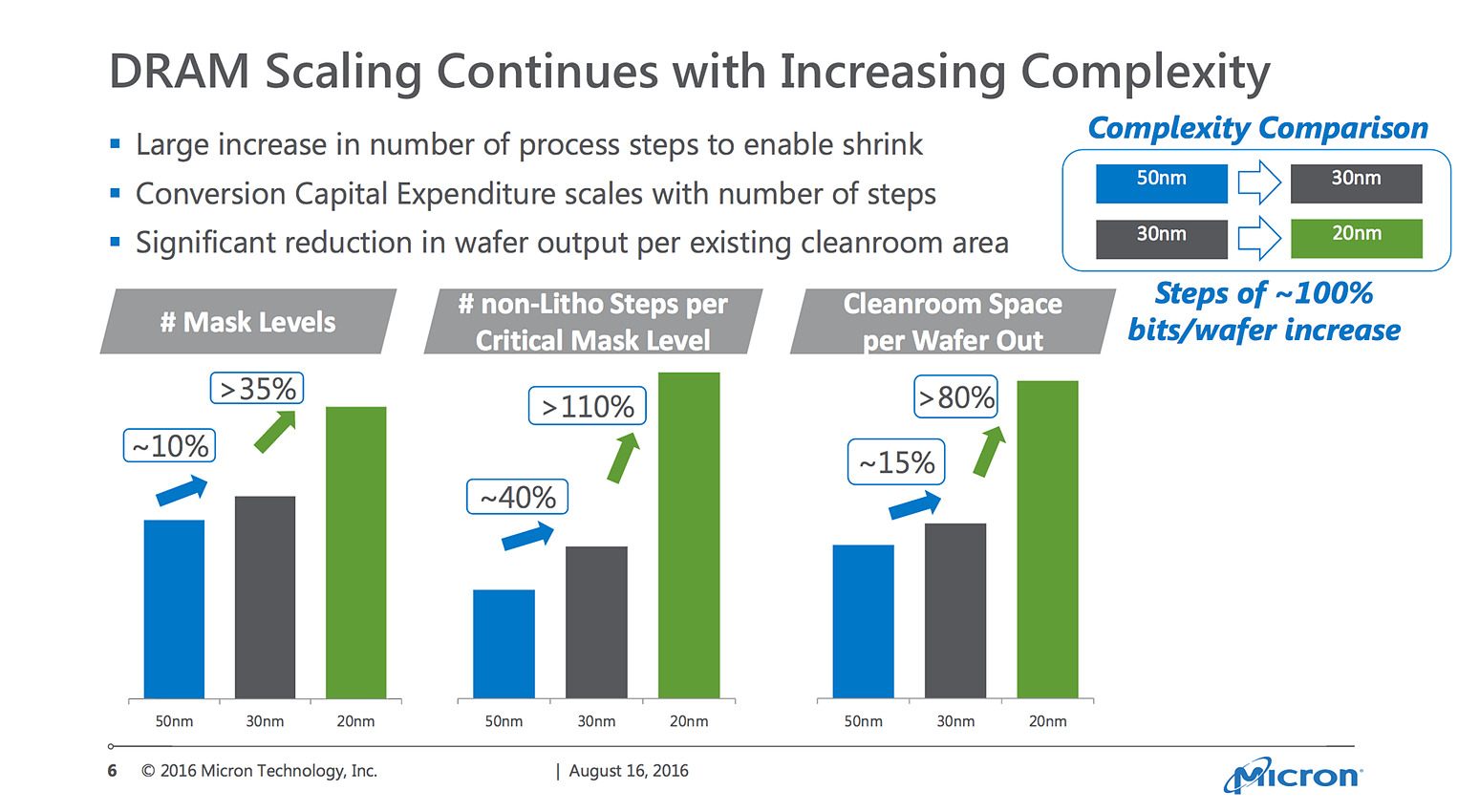

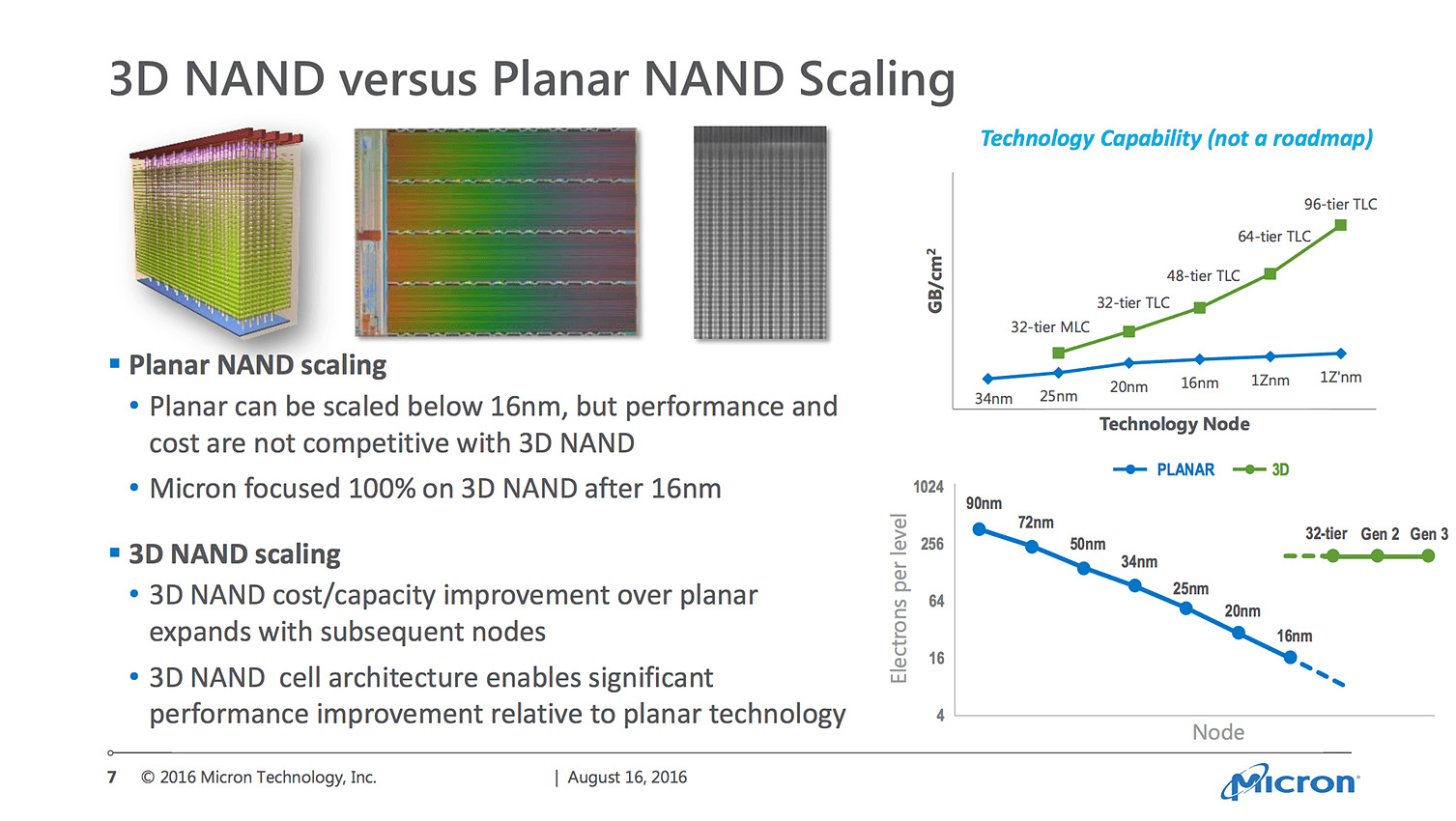

HMC, DDR5 et 3D XPoint pour Micron

Micron a également pris la parole pendant la première matinée de Hot Chips, comme nous le rapportent une fois de plus nos confrères de ComputerBase . Ces derniers qualifient d'une honnêteté rafraîchissante la présentation de Micron, ne cherchant pas forcément à annoncer des chiffres extravagants. La société aurait même regretté, si l'on en croit nos confrères, que son partenaire Intel ait annoncé beaucoup trop tôt la mémoire 3D XPoint !

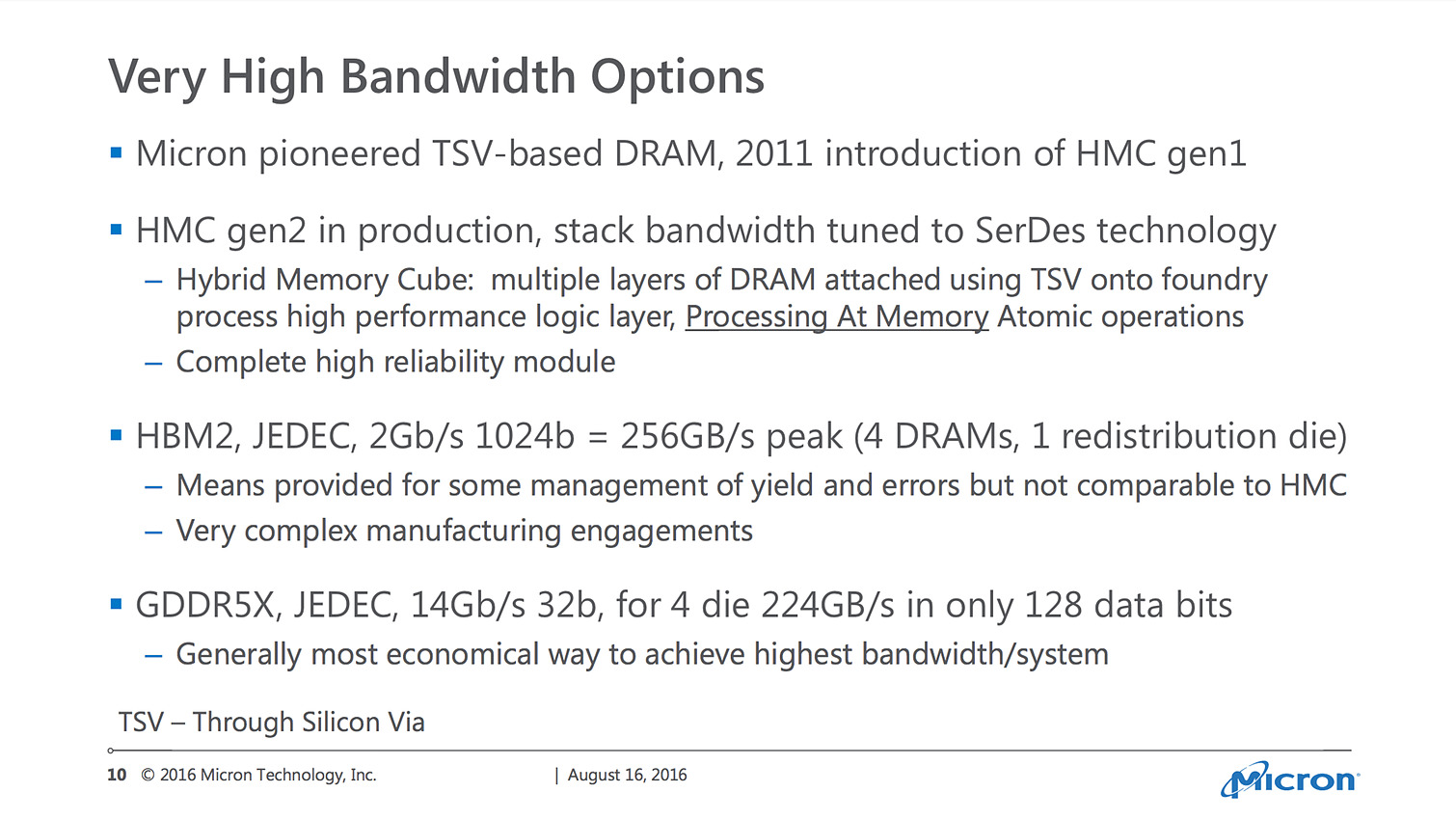

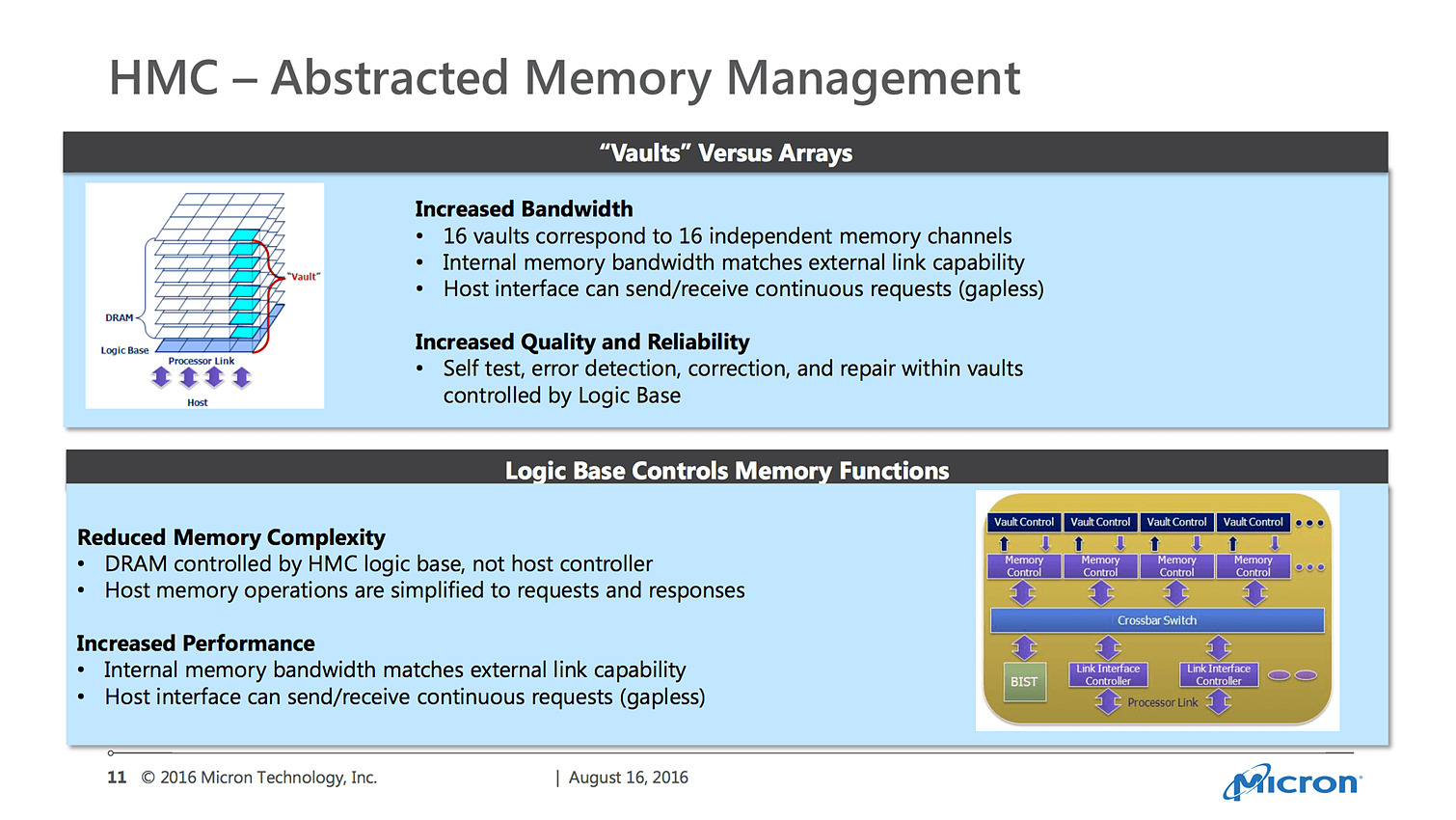

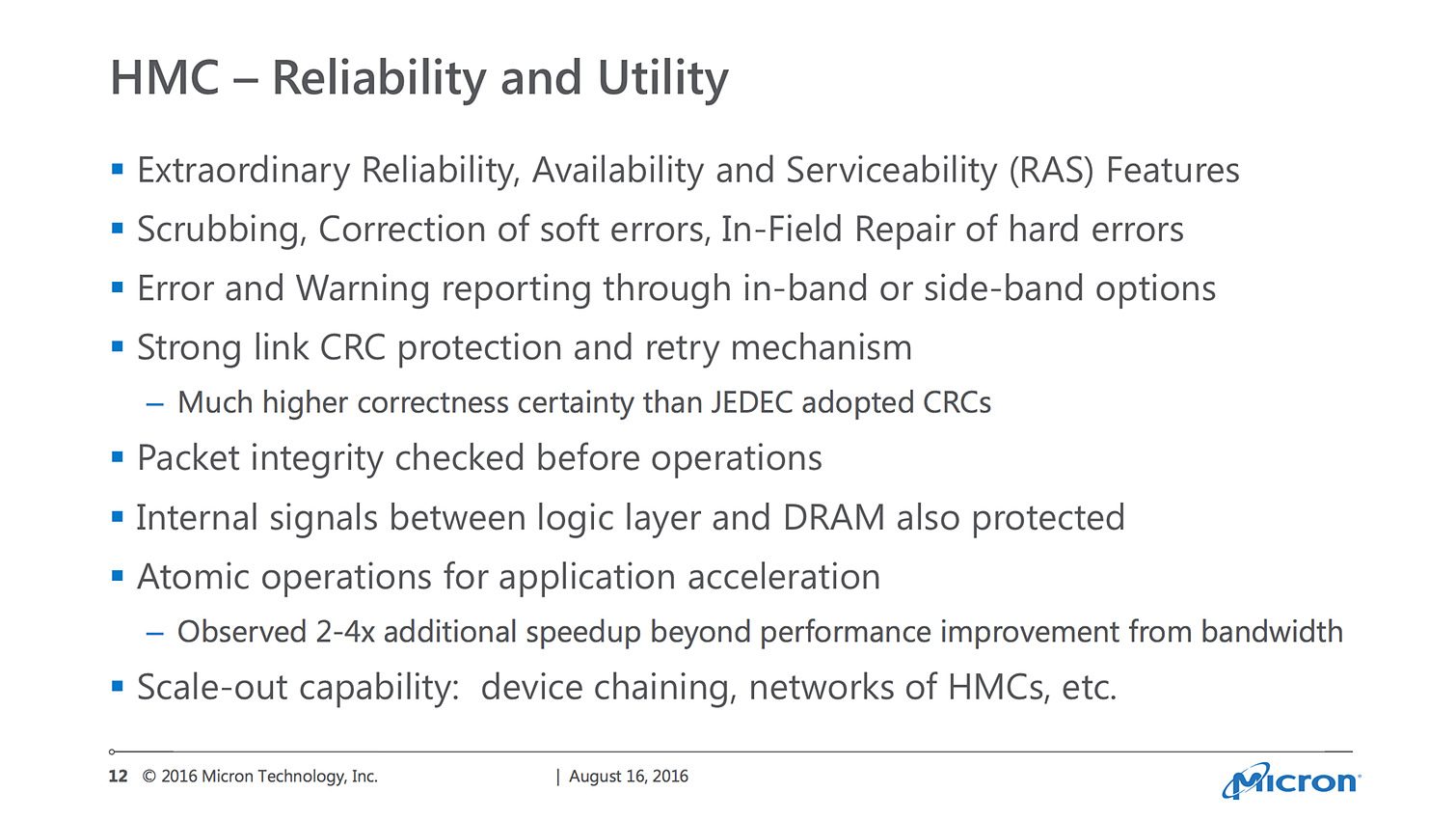

Dans le détail, Micron n'aura pas pu s'empêcher tout de même de qualifier la HBM de "mauvaise copie" de sa propre technologie Hybrid Memory Cube, plus complexe, coûteuse, et surtout assez peu disponible (elle devrait être présente sur le prochain Xeon Phi d'Intel, Knights Landing). Micron estime que la HMC dispose de nombreux avantages pour le marché du HPC, avec par exemple un meilleur algorithme de CRC que celui utilisé par le JEDEC pour la HBM.

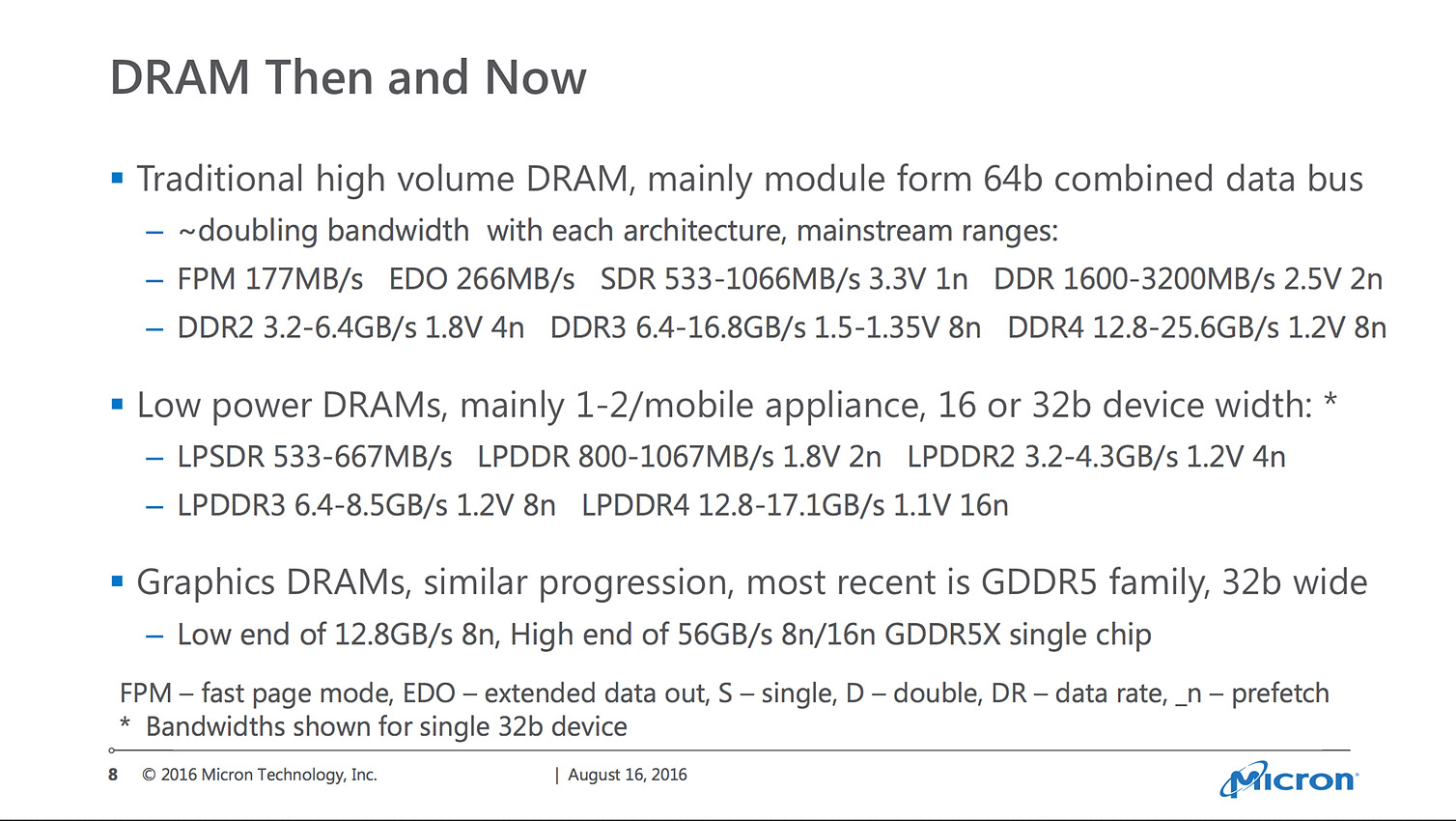

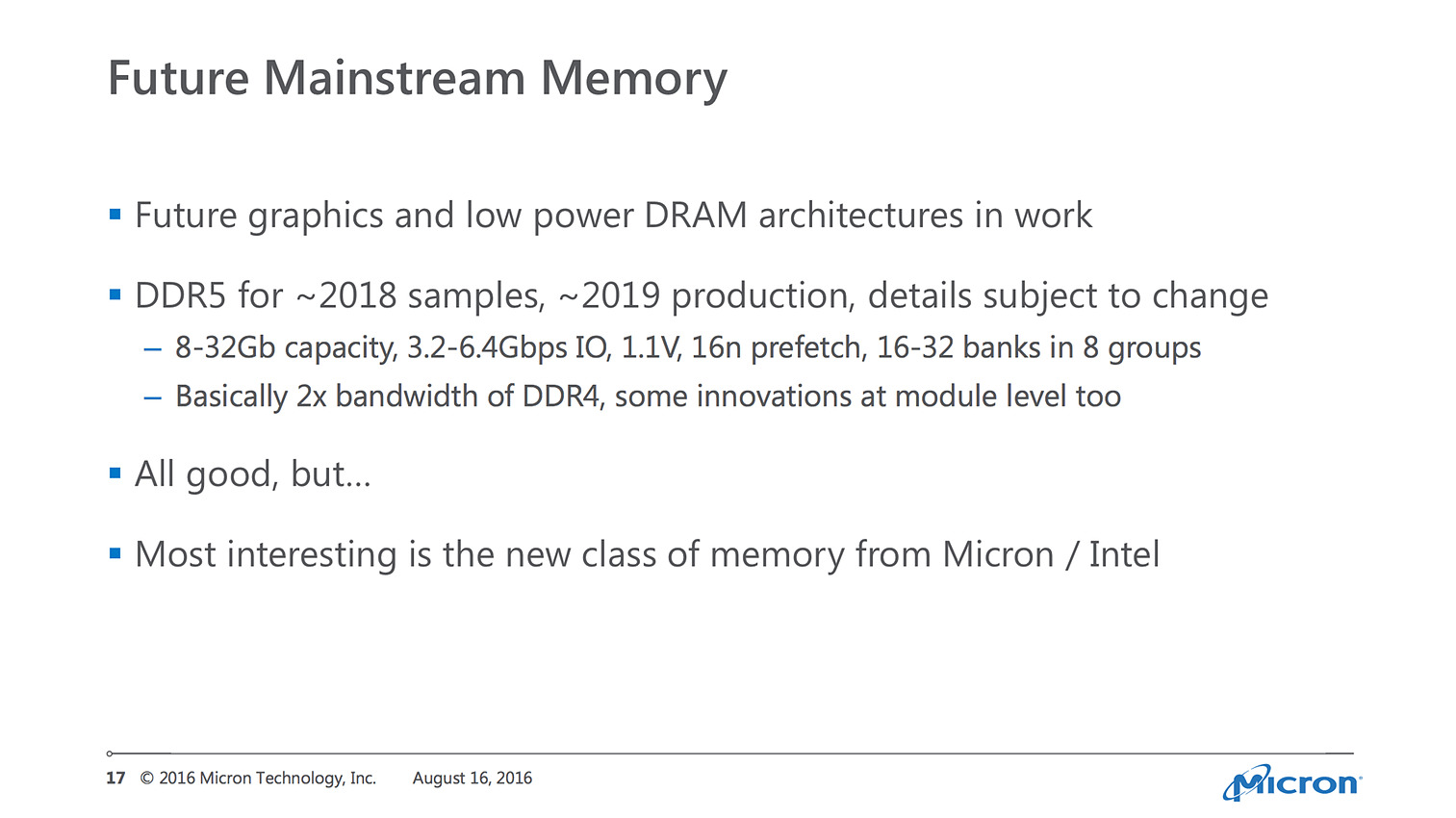

Micron aura également évoqué la DDR5 qui aura pour objectif de doubler la bande passante par rapport à la DDR4. Micron estime produire ses premiers échantillons courant 2018, avec une production en volume possiblement en 2019, mais plus probablement pour 2020.

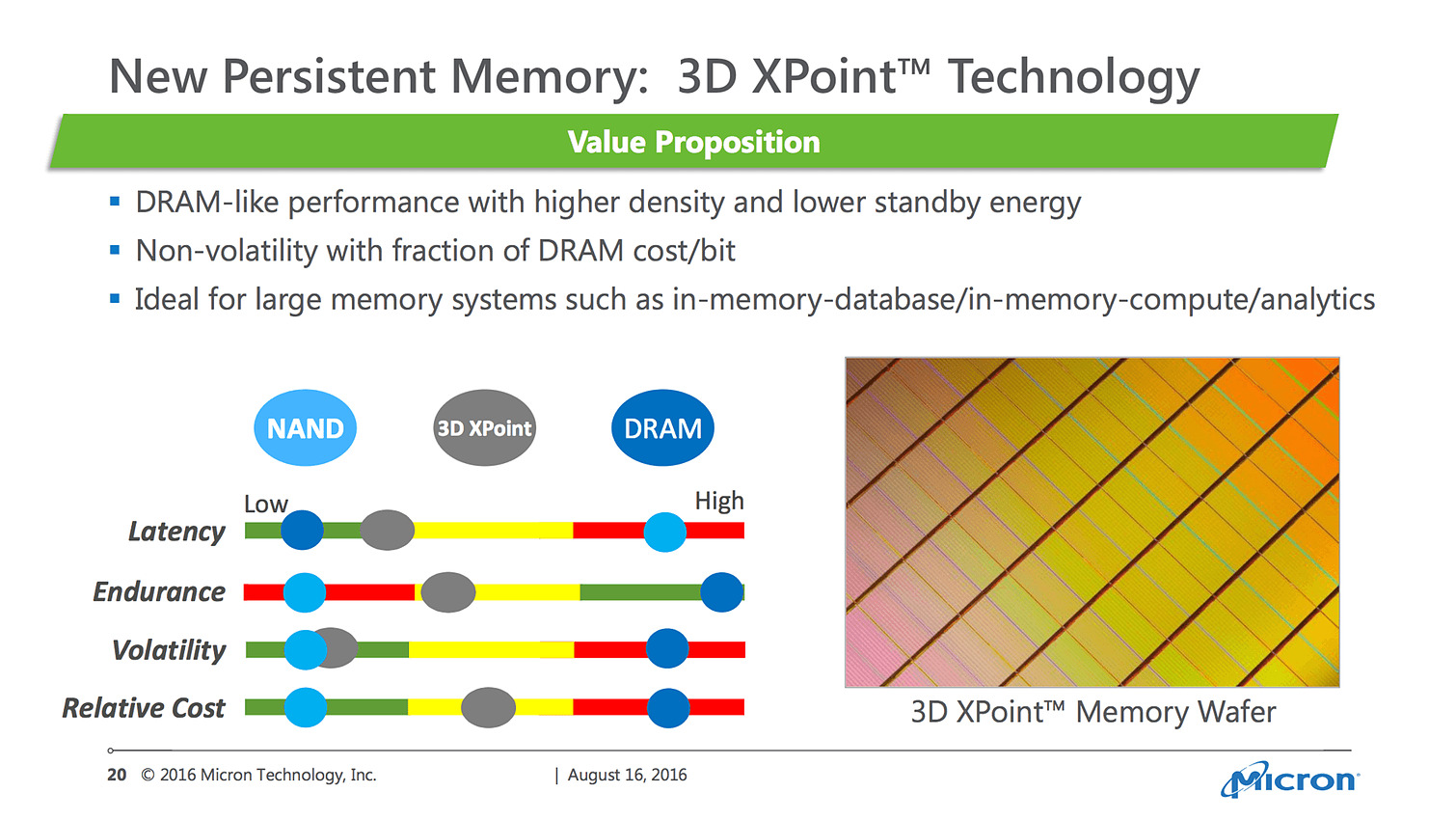

Outre le tacle envers son partenaire Intel sur la mémoire 3D XPoint, on ne retiendra pas beaucoup d'informations, si ce n'est que Micron confirme que ce nouveau type de mémoire sera en production avant la fin de l'année.

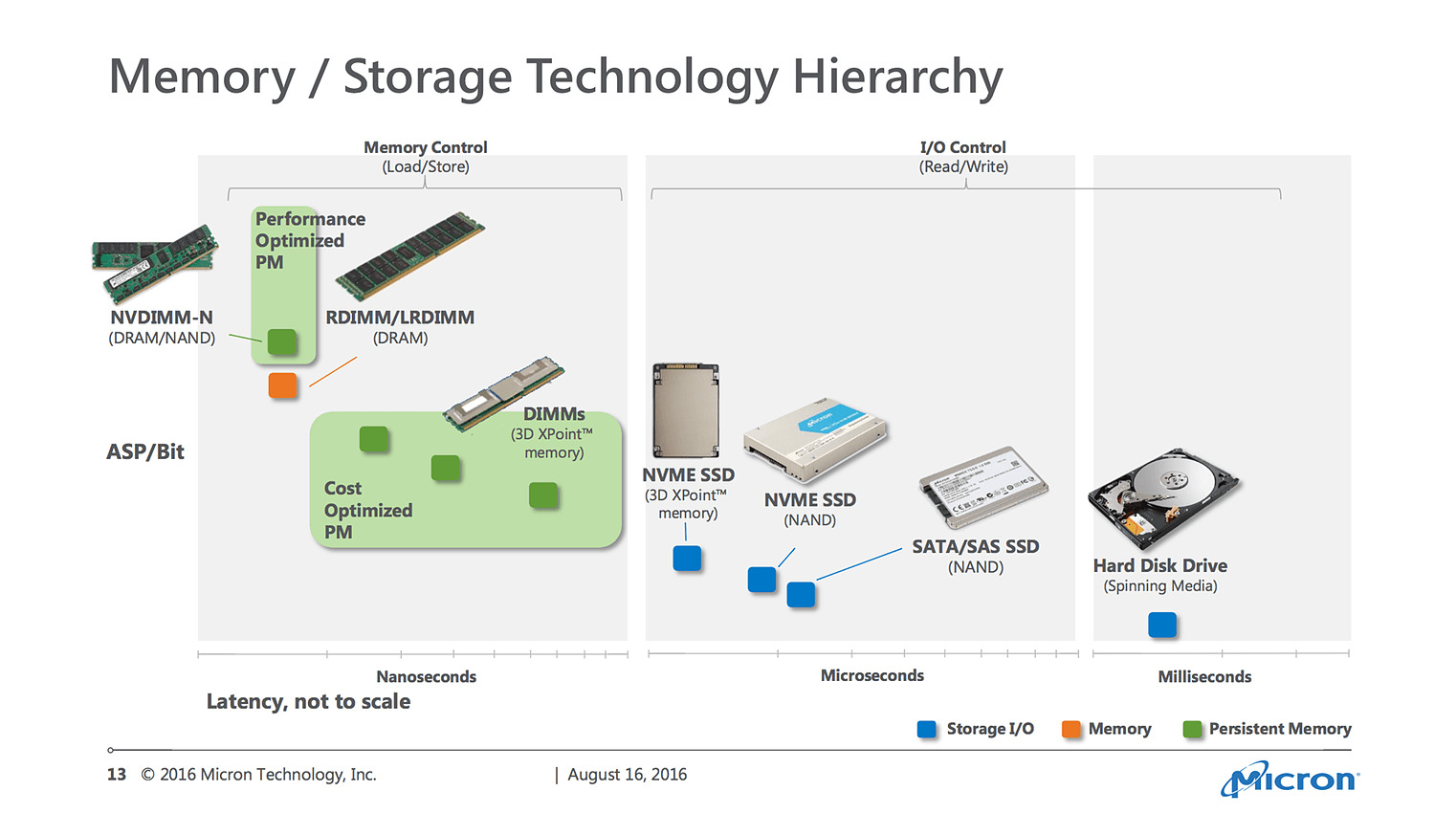

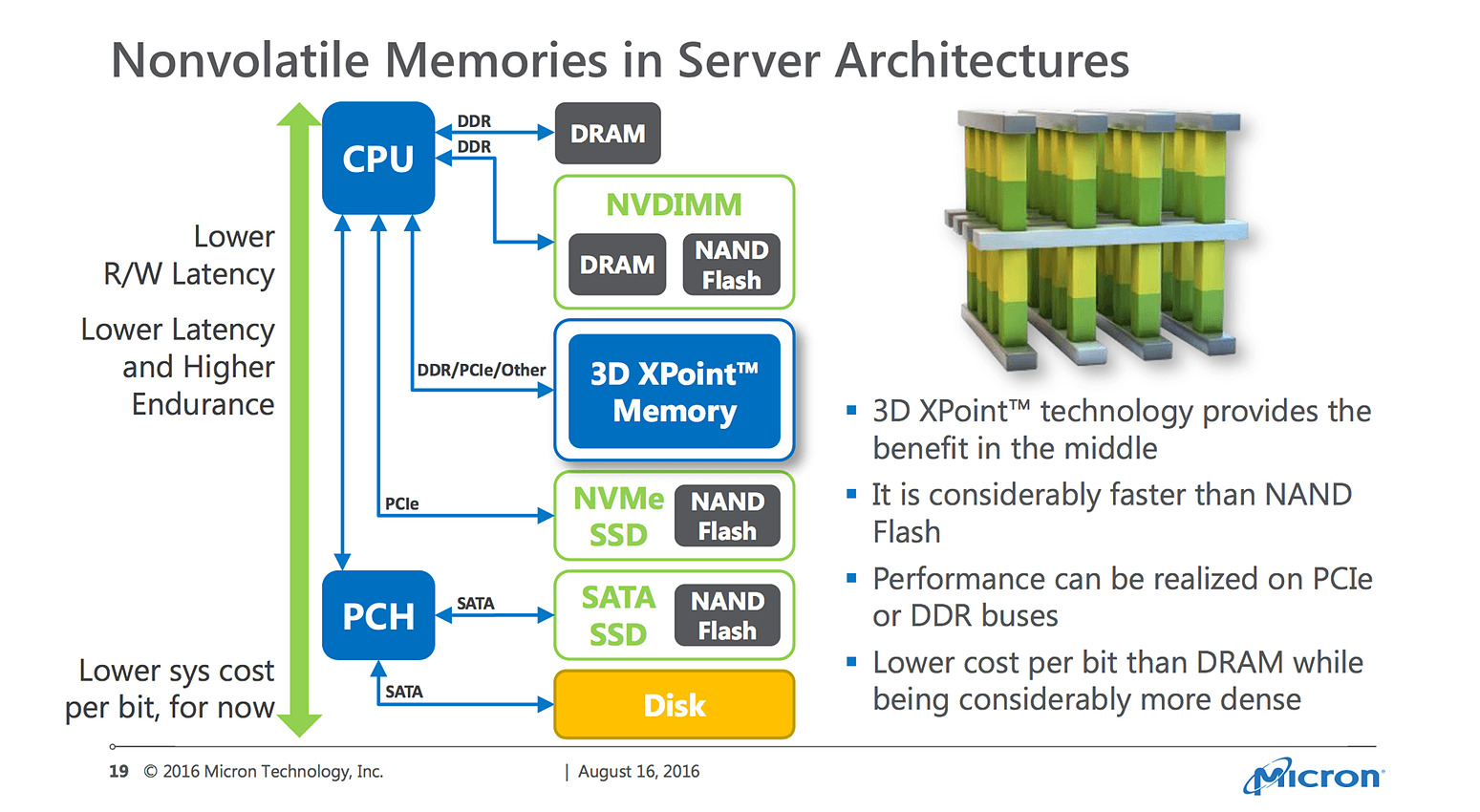

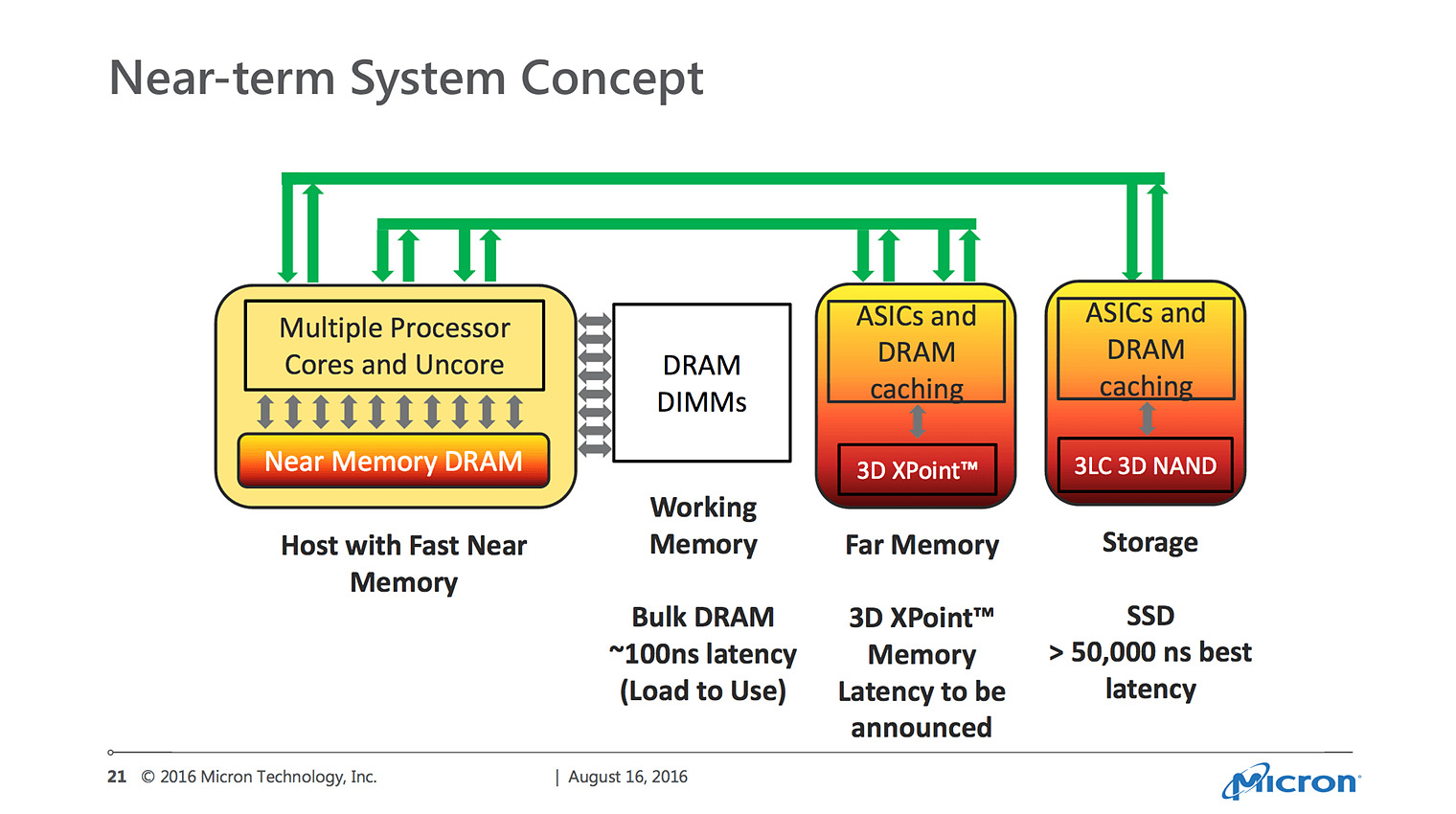

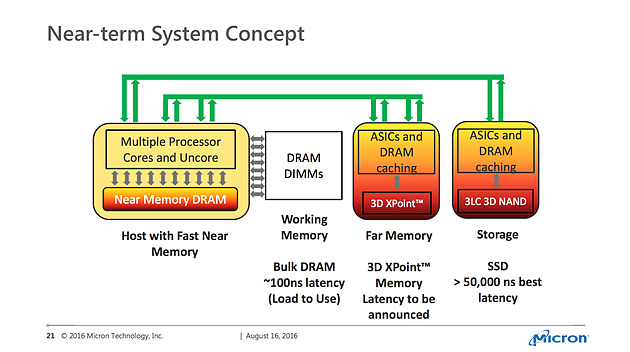

On retiendra ce dernier slide qui préfigure de ce que l'on devrait voir arriver sous peu sur les serveurs, avec deux tiers de mémoire DRAM. D'un côté une mémoire "proche", intégrée au processeur et rapide (HBM, ou plutôt HMC dans la vision de Micron) qui s'adjoint à la mémoire DRAM en barrettes plus classique. 3D XPoint et la 3D NAND proposant de leur côté deux tiers de stockages persistants.

Micron continue dans sa voie de l'originalité, dans un marché de la mémoire certes très concurrentiel. La société continue de mettre en avant sa GDDR5X, certes standardisée par le JEDEC mais qui n'a pas été adoptée par ses concurrents, mais aussi des solutions plus propriétaires comme l'Hybrid Memory Cube et 3D XPoint. Avec les ambitions de SK Hynix et de Samsung de pousser la HBM sur le terrain des PC clients, on peut cependant se demander si le pari d'ignorer la mémoire HBM ne se retournera pas contre Micron dans les mois à venir.

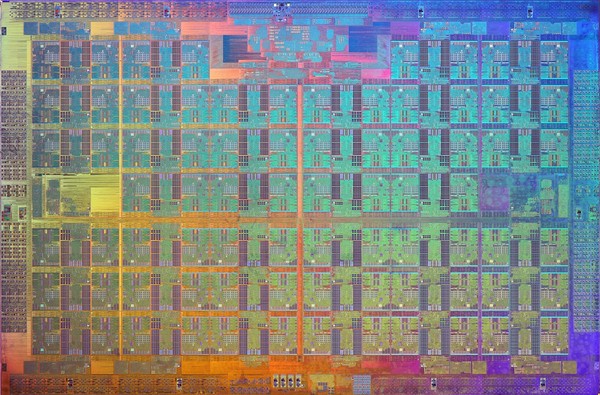

76 coeurs sur le die de Knights Landing

Intel a indiqué lors du forum SC15 dédié au HPC que des prototypes de ses Xeon Phi de génération Knights Landing fonctionnaient actuellement dans plusieurs super-ordinateurs. Cray en aurait installé dans les laboratoires de Los Alamos et du NERSC, Atos au CEA et Penguin Computing au sein du laboratoire Sandia. La date de lancement officielle n'est toutefois pas précisée, il était initialement question de mi-2015 et il y a donc un peu de retard.

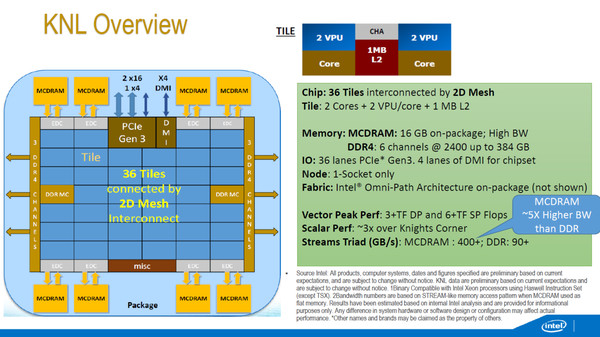

Pour rappel cette version de Xeon Phi dispose de 8 milliards de transistors gravés en 14nm et offrira jusqu'à 72 coeurs de type Silvermont associés par paire, partageant un cache L2 de 1 Mo et gérant chacun deux grosses unités vectorielles AVX-512. Jusqu'à 16 Go de mémoire à 400 Go /s (et non plus 500) seront intégrés sur le packaging, alors que cette version ne prendra plus la forme d'une carte fille mais d'un Socket : ce n'est plus un simple coprocesseur, il pourra être utilisé seul sur des machines.

Une image du die fournie par Intel montre qu'en fait ce sont 76 coeurs qui sont intégrés, le fondeur se gardant un peu de marge afin d'éviter d'avoir trop de rebut. Un wafer a également été montré, il permet d'estimer une taille qui s'approche des 700mm², soit près du double d'un Haswell-E 8 coeurs 22nm.

Intel annonce au passage Omni-Path Architecture (OPA), un nouveau lien à 100 Gbps pour relier les machines au sein d'un super-ordinateur. Des cartes filles PCIe ainsi que des switchs 24 ou 48 ports sont annoncés, sachant que certaines versions de Knights Landing intégreront directement un à deux contrôleurs OPA directement sur leur packaging.

Micron en charge de la mémoire des Knights Landing

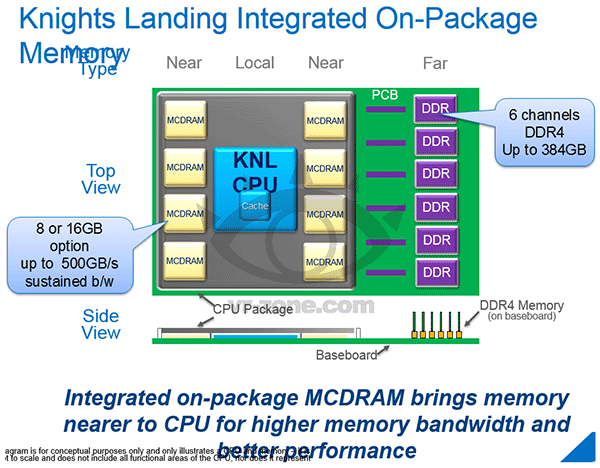

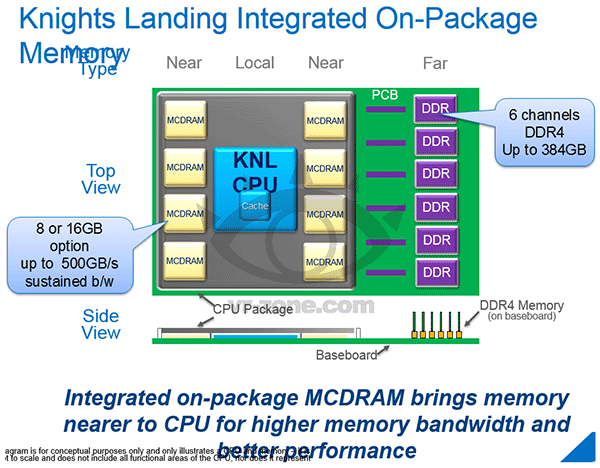

Nous vous en parlions en novembre dernier, la prochaine génération de Xeon Phi (Knights Landing) prévue pour la mi-2015 intégrera jusqu'à 16 Go de mémoire embarquée ultra-rapide délivrant une bande passante de l'ordre de 500 Go /s.

On apprend aujourd'hui que cette mémoire sera produite par Micron, qui l'a développée en collaboration avec Intel en prenant pour base l'Hybrid Memory Cube dont on parle depuis quelques années déjà. Les puces se trouveront sur le même packaging que les Xeon Phi, et seront reliées à ce dernier par une interface à très haute vitesse.

Dans son communiqué Micron indique que cette mémoire a une bande passante 5x supérieure à la DDR4 tout en prenant 50% de place en moins et avec un ratio bande passante/consommation multiplié par 3.

Pour rappel ces nouveaux Xeon Phi gravés en 14nm devraient gérer l'AVX-512, la DDR4, le PCIe Gen3 et seront disponibles en version Socket comme en carte fille PCIe. Un Xeon Phi pourra intégrer jusqu'à 72 curs de type Silvermont associés par paire, gérant chacun deux grosses unités vectorielles prenant en charge le traitement des instructions AVX-512 et partageant un cache L2 de 1 Mo. En sus de la mémoire embarquée, ils géreront six canaux de DDR4 permettant d'adresser 384 Go de mémoire supplémentaire.

Des détails sur les (monstrueux) Xeon Phi de 2015

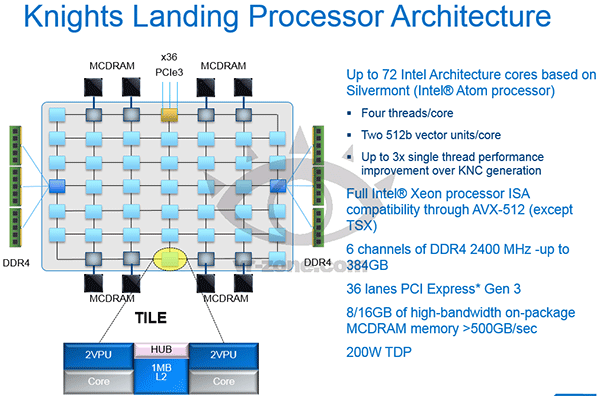

VR-Zone publie quelques slides intéressants sur la nouvelle génération de Xeon Phi nommée Knights Landing. On savait déjà que ces puces prévues pour mi-2015 seraient gravées en 14nm, géreraient l'AVX-512, la DDR4, le PCi Gen3 et seraient disponibles en version Socket comme sur des cartes PCI-Express. En termes de performances, Intel vise une puissance maximale triplée, de l'ordre de 3 Tflops en double précision, et une efficacité par watts également triplée.

On en sait maintenant plus sur les détails de la puce. Alors que Knight Corner intègre actuellement 64 curs x86 de type P54C (Pentium, à noter qu'au mieux 61 sont actifs sur les Xeon Phi 7100) disposant chacun de 512 Ko de cache L2 et pilotant une large unité de calcul vectorielle, sur Knights Landing ce sont désormais 72 curs de type Silvermont (la dernière architecture Atom lancée il y a peu, qui est cette fois out-of-order). Ils sont associés par paire, partagent un cache L2 de 1 Mo et gèrent chacun deux grosses unités vectorielles prenant en charge le traitement des instructions AVX-512.

Alors que les cartes Knights Corner gèrent au mieux 16 Go de GDDR5 offrant une bande passante de 352 Go /s, cette fois la mémoire sera composée de 8 à 16 Go de MCDRAM directement intégrée sur le packacing de la puce et offrant une bande passante pouvant atteindre 500 Go /s. Il faut y ajouter six canaux de DDR4-2400 permettant de gérer 384 Go supplémentaire avec une vitesse de 115,2 Go /s.

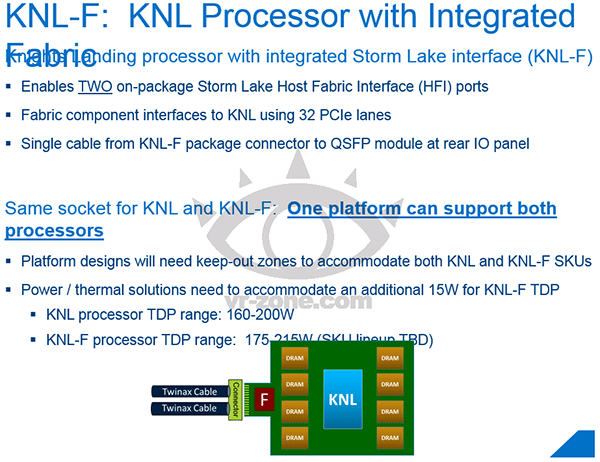

Enfin Intel y intégrera 36 lignes PCI Express Gen3, de quoi permettre d'éventuelles connexions entre plusieurs puces, ou avec des puces additionnelles. Un trimestre après le lancement des versions de base, une version "KNL-F" intégrant directement deux contrôleurs Fabric sur le packaging processeur verra le jour, elle permettra de disposer des liens optiques à haute vitesse et latence faible pour interconnecter les puces au sein d'un supercalculateur. Ces contrôleurs rajouteront 15W de consommation au TDP du package complet qui sera de 175 à 215W selon la version, contre 160 à 200W sans.

Contrairement à Knights Corner, Knights Landing sera utilisé sur Socket et il ne s'agira plus d'un simple co-processeur sur une carte fille, ce qui permettra de faire des serveurs utilisant seulement des Xeon Phi, de quoi augmenter notablement la densité pour les calculs massivement parallèles. Voilà un argument qui pourrait faire mouche dans ce secteur face aux offres Nvidia et AMD, sachant qu'une déclinaison sur carte fille de Knights Landing limitée à 2 canaux et 64 Go de DDR4 est également prévue pour fin 2015.