Les contenus liés au tag Intel

Afficher sous forme de : Titre | FluxRésultats Intel pour le second trimestre

Focus: Core i5-5675C : Broadwell côté CPU en test

Dossier: Celeron N3150 et Pentium N3700 : Braswell en test

Skylake K sans ventirad box, 130W requis ?

Cannonlake 10nm retardé à 2017, Kaby Lake pour 2016 ?

Dossier : Intel Core i7-6700K, i5-6600K et Z170 : Skylake en test

Skylake débarque au sein des i7-6700K et i5-6600K. Associés à un nouveau Socket LGA 1151 et un nouveau chipset Z170, ces processeurs vous inciterons-t-ils à changer de machine ?

[+] Lire la suite

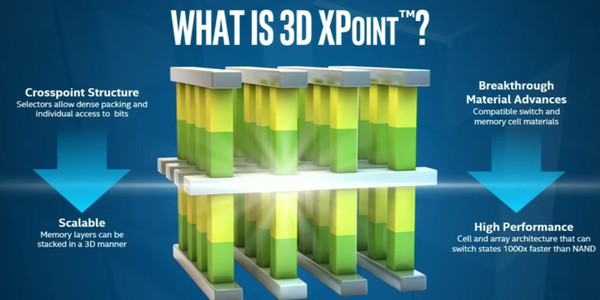

Intel et Micron annoncent la ReRAM 3D XPoint

Intel et Micron viennent d'annoncer conjointement une nouvelle technologie de mémoire baptisée « 3D XPoint » (à prononcer « 3D Crosspoint »). Les deux sociétés ont présenté cette technologie comme une nouvelle classe de mémoire, à mi-chemin entre la DRAM et la NAND. Il s'agit d'une technologie mémoire non volatile (comme la NAND) mais annoncée comme significativement plus rapide.

Les deux sociétés ont été relativement muettes sur les détails mais on peut tirer quelques informations des grandes lignes qui ont été révélées. Techniquement on peut considérer 3D XPoint comme une « variante » de la NAND dont elle modifie les deux éléments principaux, le switch et la cellule de stockage.

Au niveau de la cellule de stockage, et contrairement à de la NAND, on ne retrouve plus de transistor : les données ne sont plus stockées sous forme d'électrons mais en utilisant le changement de propriétés des matériaux utilisés pour créer les cellules (les blocs jaunes/verts sur le schéma). Le type de matériaux utilisés (deux, étant donné les deux couleurs ?) n'est malheureusement pas précisé et l'on n'aura pas eu plus de détails sur le fonctionnement exact durant la présentation, même si Intel a confirmé à nos confrères d'EETimes qu'il s'agissait bien de "changement de résistance", ce qui permet de classer 3D XPoint comme une variante de ReRAM. On sait que Micron s'intéresse à la ReRAM depuis un moment, par exemple avec cette recherche avec Sony, mais a l'époque le concept utilisé était différent, utilisant des transistors. D'un point de vue structurel, on semble s'approcher un peu plus de ce que proposait Crossbar, même si là encore l'absence de transistors est l'une des différences principale.

L'autre innovation se situe au niveau du switch qui permet de sélectionner les cellules auxquelles on souhaite accéder en faisant varier la tension, un mécanisme là aussi dénué de transistor. En pratique, exit le concept de blocs de la NAND, on peut lire et écrire les bits de données individuellement ! Qui plus est, il est possible de superposer ces structures switch/cellules en hauteur pour améliorer la densité.

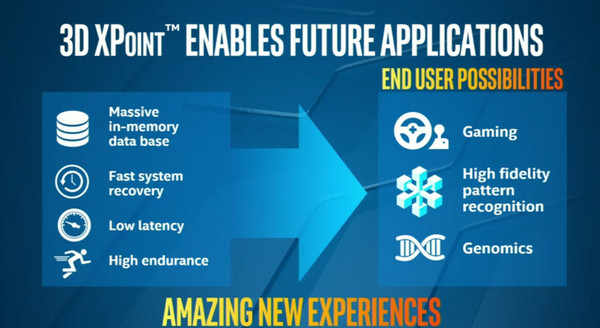

Les deux sociétés se félicitent de gros chiffres qui malheureusement ne sont pas expliqués, avançant des performances 1000x supérieures à la mémoire NAND, sans préciser de quelle NAND il s'agit, ou même tout simplement du type d'opération concerné ! On suppose, à la lecture de certains documents qu'Intel ne parle pas de débits mais de latence puisqu'il annonce que contrairement à la NAND dont la latence est mesurée en microsecondes, la latence de XPoint est mesurée en nanosecondes (une affirmation bien floue !) [MAJ : Un document dédié aux équipes marketing d'Intel - voir en commentaires - semble confirmer qu'il s'agit bien de la latence qui est utilisée pour le facteur de 1000x évoqué. Un facteur de 10x entre la latence XPoint et DRAM est également sous entendu. Le même document évoque, par rapport aux offres NVMe actuelles, un avantage de 10x sans plus de détails ce qui est déjà plus raisonnable]. On imagine en pratique que l'écart sera surtout le plus visible sur les écritures aléatoires - ce qui a été vaguement sous-entendu lors de la session de questions/réponses - ou l'écart avec la NAND parait le plus élevé d'un point de vue technique. La question de l'écart de performance sur les opérations de lectures a été écartée par les représentants des sociétés. On se félicitera tout de même (avec les mêmes réserves) du fait que l'endurance est annoncée comme 1000x supérieure à la NAND.

Par rapport à la mémoire DRAM, les sociétés ne qualifient cependant pas le niveau de performances, indiquant juste que la densité est 10 fois plus élevée.

Pour le reste les détails sont minces, aucune information sur le process de fabrication utilisé n'a été donnée par exemple (certains de nos confrères indiquent un process 20nm, mais nous n'avons pas pu confirmer l'information). Pour ce qui est de produits en pratiques, le premier sera une puce de 128 Gbit qui à l'intérieur superpose deux couches de cette nouvelle structure switch/cellule. Des échantillons de ces puces devraient être disponibles « cette année » tandis que côté produits finaux il faudra attendre 2016.

En pratique ces puces devraient pouvoir permettre de réaliser, côté grand public, des SSD PCI Express très rapides dans toutes les circonstances même si la question du prix a été éludée. Intel a cependant parlé de l'intérêt de cette mémoire pour le jeu en général, laissant penser qu'il y aura des applications grand public. Au-delà du stockage, c'est surtout côté serveur que cette mémoire devrait se présenter comme un tiers intermédiaire entre la DRAM classique et la NAND, autour des applications type « big data ». La manière dont ces produits se matérialiseront, ou s'interconnecteront, reste malgré tout floue. Intel et Micron proposeront chacun de leurs côté des produits issus de la technologie.

Sans plus de détails sur le cout de la technologie ou ses performances réelles il est difficile d'en tirer plus, d'autant que le représentant de Micron a indiqué que cette technologie ne remplacerait pas la NAND 3D en tant que produit (nous supposons que la NAND 3D gardera, au moins au début, un avantage de cout massif). Malgré tout, les innovations techniques semblent extrêmement intéressantes et pourraient remplacer à terme la NAND traditionnelle. Nous espérons qu'Intel dévoilera un peu plus de détails techniques lors son traditionnel Intel Developer Forum qui se tiendra cette année du 18 au 20 août.

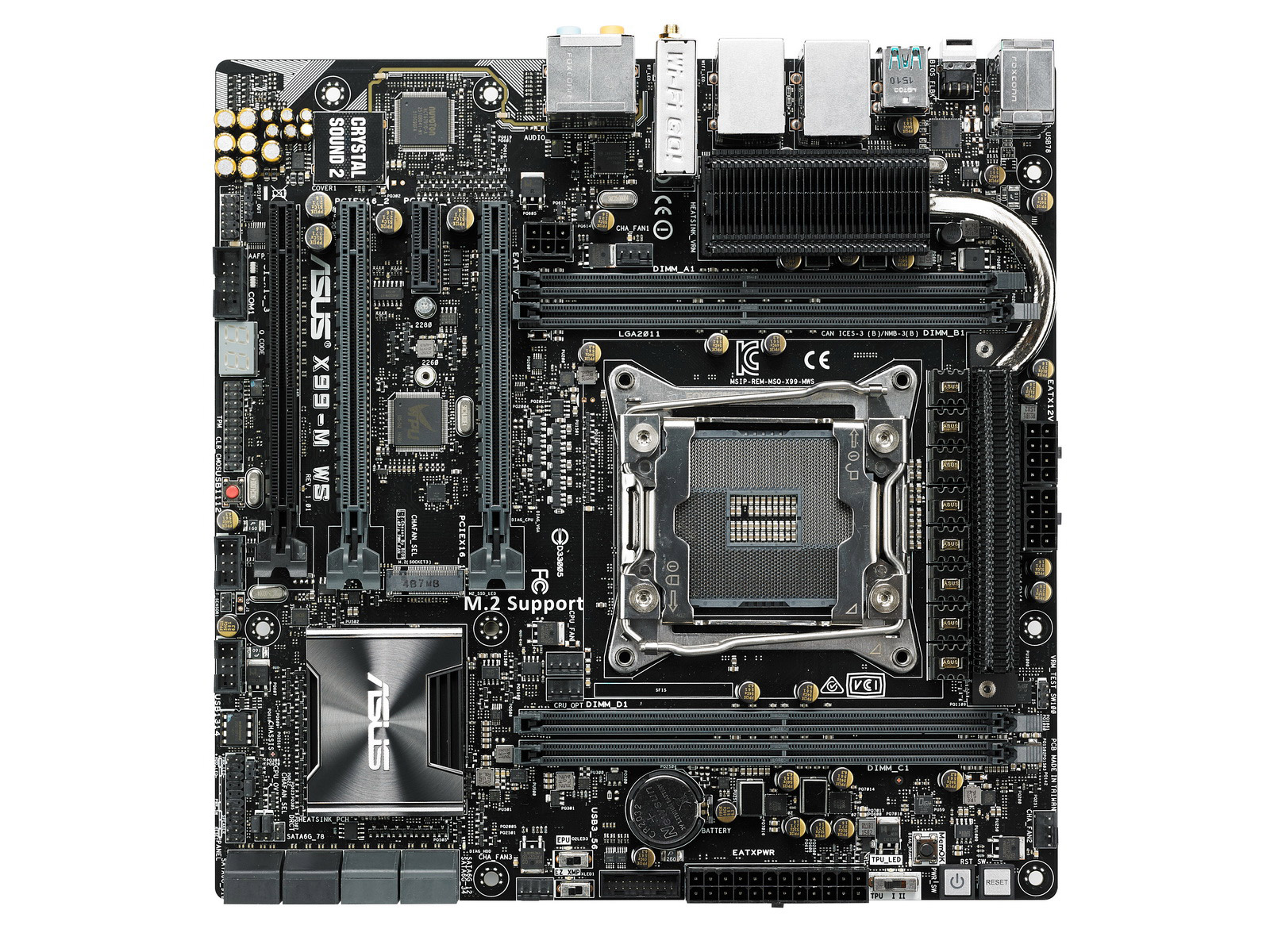

X99 en Micro-ATX chez Asus

Asus a mis en ligne sur son site les caractéristiques d'un nouveau modèle de cartes mères X99 dans sa gamme, la X99-M WS. Cette carte LGA2011-3 se distingue par son format Micro-ATX compact. Si Asus n'en proposait pas à ce format jusqu'ici, il faut noter qu'il existe encore plus petit, notamment chez Asrock qui propose un modèle Mini-ITX , mais avec de sérieuses concessions principalement sur les canaux mémoires supportés.

A l'inverse, on retrouve sur la carte d'Asus quatre slots mémoires DDR4 pour gérer entièrement les quatre canaux des processeurs. Côté PCI Express on a droit à trois slots x16 reliés au CPU (configurables en x16/x16/x8 avec un CPU 40 lignes) ainsi qu'un slot PCIe 2.0 x1 relié au chipset. Pour le stockage on a droit à huit ports SATA 6 Gbps (4 supportant le RAID) via le chipset ainsi qu'un slot M.2 (fonctionnant en mode SATA et PCIe).

Pour le réseau on retrouve deux contrôleurs Gigabit Ethernet Intel, ainsi qu'un module WiFi 802.11ac/Bluetooth 4.0. Côté son c'est un contrôleur Realtek ALC1150 qui officie avec l'option DTS Connect.

On notera sur l'USB la présence de 6 ports USB 3.0 et 6 ports 2.0 gérés par le chipset (respectivement 4 et 2 en façade arrière, le reste via des headers sur la carte) mais aussi deux ports USB 3.1 via un contrôleur Asmedia. Deux ports qui se présentent en façade arrière sous la forme de deux connecteurs Type-A traditionnels, et non au nouveau format Type-C.

Nous attendons plus d'informations sur le prix et la disponibilité de la part d'Asus France.

Les Skylake ''non K'' repoussés d'un mois

Alors que les Intel Core i7-6700K et Core i5-6600K, les premiers processeurs Skylake, ainsi que le chipset Z170 les accompagnants seront lancés et disponibles dès le 5 août prochain, les choses semblent se compliquer pour les 8 autres processeurs prévus qui ne seront pas overclockables mais moins chers.

Alors que les Intel Core i7-6700K et Core i5-6600K, les premiers processeurs Skylake, ainsi que le chipset Z170 les accompagnants seront lancés et disponibles dès le 5 août prochain, les choses semblent se compliquer pour les 8 autres processeurs prévus qui ne seront pas overclockables mais moins chers.

Plusieurs fabricants de cartes mères nous ont ainsi confirmé que les cartes H170 et B150 et le reste de la gamme ne seront pas lancés entre le 30 août et le 5 septembre comme c'était prévu mais environ un mois plus tard. Derrière ce décalage inédit de 2 mois entre les CPU K et les autres se cache probablement des stocks importants restant à écouler sur Haswell du fait d'un marché PC qui n'est pas au mieux de sa forme comme l'a rappelé Intel lors de l'annonce de ses derniers résultats.

Intel abandonne le Tick-Tock, confirme Kaby Lake

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

En marge de l'annonce de ses résultats financiers, la conférence dédiée aux analystes a été l'occasion pour Intel de confirmer ce dont l'on se doutait depuis un long moment : le 10nm du constructeur ne sera pas à l'heure.

Au milieu de l'annonce de nouveaux retards sur sa roadmap mobile (notamment SoFIA LTE qui est désormais attendu pour la première moitié de 2016), Brian Krzanich a indiqué que la transition d'un node à l'autre ne tenait plus réellement le rythme des 24 mois que le constructeur souhaitait s'imposer, mais que sur les deux générations précédentes, il était plus proche des deux années et demi. En conséquence, la stratégie du Tick-Tock doit s'adapter et il aura confirmé l'arrivée d'un troisième produit 14 nm, Kaby Lake qui sera lancé durant la seconde moitié de 2016 (comme on le pressentait le mois dernier) !

Le CEO d'Intel décrit Kaby Lake comme « bâti sur les fondations de la micro architecture Skylake », mais « avec des améliorations clefs de performances ». Un phrasé relativement vague qui laisse entendre qu'il s'agirait d'un peu plus que d'un « Skylake refresh », sans vraiment s'engager (possiblement un nouveau GPU seulement ?). Le lancement de Cannonlake est lui bel et bien repoussé à la seconde moitié de 2017, en 10nm.

Interrogé (légèrement) sur le sujet par les analystes, Brian Krzanich a qualifié le retard par la complexité croissante de mise au point des process et que les difficultés du 10nm, si elles étaient similaires en pratique à celles rencontrées pour le 14nm, n'étaient pas directement liées au retard du 14nm. Intel est sur le sujet dans une position délicate puisque le constructeur a toujours clamé que le retard du 14nm n'aurait aucun impact sur le 10nm. Selon le CEO, la lithographie continue à être de plus en plus complexe, notamment à cause de l'augmentation des étapes de multi-patterning. En marge de cela, il aura rappelé que le 10nm d'Intel sera une solution sans EUV (le reste de l'industrie ne s'attends pas non plus à disposer de l'EUV pour le 10nm).

Pour le CEO, rajouter Kaby Lake à la roadmap permet d'améliorer la « prévisibilité » pour ses partenaires. Un argument qui ne manque pas d'ironie quand l'on connait l'historique du Tick-Tock chez Intel. La stratégie du Tick-Tock avait été mise en place en interne chez Intel au début des années 2000 par Pat Gelsinger dans le but de mettre de l'ordre dans le développement parfois anarchique des architectures qui a conduit à de nombreux projets et architectures repoussés et abandonnés. En interne, il s'agissait de délimiter clairement le périmètre de deux équipes de développement d'architectures, une située en Oregon et l'autre en Israël. Le tout articulé autour des changements de process tous les deux ans.

Ainsi chaque nouveau passage à un process (65 vers 45 nm, etc) serait un Tick. Une version légèrement modifiée de l'architecture précédente, portée vers le nouveau node (ce que l'on appelle un die shrink), tandis que la « nouvelle architecture », le Tock serait lancé l'année suivante, lorsque le process de fabrication serait arrivé à maturité.

Historiquement, ce n'est qu'avec beaucoup de créativité que le constructeur aura pu compter 24 mois entre chaque node, des retards de plusieurs mois ayant été observés au fil des années mais globalement jusqu'ici Intel s'était imposé de tenir le modèle de deux produits principaux (on met de côté les produits/architecture dédiées spécifiquement à la mobilité) par node sur environ deux ans.

Avec le 14nm le modèle n'était plus tenable, obligeant en 2014 Intel à proposer un Haswell refresh, simple « speed bump » d'Haswell, lancé en juin 2013 en lieu et place de Broadwell. En pratique si Intel s'est targué d'avoir « lancé » le 14nm en 2014, il s'agissait d'un seul processeur, le Core M, qui plus est dans un stepping remplacé avant même sa sortie ! Et pour le desktop, la gamme Broadwell aura été réduite au minimum avec seulement deux modèles, lancés le mois dernier pour tenir les annonces. Avec au final un retard d'un an sur la cadence que s'imposait jusqu'ici Intel.

En pratique Skylake (le tock original 14nm) est toujours attendu pour cette année même si Intel n'a pas encore confirmé de quelle manière s'effectuerait son lancement. Il a été indiqué par Intel qu'une des conséquences du ralentissement de l'activité en Q2 était un inventaire encore important, laissant penser que le constructeur pourrait repousser certains SKU de Skylake. Le lancement des modèles K était prévu pour rappel pour le 5 aout, tandis que le reste de la gamme 4 curs était attendue entre le 30 aout et le 5 septembre. On ne s'étonnerait pas de voir ces références repoussées de plusieurs semaines afin d'écouler les inventaires existants, même si Intel ne l'a pas dit clairement.

On notera également qu'au détour d'une question, Brian Krzanich a confirmé que le 10nm d'Intel utiliserait toujours des FinFET, et non un autre type de structures comme certaines rumeurs avaient pu le laisser entendre. Il a indiqué que le 10nm serait la troisième génération de FinFET d'Intel. A une autre question il a indiqué que des changements de matériaux étaient par contre attendus sans les préciser.

Interrogé enfin sur l'impact de ces retards sur « l'avance » d'Intel en matière de process par rapport au reste de l'industrie, Brian Krzanich s'est voulu rassurant, indiquant que l'avance d'Intel ne diminuerait pas sur le reste de l'industrie. De notre point de vue, il est probable que TSMC, et possiblement Samsung lancent une production en volume autour, voir même un peu avant Intel. Ce qui serait, au moins pour l'image, un véritable drame pour la firme de Santa Clara.