Les contenus liés aux tags Intel et Xeon

Afficher sous forme de : Titre | FluxNouveaux Xeon D et Pentium D

Intel bloque les Xeon sur les chipsets classiques

Xeon Skylake pour 2017, 28 curs et 6 canaux

Les Xeon E7 v3 (Haswell-EX) débarquent

Intel Xeon D, SoC Broadwell 14nm et 2x10GbE

Xeon E3-1200 v6 : 3,9 GHz pour 73 W

Après avoir lancé ses Kaby Lake pour le grand public, Intel va également proposer des processeurs pour serveurs et stations de travail en LGA 1151.

Les Xeon E3-1200 v6 doivent être lancés durant le premier trimestre 2017, mais Intel n'a pour l'heure pas dévoilé leurs spécifications. MSI s'en est donc chargé.

Le constructeur de cartes mères a en effet publié sur son site les caractéristiques des futurs Xeon E3-1200 v6, avant de les retirer.

Au programme, huit processeurs sont prévus : trois dont la nomenclature se termine par un 5 et qui embarquent l'IGP Intel HD P630 (dont la fréquence de fonctionnement atteint 1 150 MHz), et cinq autres qui sont privés de cet IGP et dont la nomenclature s'achève par un 0.

Les Xeon E3-1220 v6 (3 GHz) et Xeon E3-1225 v6 (3,3 GHz) sont les deux seuls à être privés de l'HyperThreading. Les E3-1230 (3,5 GHz), E3-1240 (3,7 GHz), E3-1270 et E3-1275 (3,8 GHz), ainsi que le fleuron de la gamme, le E3-1280 (3,9 GHz), sont quant à eux équipés de quatre coeurs physiques et gèrent un total de huit threads.

Tous sont en revanche dotés de 8 Mo de cache de niveau 2 et fonctionnent avec une enveloppe thermique comprise entre 72 et 73 W, soit 7 à 8 W de moins que les Xeon de génération Skylake.

Les Xeon E7 v4 débarquent

Intel vient d'annoncer la 4è génération de Xeon E7 ayant pour nom de code Broadwell-EX. A l'instar des v2 et v3, soit les Ivy Bridge-EX et Haswell-EX, cette version utilise toujours la plate-forme Brickland. Si le Socket utilise 2011 points de contact, il est toutefois différent de celui utilisé pour les Xeon E5 v4 Broadwell-E.

Si les Xeon E5 v4 utilisent 3 die distincts, le Xeon E7 n'en utilise qu'un qui fait, comme la version HLC des E5, 456mm² pour 7,2 milliards de transistors. La gravure est en 14nm et dans la configuration maximale ce sont ainsi 24 coeurs et 60 Mo de cache LLC qui sont intégrés, contre 18 coeurs et 45 Mo pour Haswell-EX. On peut se demander si le die des Xeon E7 v4 et Xeon E5 v4 LLC n'est pas commun.

Côté fonctionnalités, Broadwell-EX ajoute principalement par rapport à Broadwell-E un 3è lien QPI nécessaire à des configurations 4 et 8 Sockets au lieu de 2. Chacun des deux contrôleurs mémoire ne gère pas directement la mémoire mais s'interconnecte à deux SMB (Scalable Memory Buffer) via une interface SMI (Scalable Memory Interconnect), ces SMB sont ensuite reliés à la mémoire qui peut être de type DDR4-1333/1600/1866 ou DDR3-1066/1333/1600. Au final chaque CPU peut gérer 1536 Go de mémoire à 102 Go /s sur 24 DIMM.

La version la plus haut de gamme, le Xeon E7-8890 v4, est affichée à 7175$. Il dispose de 24 coeurs fonctionnant à 2.2 GHz / 3.4 GHz en charge classique et 1.8 / 3.4 GHz en charge AVX, dans les deux cas le Turbo maximal sur les 24 coeurs est de 2.6 GHz, le tout pour un TDP de 165 watts. Le moins cher est le Xeon E7-4809 v4, il intègre 8 coeurs à 2 GHz pour un TDP de 115w et 1224$. Aucun mode Turbo n'est intégré et les liens QPI fonctionnent à 6.4 GT/s au lieu de 9.6 GT/s.

Xeon E5-2600 v4, 1ers pas pour Broadwell-EP

Intel vient de lancer les Xeon E5-2600 v4, nom de code Broadwell-EP. Comme leurs prédécesseurs v3, Haswell-EP, ils utilisent un Socket LGA2011-v3. La gravure passe au 14nm et Intel en profite pour gonfler le nombre de coeurs quelle que soit la version du die :

- LLC : 246mm² et 3,4 milliards de transistors pour 10 coeurs

- MLC : 306mm² et 4,7 milliards de transistors pour 15 coeurs

- HLC : 456mm² et 7,2 milliards de transistors pour 24 coeurs

[ 1 ] [ 2 ]

C'est la version LLC qui sera utilisée pour les futurs Core i7 LGA2011-v3. Le 14nm permet à Intel de baisser notablement la taille des die qui était respectivement de 354, 492 et 662mm² sur leurs prédécesseurs pour 8, 12 et 18 coeurs. Malgré une hausse de 22 à 30% du nombre de transistors et de 25 à 33% du nombre de coeurs on a donc une baisse de 30 à 38% de la surface des die.

La taille du LLC reste à 2,5 Mo par coeur, et on retrouve la même configuration sur les versions MLC et HLC que sur Haswell-EP avec deux groupes de coeurs distincts avec un ring bus et un contrôleur mémoire chacun, les deux ring bus étant interconnectés. Chaque contrôleur mémoire gère alors 2 canaux contre 4 pour la version LLC.

Avant de parler des nouveautés on notera que les instructions TSX, désactivées sur Haswell-EP suite à un bug, sont de retour. En termes de microarchitecture, Broadwell apporte des améliorations mineures qui devraient tout de même apporter un gain de performance de l'ordre de 5% à fréquence égale, mais les améliorations sur l'instruction PCLMULQDQ permet d'obtenir un gain de 20 à 25% en AES et de 90% pour CRC. Le support de la DDR4 passe pour sa part la 2133 à la 2400. Enfin Intel a intégré des améliorations dédiées à la virtualisation, comme la possibilité d'observer par thread/application ou VM l'utilisation du cache et de la bande passante mémoire et de pouvoir agir sur l'allocation du cache afin d'éviter une accaparation des ressources, mais aussi la possibilité d'envoyer les interruptions externe directement à la machine virtuelle sans passer par l'hyperviseur.

[ 1 ] [ 2 ] [ 3 ]

L'unité de contrôle de la puissance a également été revue afin de mieux gérer les charges composées d'instructions AVX et d'instruction scalaires. En effet sur ces processeurs la fréquence varie notablement selon le type de charge, ainsi un E5-2699 v4 (22 coeurs et 145W) a une fréquence de base de 1,8 GHz en charge AVX pour un Turbo maximal allant de 2,6 à 3,6 GHz selon le nombre de coeurs utilisés. Hors AVX la fréquence de base est de 2,2 GHz pour 2,8 à 3,6 GHz en Turbo. Sur Haswell-EP dès qu'un coeur exécutait des instructions AVX, tous les coeurs passait en mode "AVX" avec des fréquences réduites, alors que sur Broadwell-EP coeurs exécutants des instructions scalaires peuvent utiliser des fréquences supérieures.

Bonne nouvelle côté tarif ces Xeon E5-2600 v4 sont aux mêmes tarifs que les v3 à numérotation équivalente alors même qu'ils profitent d'un nombre de coeurs en hausse de 25 à 33%. Les fréquences de base et Turbo varient un peu, parfois à la hausse parfois à la baisse. L'entrée de gamme est constitué d'un E5-2603 v4 à 213$ pour 6 coeurs à 1,7 GHz et 85W alors qu'on peut grimper à 4115$ pour les l'E5-2699 v4 offrant 22 coeurs à 2,2-3,6 GHz (hors AVX) pour 145W. Il existe 3 versions 10 coeurs :

- E5-2630L v4, 10 coeurs à 1,8-2,9 GHz pour 55W, 612$

- E5-2630 v4, 10 coeurs à 2,2-3,1 GHz pour 85W, 667$

- E5-2640 v4, 10 coeurs à 2,4-3,4 GHz pour 90W, 939$

Les dernières rumeurs font pour rappel état d'un tarif qui serait de l'ordre de 1500$ pour l'i7-6950X qui a une fréquence de base de 3 GHz et un TDP de 140W. Son lancement devrait intervenir lors du Computex en juin.

Accélération SHA pour Cannonlake

Quelques petites informations et confirmations sont apparues ce week-end à propos de Cannonlake, la future architecture processeur d'Intel prévue pour la seconde moitié de 2017, et qui sera la première du constructeur à être produite dans un procédé de fabrication 10nm.

Quelques petites informations et confirmations sont apparues ce week-end à propos de Cannonlake, la future architecture processeur d'Intel prévue pour la seconde moitié de 2017, et qui sera la première du constructeur à être produite dans un procédé de fabrication 10nm.

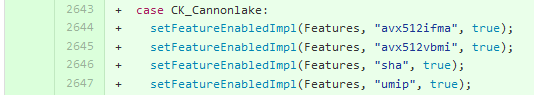

C'est par la publication d'un patch pour Clang, le compilateur C/C++/Obj-C de LLVM que l'on aura obtenu d'abord quelques confirmations sur le support d'AVX-512. Le patch en question que vous pouvez retrouver ici concerne l'énumération des fonctionnalités des familles de processeur. L'intérêt de ce code est de permettre aux développeurs, indépendamment de la machine qu'ils utilisent, de compiler des versions optimisées de leurs programmes pour une architecture donnée (par exemple, optimisée pour Skylake en ajoutant -march=skylake, plus de détails sur le sujet dans cet article).

Le patch, en développement depuis début février , indique le support spécifique de certains jeux d'instructions en fonction des familles. On retrouve ainsi les deux déclinaisons de Skylake, la version "client" (celle disponible pour les PC portables et de bureau) et la version "serveur" pour les Xeon. Cette dernière se différencie pour rappel par son support d'une partie du jeu d'instruction AVX-512.

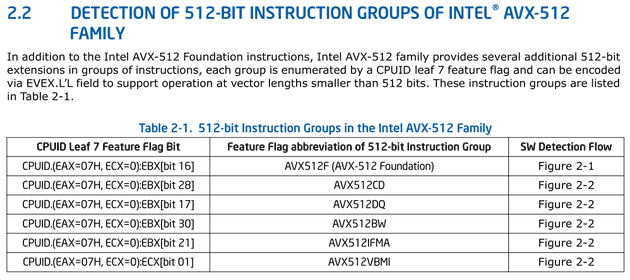

Pour ce patch, Intel ne spécifie qu'une seule version de Cannonlake et l'on retrouve, comme promis, le support des instructions AVX-512. De manière plus précise, en plus des instructions déjà supportées par la version Xeon de Skylake, deux autres extensions sont présentes, avx512ifma et avx512vbmi (une information que nous avions notée l'année dernière). L'extension avx512ifma concerne les instructions dites fused multiply add (par exemple A x B + C), appliquées cette fois ci à des nombres entiers (sur une précision de 52 bits). avx512vbmi rajoute des instructions de manipulation/permutations vectorielles d'octets (Vector Byte Manipulation Instructions).

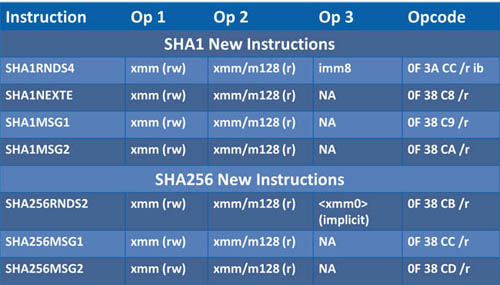

L'autre information est la confirmation de l'arrivée d'instructions dédiées aux calculs de hash cryptographiques. Les instructions sha font, sans trop de doute, référence à ces instructions présentées en 2013 par Intel , capables d'accélérer le calcul de hash aux formats SHA-1 et SHA-256 . Elles devraient être donc introduites pour la première fois sur Cannonlake.

On notera également dans le patch la mention d'une autre extension, umip pour laquelle nous n'avons pas encore trouvé de référence dans la documentation d'Intel !

Premiers Xeon + FPGA au prochain trimestre

En 2014, Intel avait annoncé sa volonté de combiner un Xeon et une puce programmable FPGA. Si on attendait ces produits pour les Xeon "Purley" en Skylake prévus pour 2017 d'après cette roadmap, le fabricant a précisé qu'il livrerait les premières puces Xeon + FPGA dès le premier trimestre 2016 à des fournisseurs de services cloud afin qu'ils optimisent leur algorithmes pour tirer parti du FPGA.

Pour rappel, Intel a annoncé en juin dernier le rachat du spécialiste des FPGA Altera avec lequel il avait déjà un partenariat pour l'utilisation de ses usines. Xilinx, autre spécialiste du FPGA, a pour sa part annoncé ces dernières semaines des collaborations avec Qualcomm et IBM afin d'associer des FPGA avec les architectures Power et ARM. Chacun affute donc ses armes pour ce qui semble être une des voies qui sera utilisée pour augmenter la puissance des centres de données dans les années qui viennent !

A noter qu'il ne s'agit pas d'une première pour Intel, qui avait déjà lancé en 2010 l'Atom E600C, qui combinait un Atom et un FPGA Altera (respectivement à droite et à gauche).