Les derniers contenus liés aux tags Intel et IDF 2015

IDF: Intel annonce Optane, SSD 5-8x + rapides

IDF: IDF 2015, c'est parti !

IDF: L'architecture GPU de Skylake

IDF: Alpine Ridge et Thunderbolt 3

IDF: L'USB Type-C en route pour l'universalité

IDF: Support de la mémoire DDR3 sur Skylake

IDF: L'architecture CPU Skylake en détails !

IDF: L'architecture GPU de Skylake

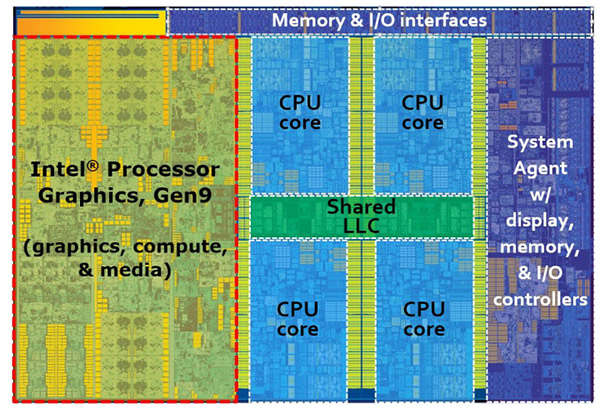

Lors de notre test de Skylake, nous avions pu publier quelques détails sur le fonctionnement de son architecture graphique. L'IDF a cependant été l'occasion d'obtenir quelques précisions supplémentaires que nous allons essayer de vous détailler. En pratique la grande majorité des modifications a surtout un impact sur la consommation, et non sur les performances comme l'ont montrés nos tests pratiques.

Architecture

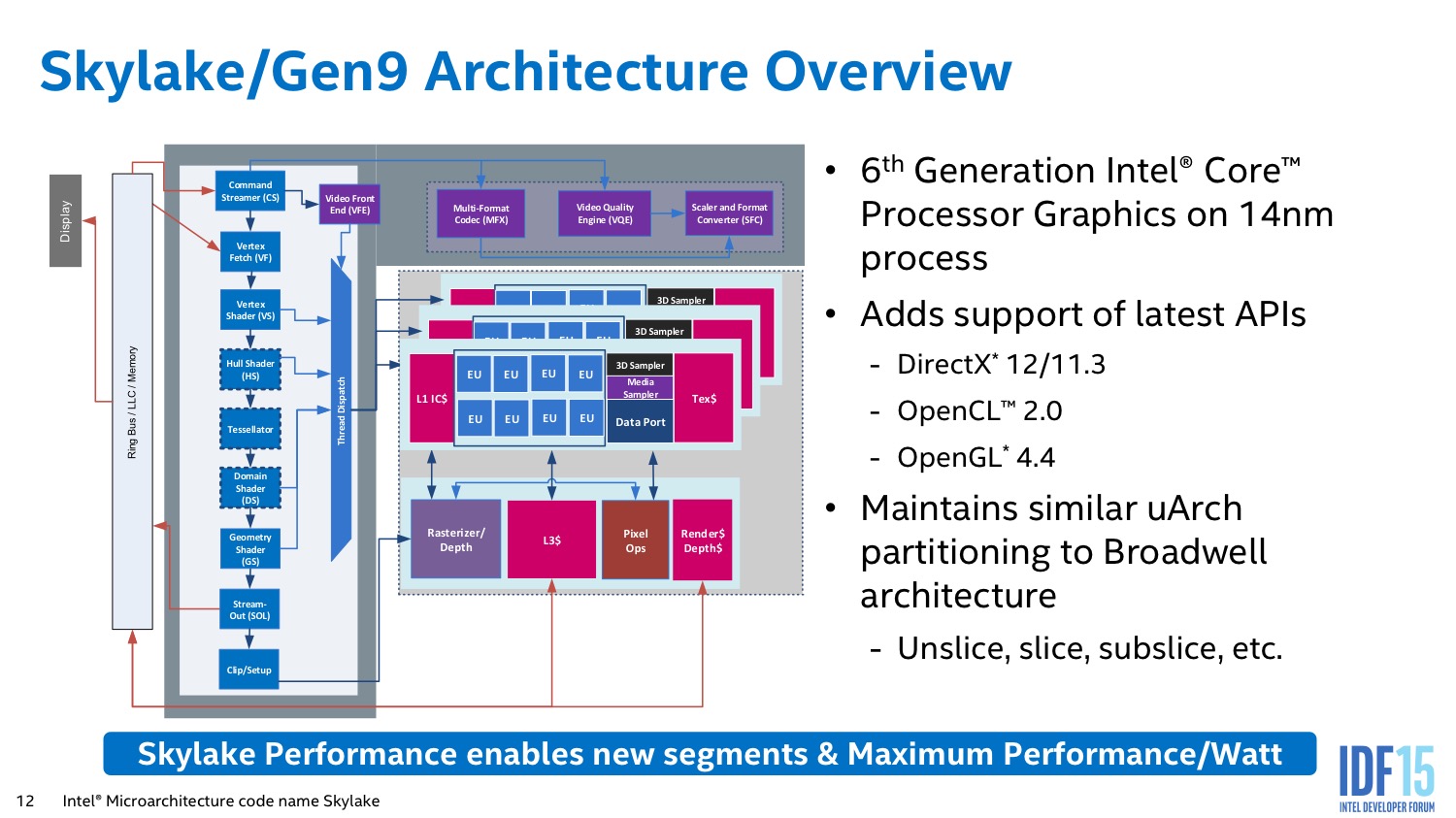

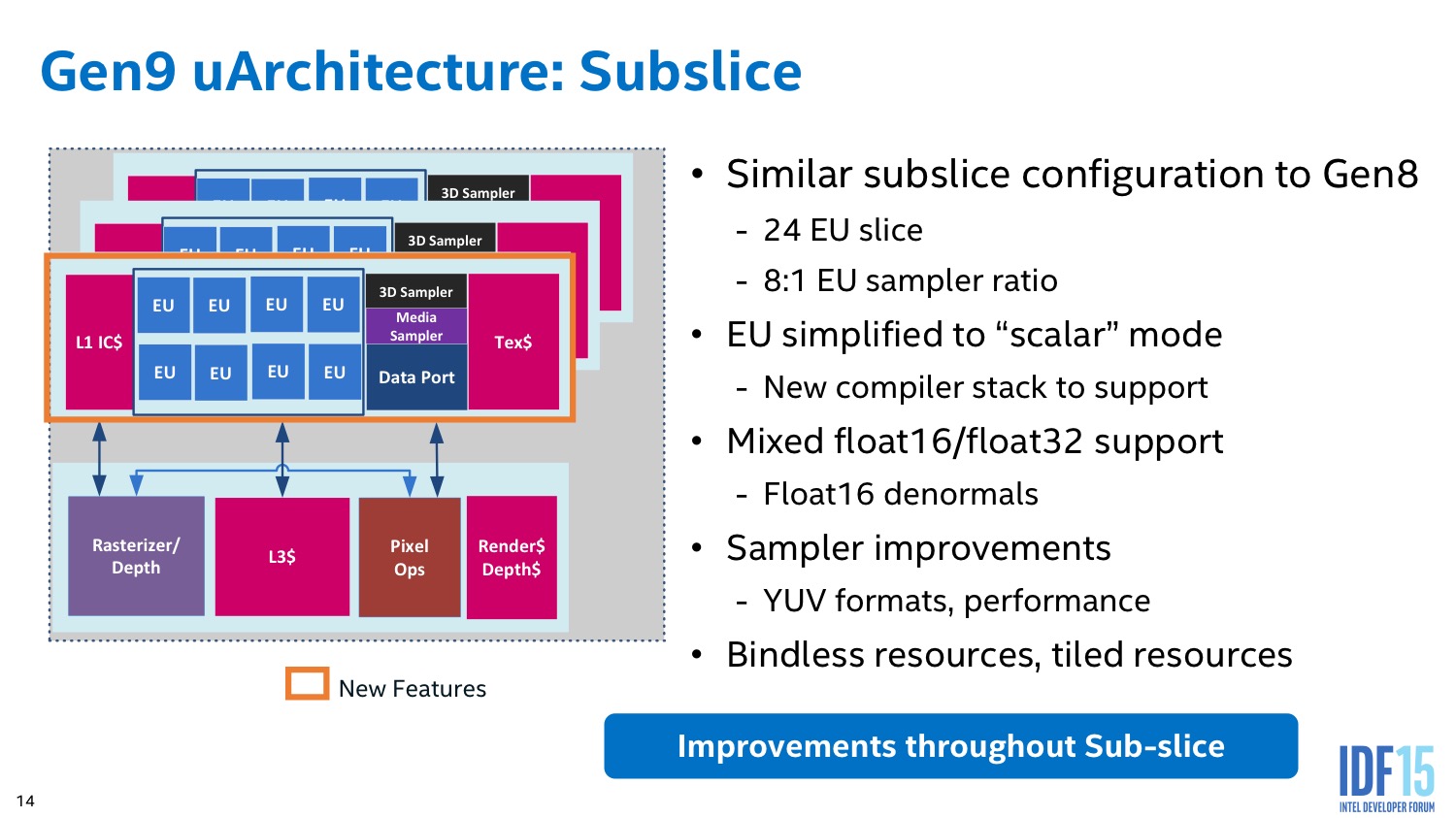

De haut niveau, la génération graphique 9 de Skylake est assez proche de celle de Broadwell. Comme nous l'indiquions à l'époque on retrouve les mêmes concepts de « slices » et d'EU. C'est à l'intérieur de ces unités que l'on retrouve les changements.

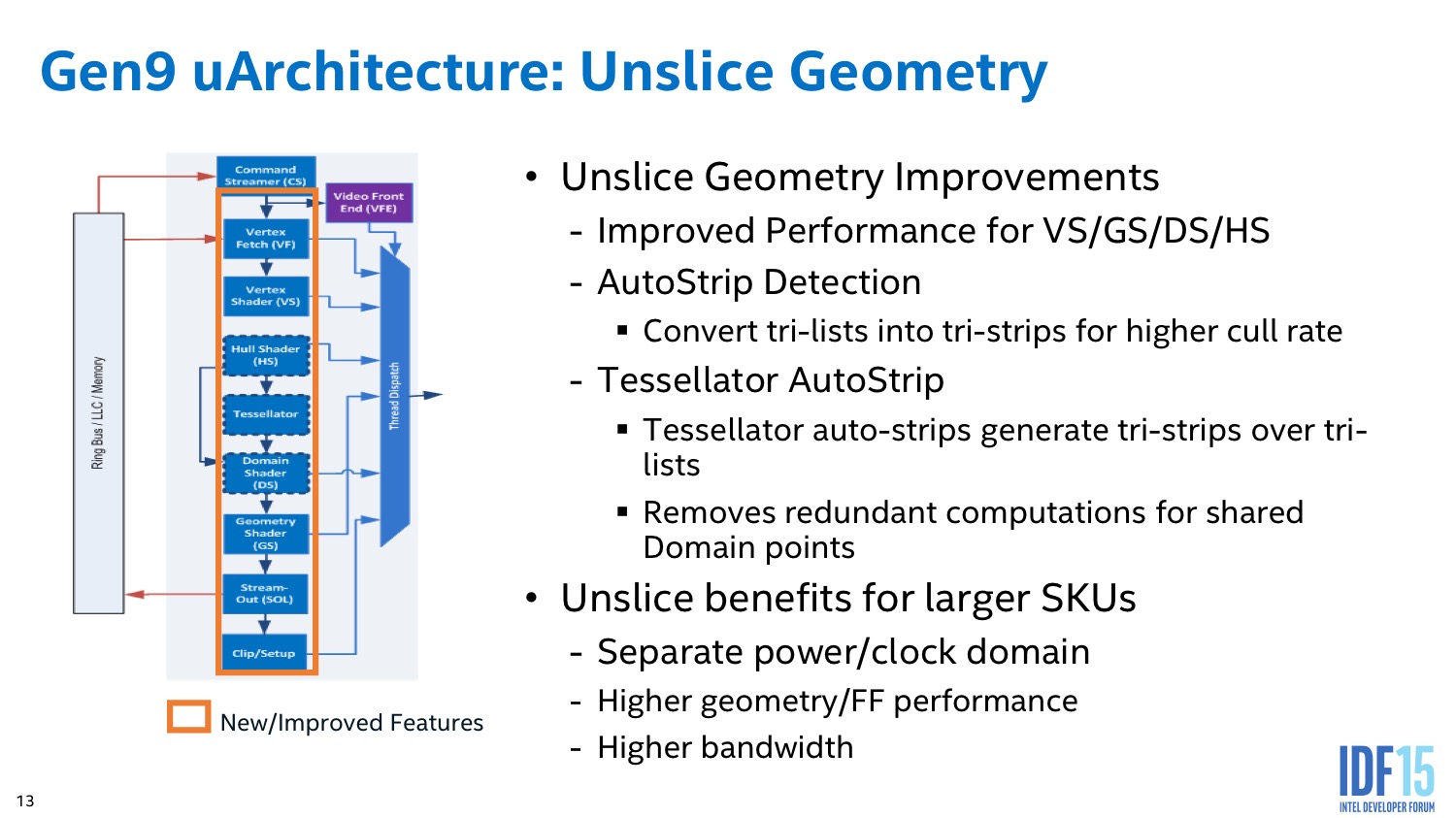

On notera au niveau de la gestion de la géométrie que toute la partie tessellation a été optimisée pour tenter de diminuer au maximum la génération de géométrie inutile (et donc améliorer les performances).

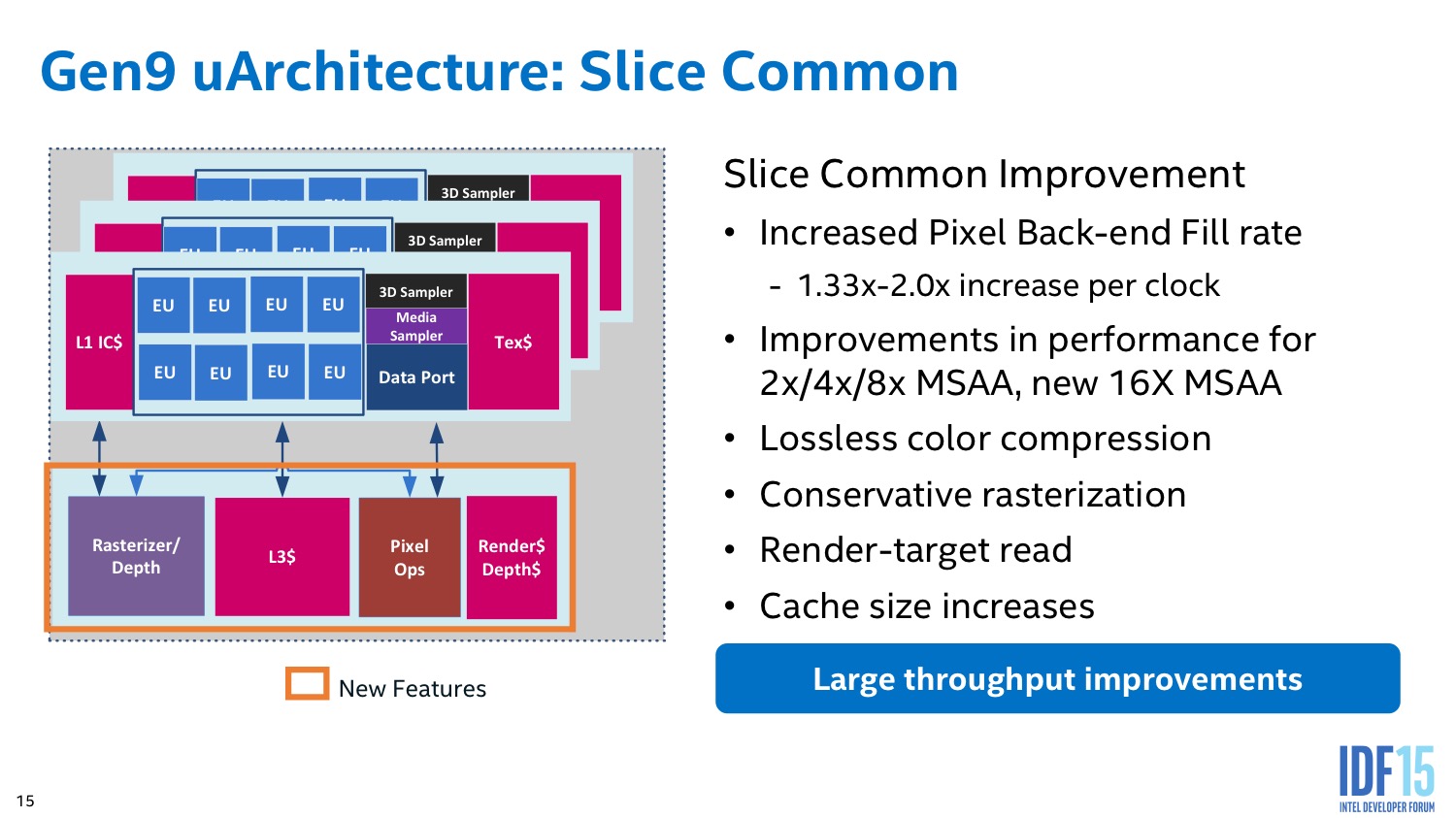

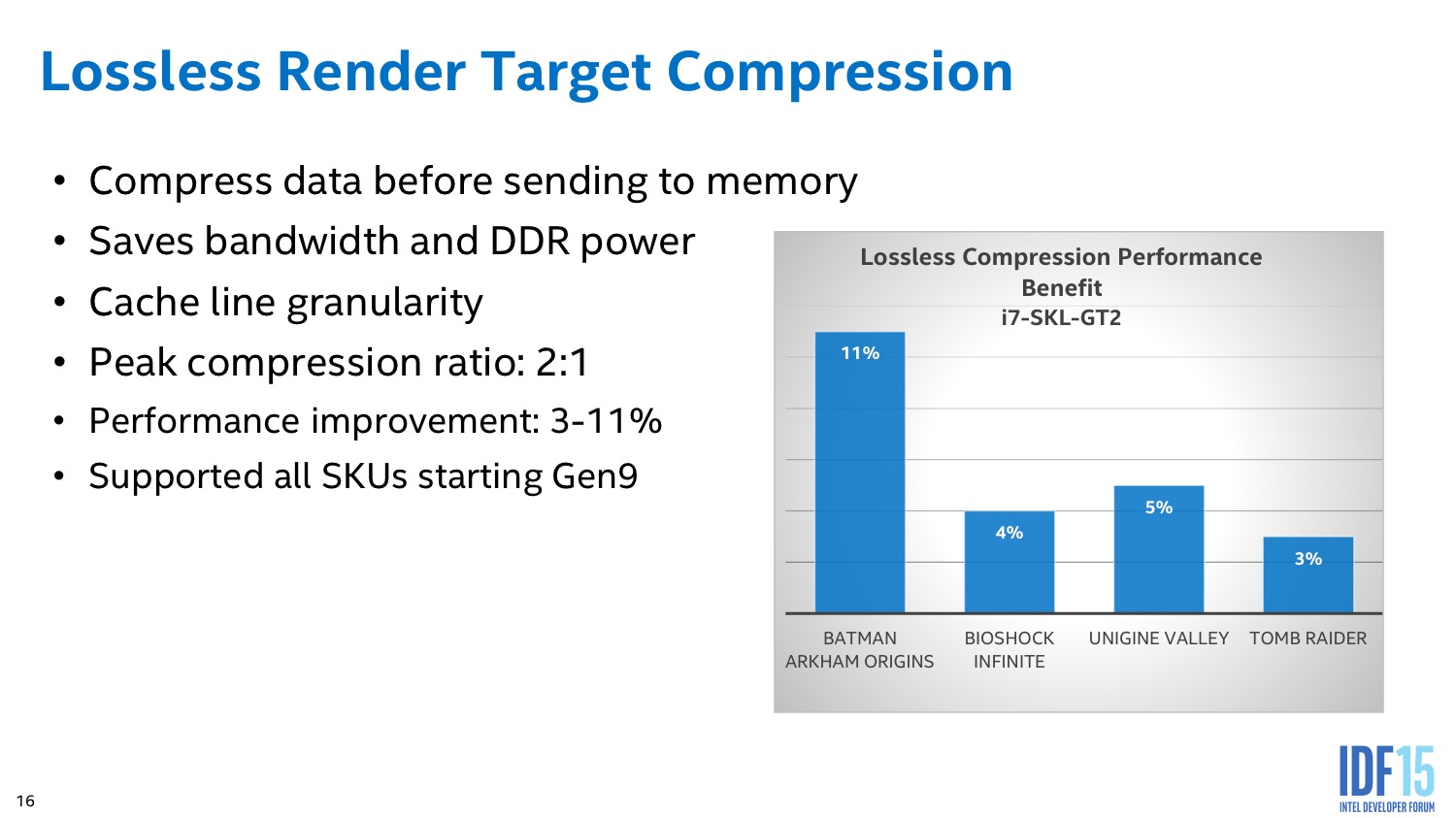

Au niveau du rasterizer on note quelques changements. Côté anti-aliasing un mode MSAA x16 apparait, tandis que les modes inférieurs gagnent en performance et l'on note l'augmentation de la taille du L3 graphique (qui passe de 512 Ko à 768 Ko). La compression ne se limite pas aux buffers de couleurs, mais s'applique également aux Render Target, une compression sans pertes est disponible (jusqu'a un ratio de 2:1) qui permet de réduire l'impact sur la mémoire et le cache. Un changement qui permet de réduire la consommation, et d'augmenter un petit peu les performances.

On notera enfin quelques petits changements qui visent plus précisément l'aspect « compute » avec une amélioration des performance de la gestion de la cohérence du cache et de nouvelles instructions atomiques (pour un élément, a l'inverse des instructions vectorielles qui s'appliquent a plusieurs éléments à la fois).

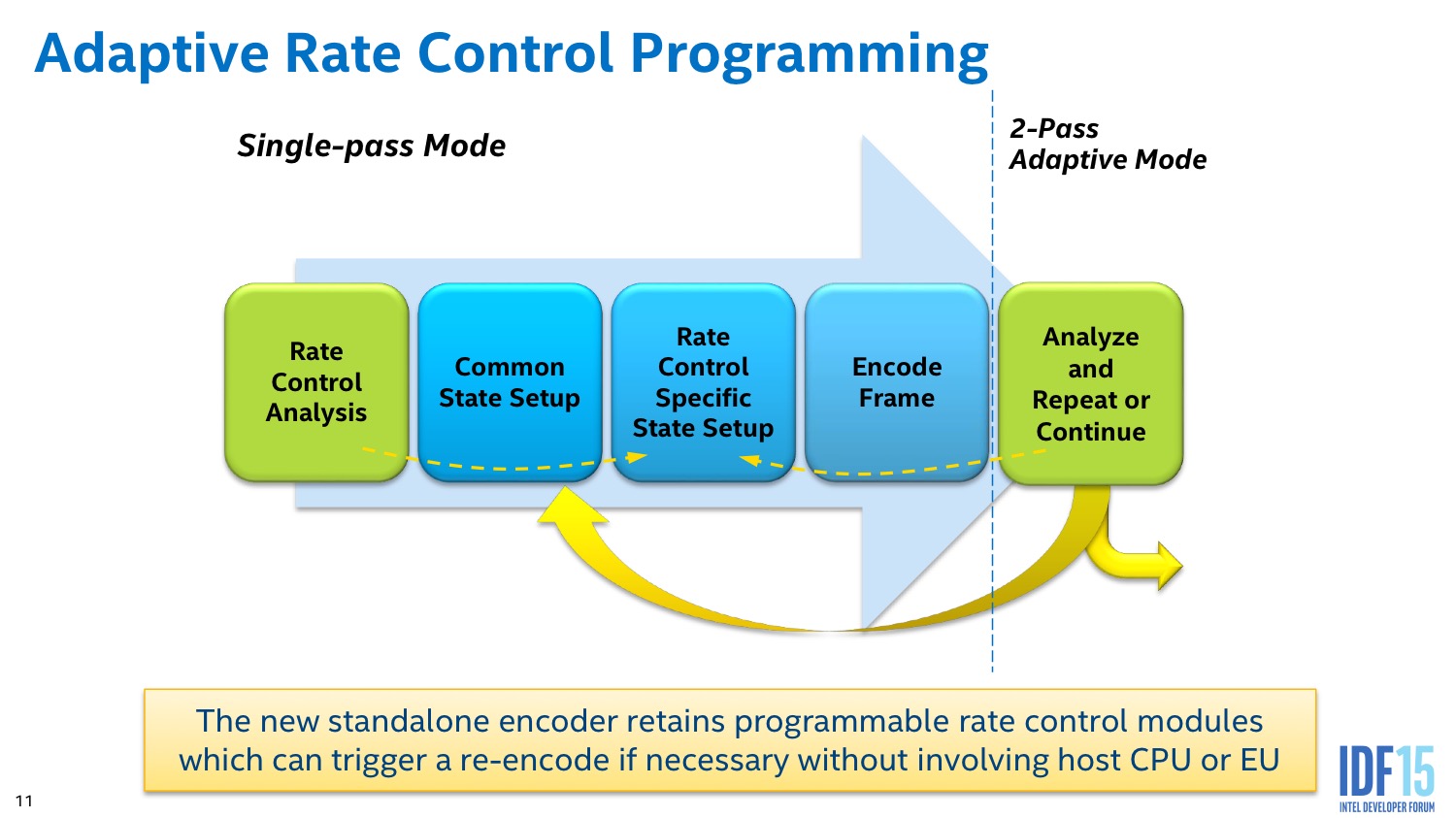

QuickSync et media

Nous avions dans notre test noté le saut de qualité offert par QuickSync en ce qui concerne l'encodage vidéo H.264. La raison principale de ce changement semble être l'ajout d'une gestion de l'adaptative rate control pour relancer l'encodage de frames jugées comme mal encodées après coup. Au delà de l'amélioration de qualité, nous avons noté que sur les transitions de scènes (hors I-Frame), Broadwell et Skylake se distinguent largement des architectures Intel précédentes, ce qui peut être lié à ce changement.

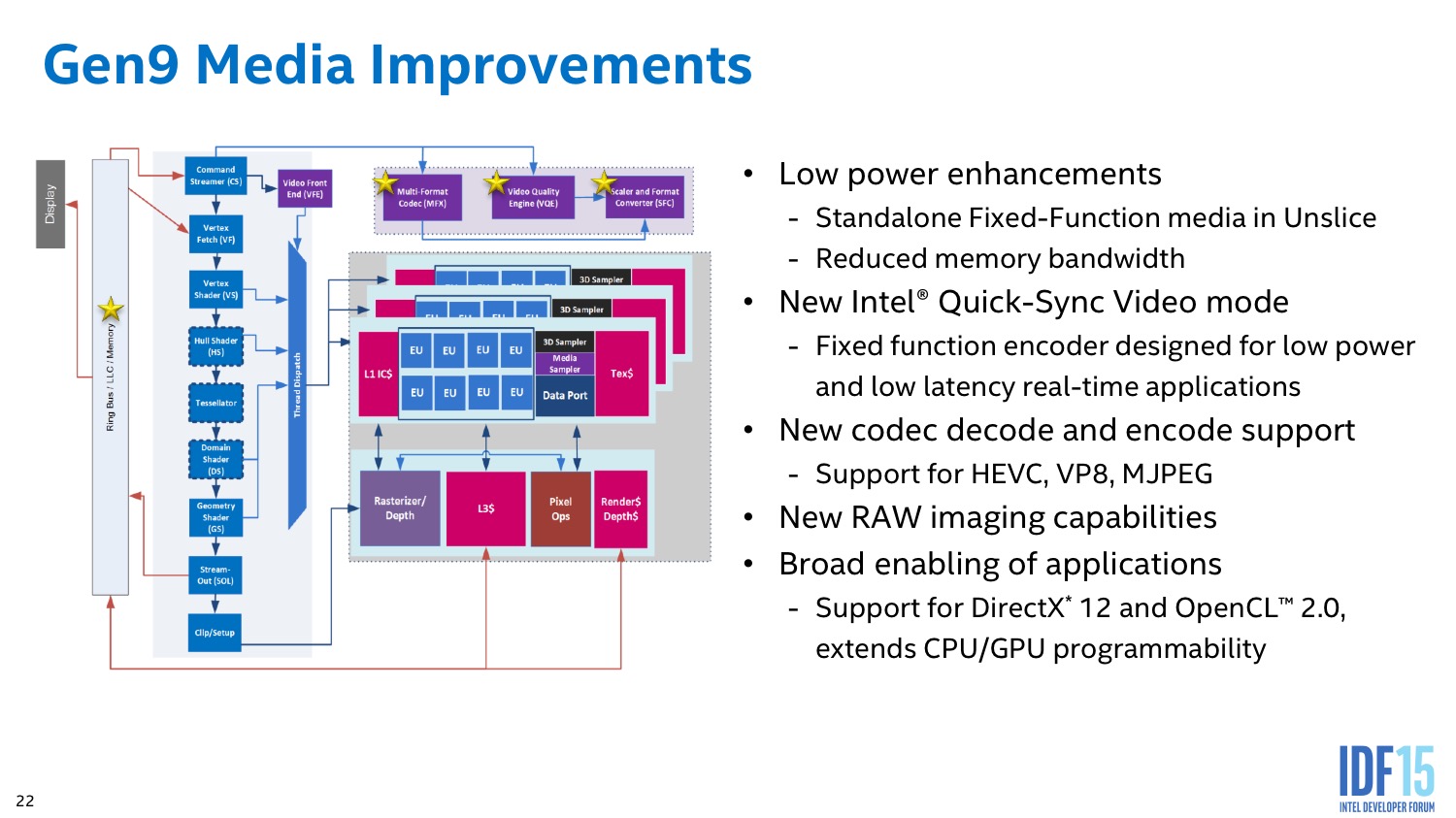

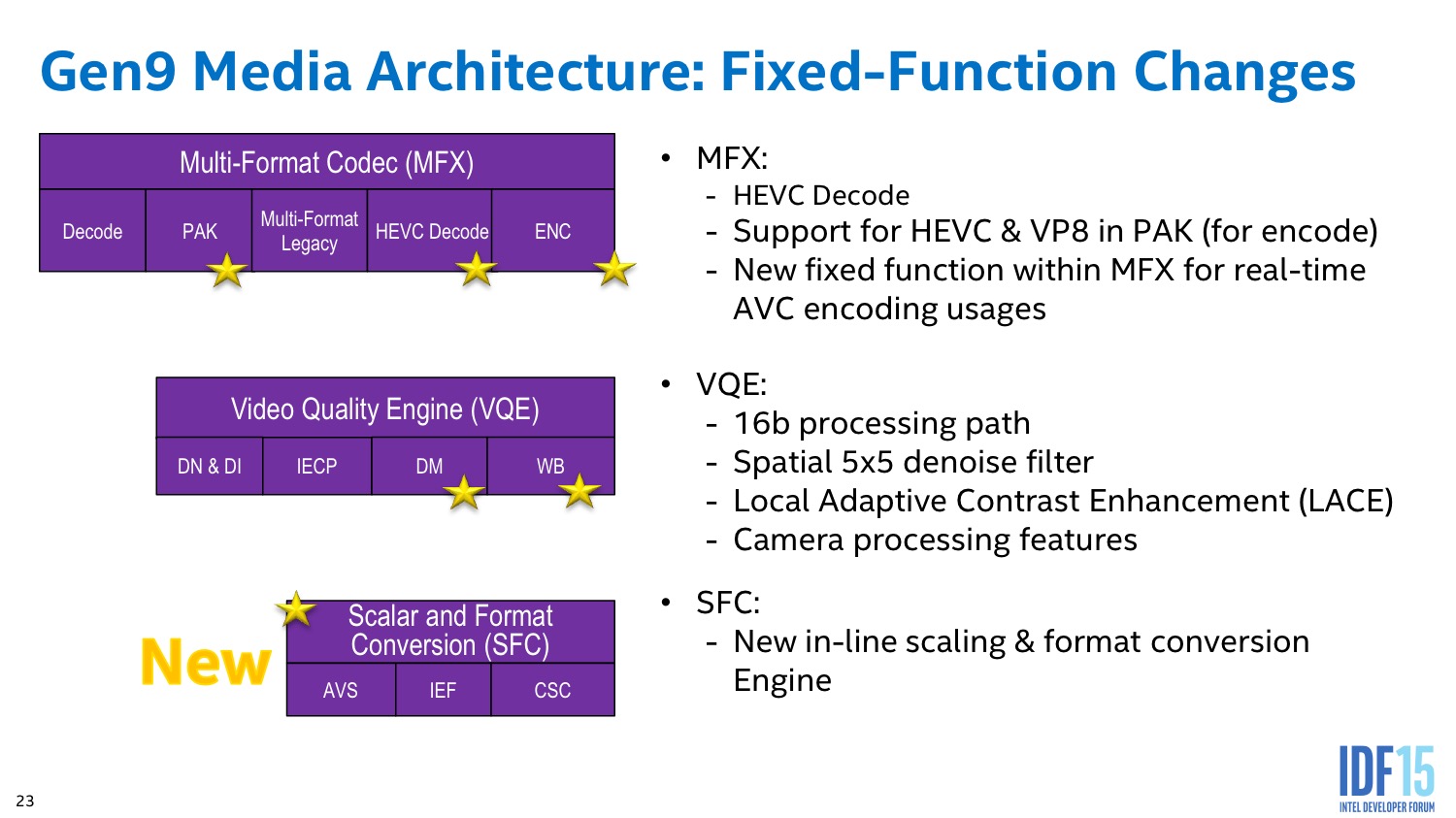

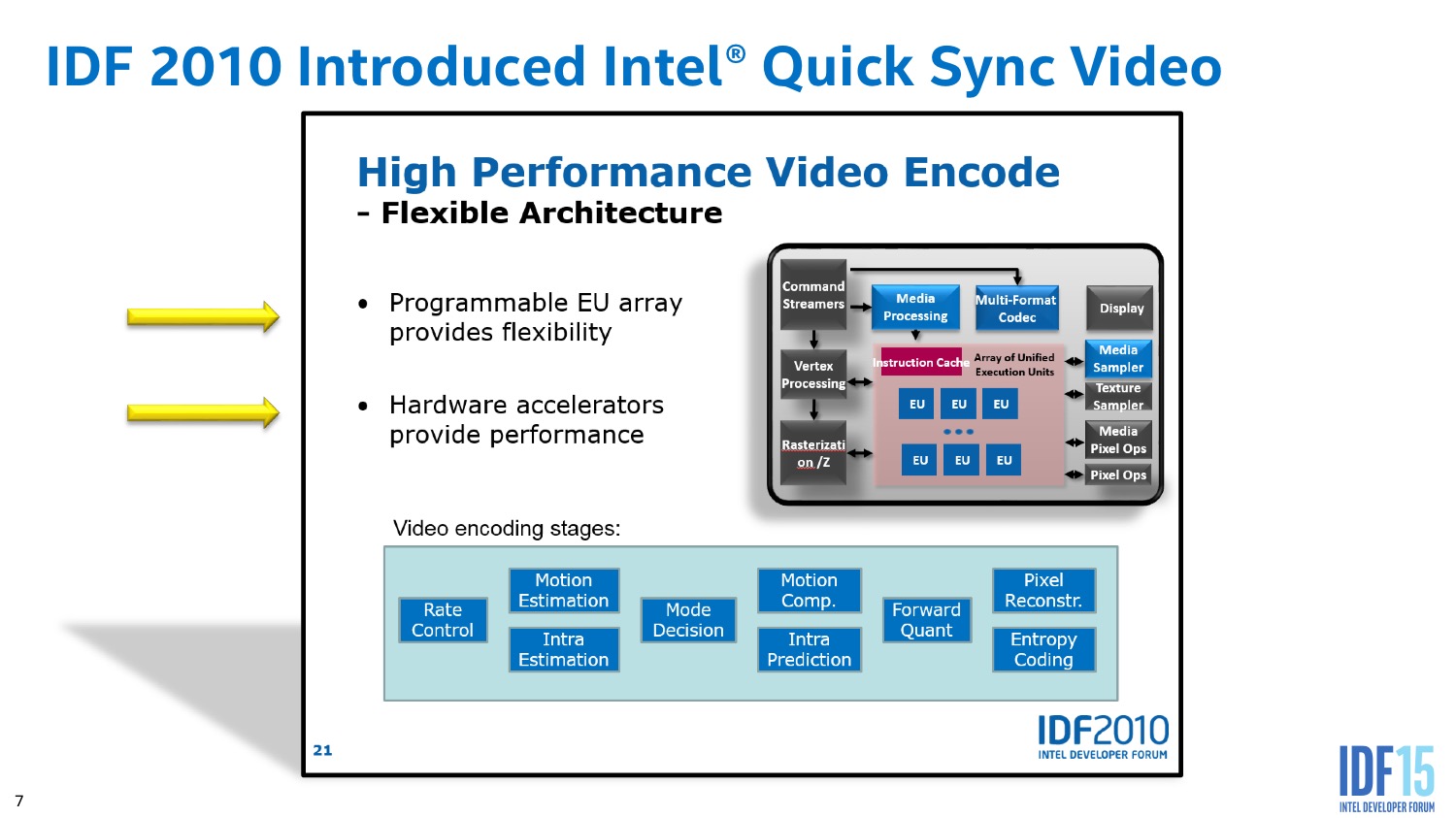

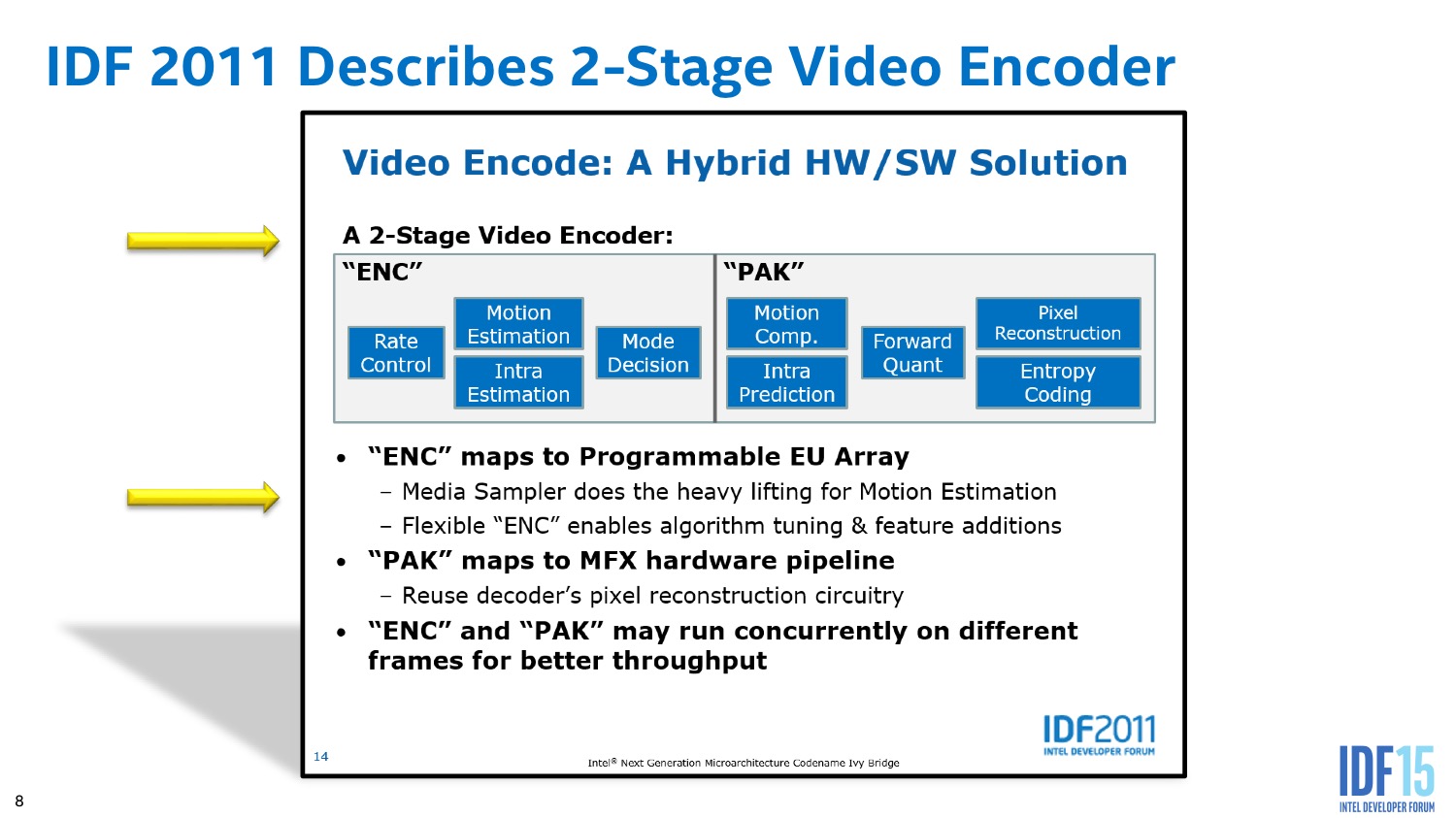

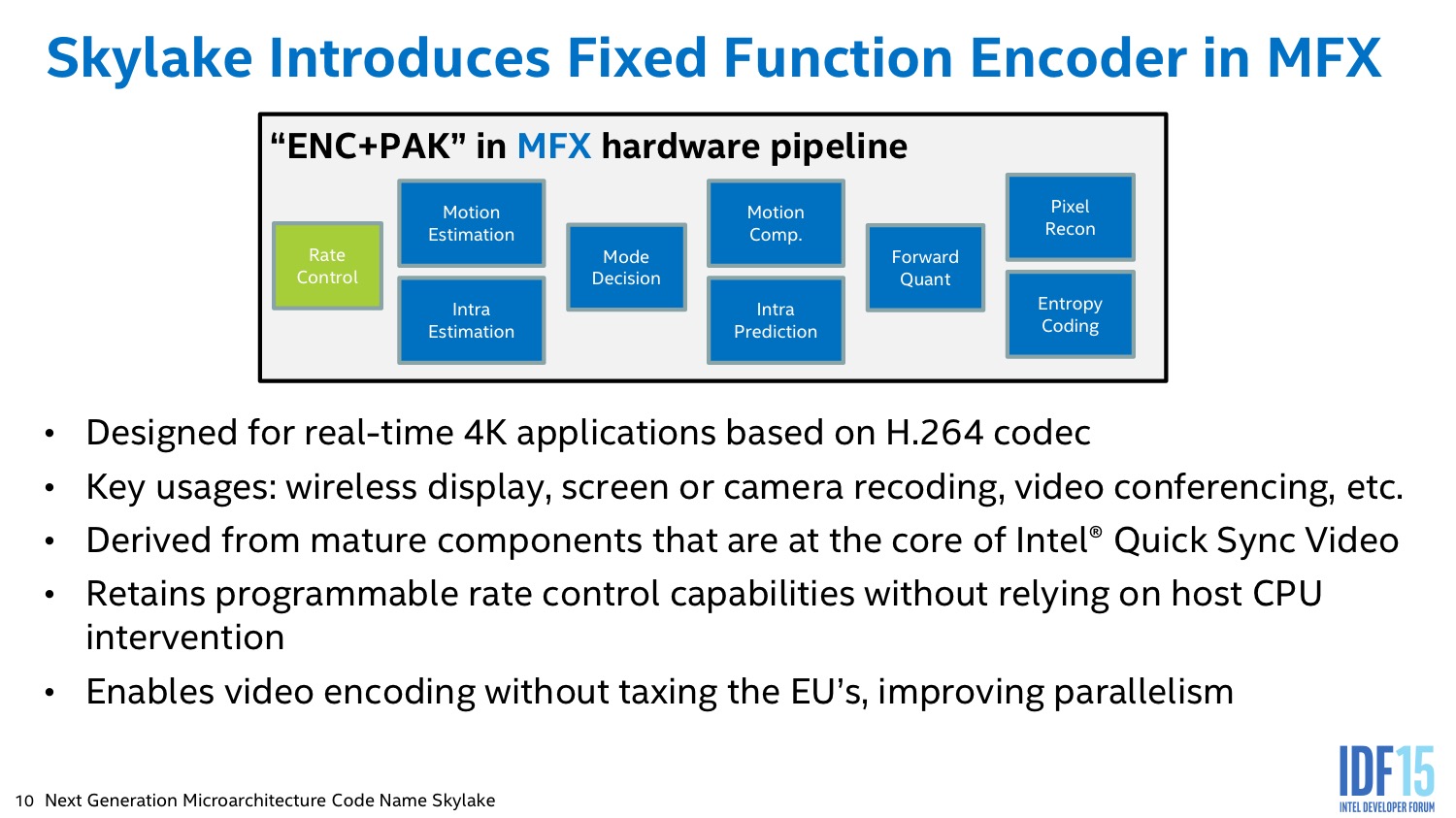

Cette amélioration nette de la qualité d'encodage n'est cependant pas le seul changement apporté. En pratique le GPU de Skylake inclut trois blocs pour ces traitements, un dédiée à l'encodage/décodage (MFX), un aux traitements vidéos (VQE), et un nouveau bloc pour les conversions de formats vidéo (changement d'espaces de couleur) et de scaling (SFC).

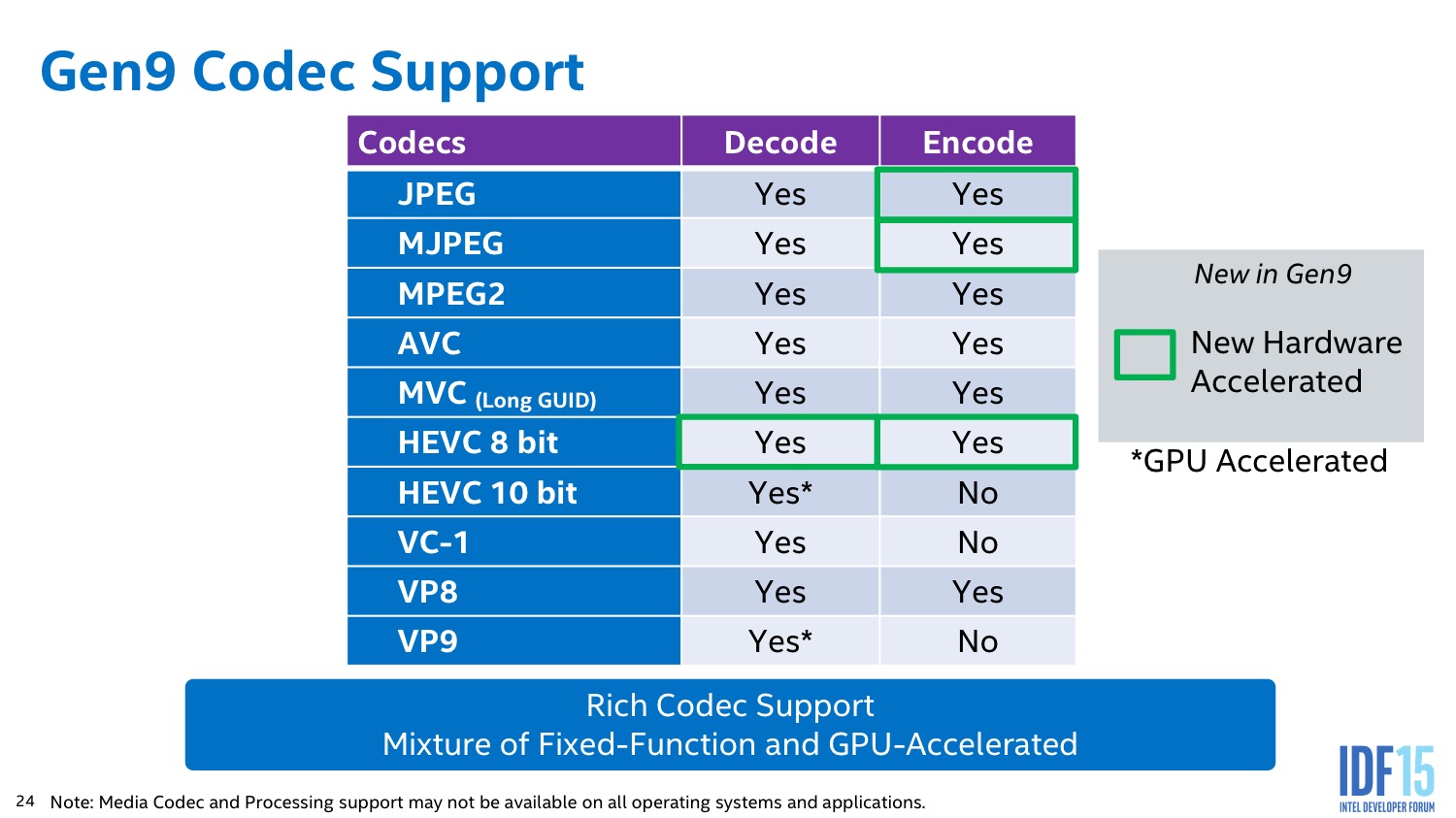

Du côté du MFX la plus grosse nouveauté concerne l'arrivée du décodage et de l'encodage du format H.265/HEVC 8 bit (le profil main). Intel confirme que pour l'instant, le HEVC 10 bit n'est pas décodé par le MFX, une accélération « GPU » est annoncée mais elle n'est pas transparente comme l'accélération DXVA des autres formats. Intel a également ajouté un encodage des formats JPEG et MJPEG, des formats triviaux à encoder pour le processeur, le but étant surtout de réduire la consommation via des unités fixes.

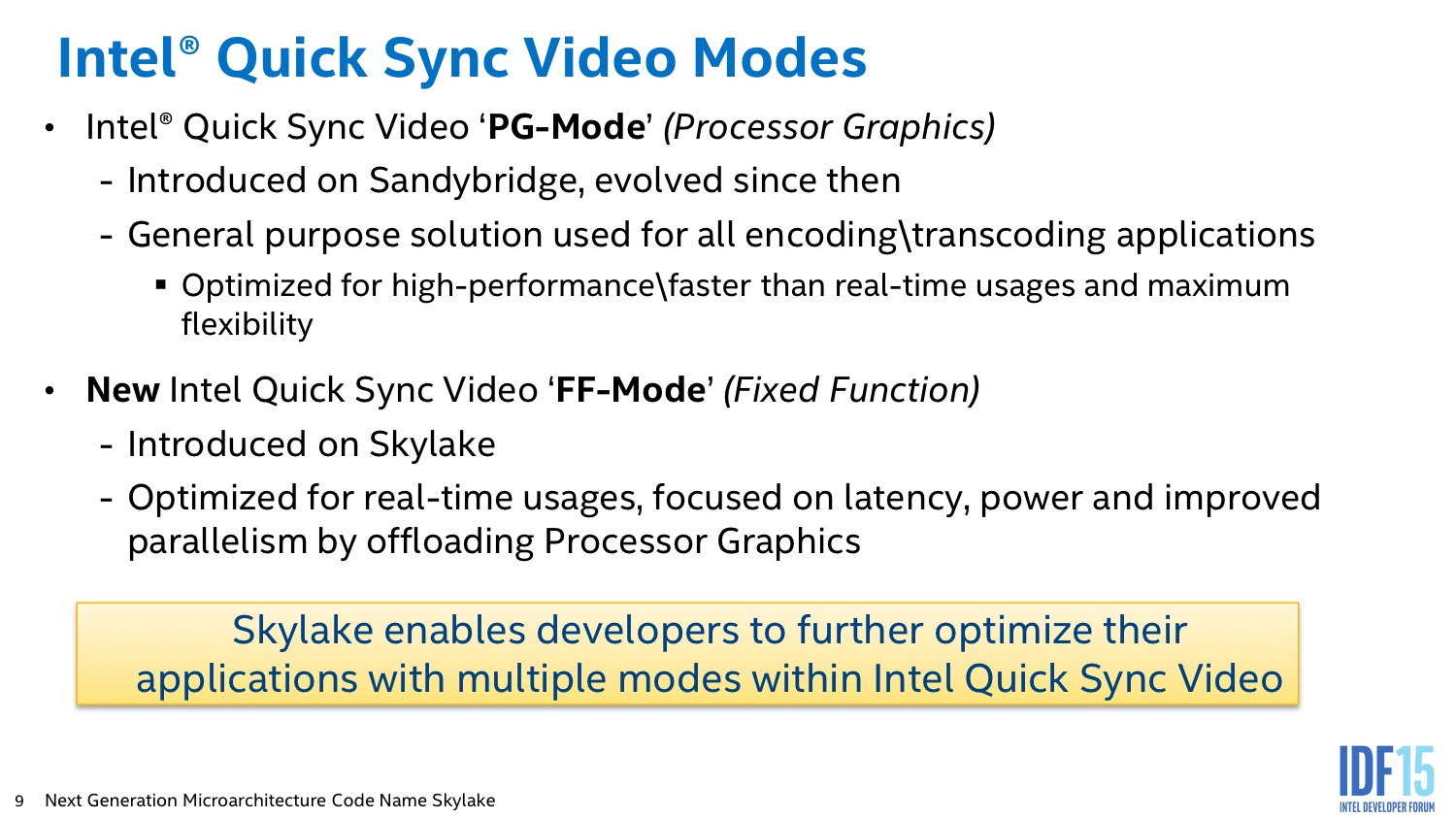

C'est d'ailleurs l'autre nouveauté que l'on retrouve au niveau de l'encodage H.264/AVC, Intel a ajouté des unités fixes pour réaliser un encodage temps réel (FF Mode). Le but de ce mode alternatif est de proposer un encodage d'une qualité un peu inférieure, mais avec un débit et un temps de compression prévisible.

Nous avons pu voir une démo sous Starcraft II, ou l'on pouvait noter une qualité en dessous de ce que l'on obtient via le mode classique, mais tout à fait suffisante pour streamer en temps réel une partie en ligne avec un impact minimal sur la consommation et les performances CPU.

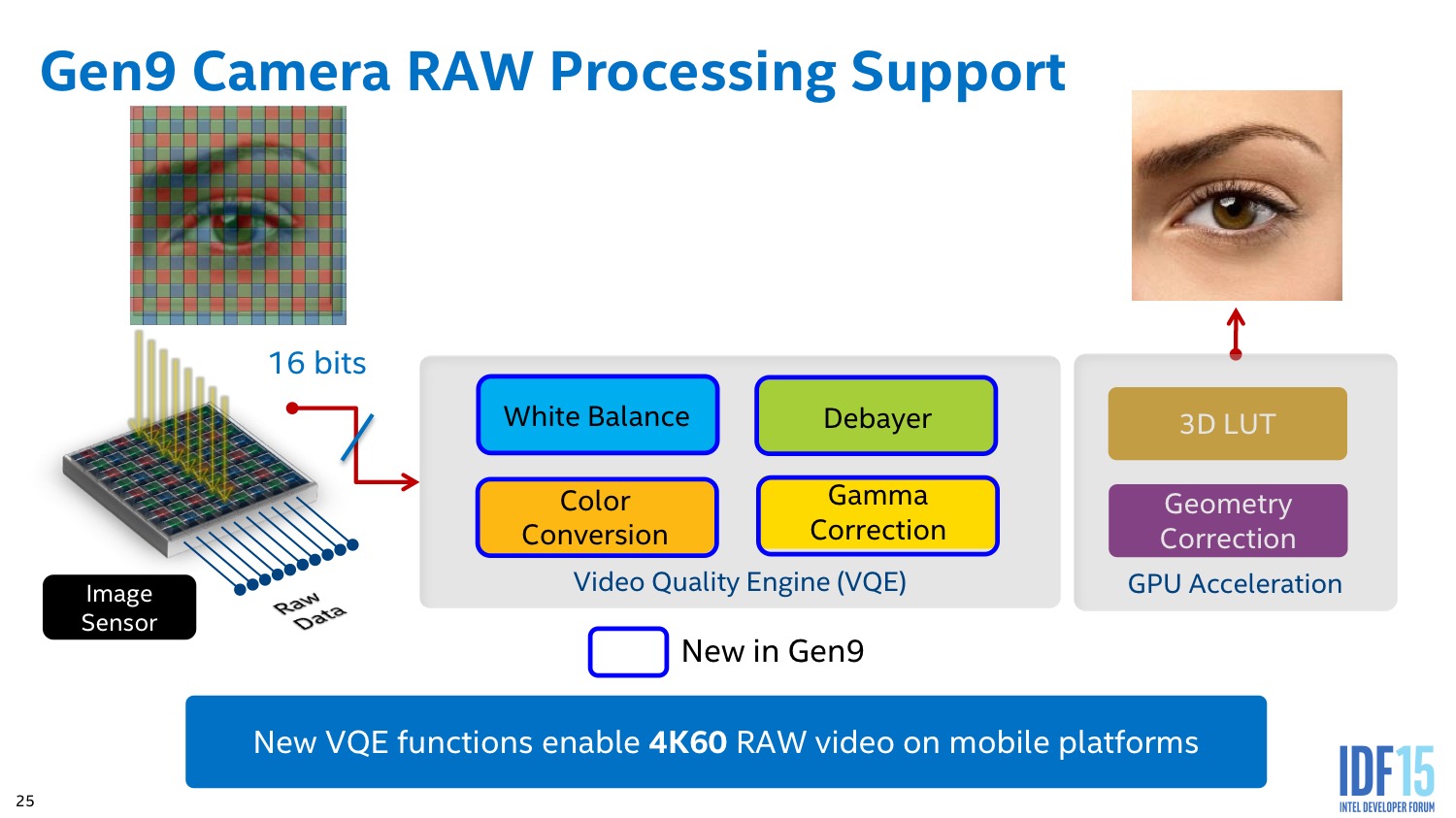

Du côté du VQE, c'est le traitement des formats RAW qui est accéléré avec les opérations de correction de balance des blancs, conversions d'espace colorimétrique et correction de gamma nottament. Des traitements qui peuvent s'appliquer non seulement aux photos, mais également aux vidéos RAW en provenance de DSLR/caméras vidéos 4K.

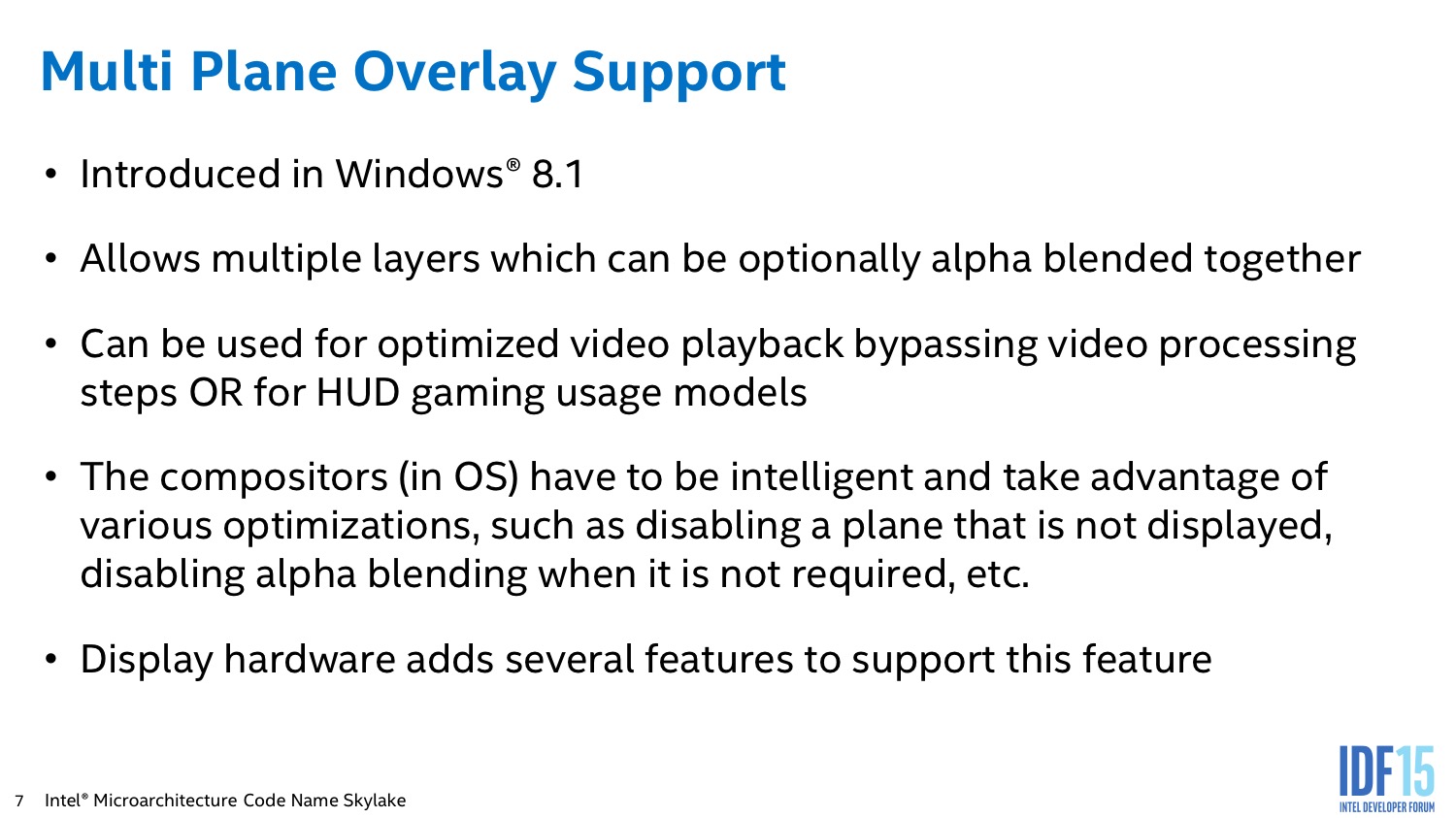

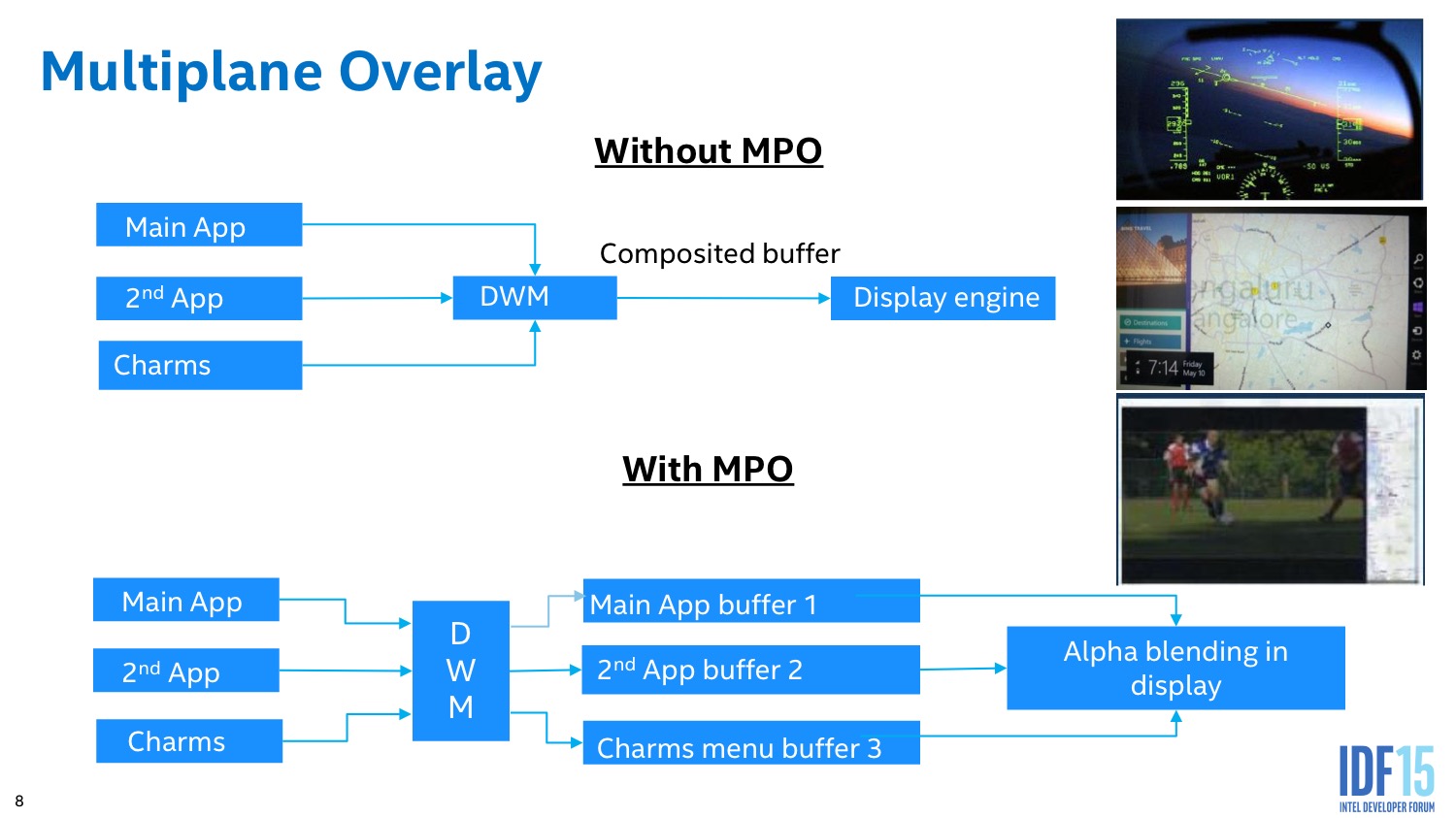

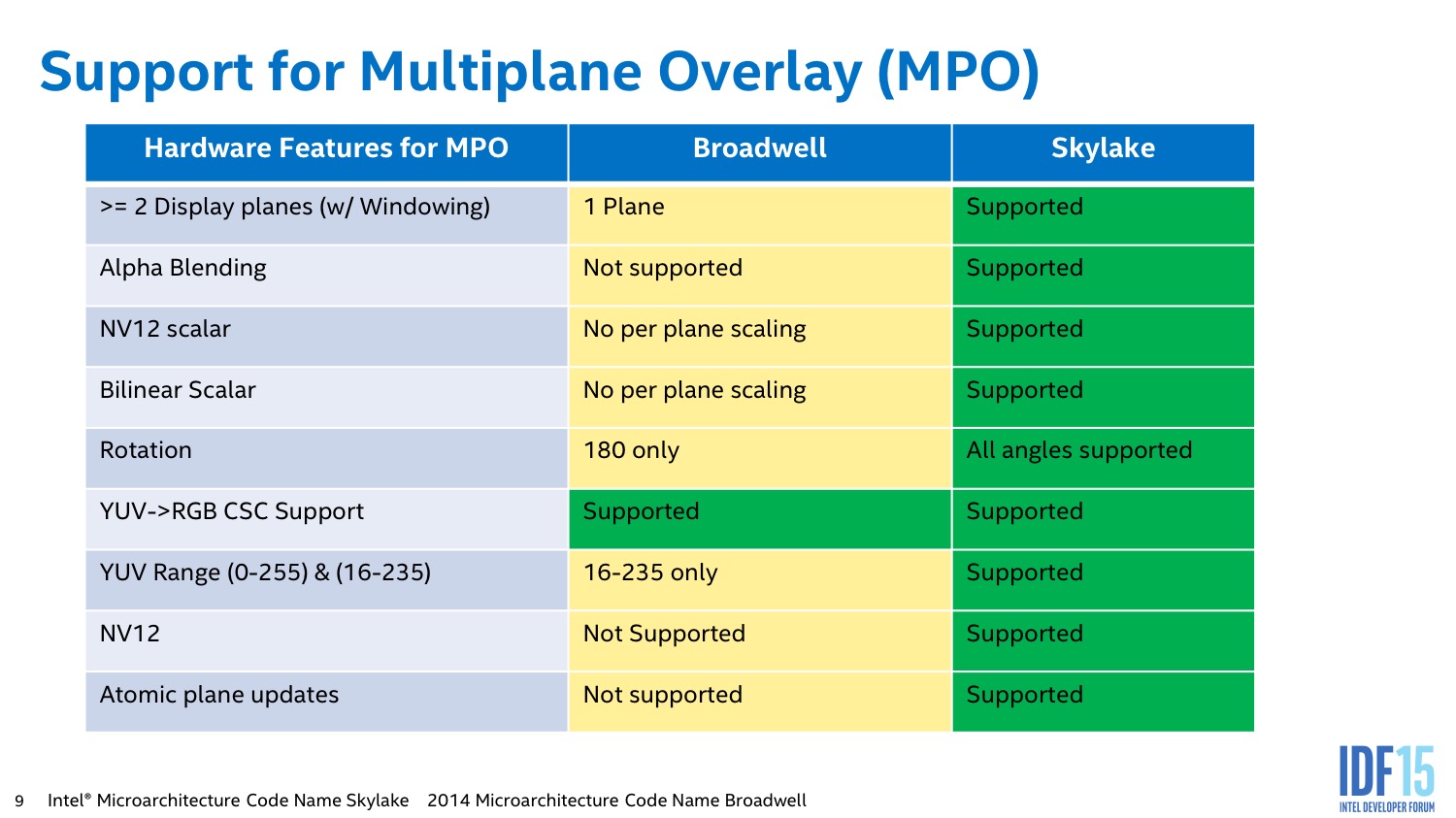

Enfin, le SFC est une nouveauté, c'est lui qui permet la gestion de ce que Microsoft appelle le mode Multi Plane qui permet d'afficher les vidéos en limitant au maximum les interactions avec la mémoire en accélérant en temps réel les opérations de scaling et conversions de couleurs. Les vidéos décodés sont ainsi adaptées directement à l'écran sans avoir besoin de passer par la mémoire centrale ou un cache pour traitement. Une fonctionnalité qui est également implémentée par AMD dans ses APU Carrizo pour rappel.

Système d'affichage

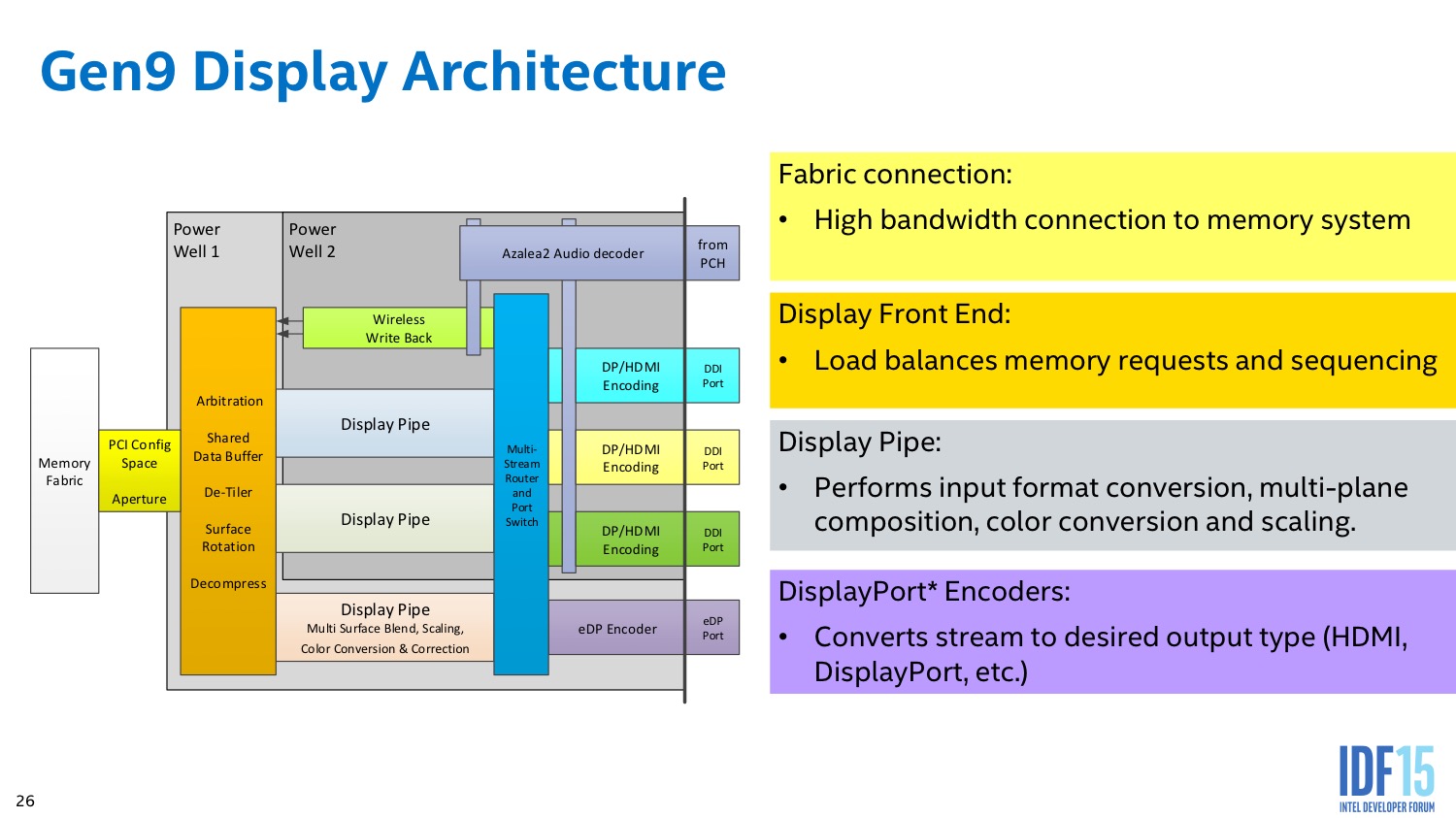

De ce côté Intel a effectué plusieurs remises à niveau de sa plateforme, en supprimant la liaison FDI entre le CPU et le chipset et en supprimant dans ce dernier la gestion des sorties analogiques VGA. Aujourd'hui, si l'on souhaite ajouter à sa carte mère Skylake une sortie VGA, il faudra rajouter une puce pour convertir le signal numérique en analogique, ce qui explique la rareté des sorties VGA sur beaucoup de cartes mères annoncées par les constructeurs, là ou elles étaient pléthoriques dans les gammes Z87/Z97 !

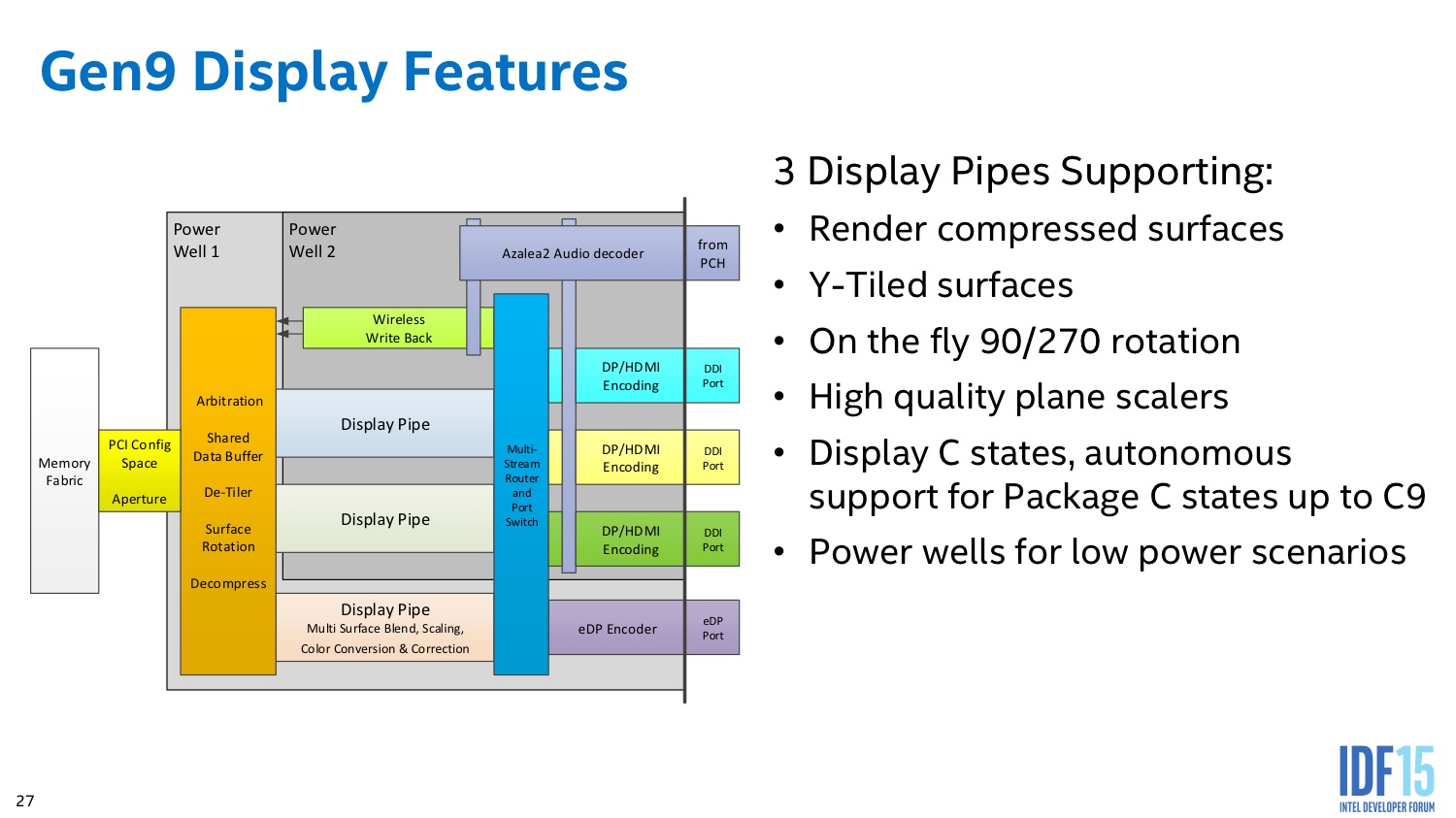

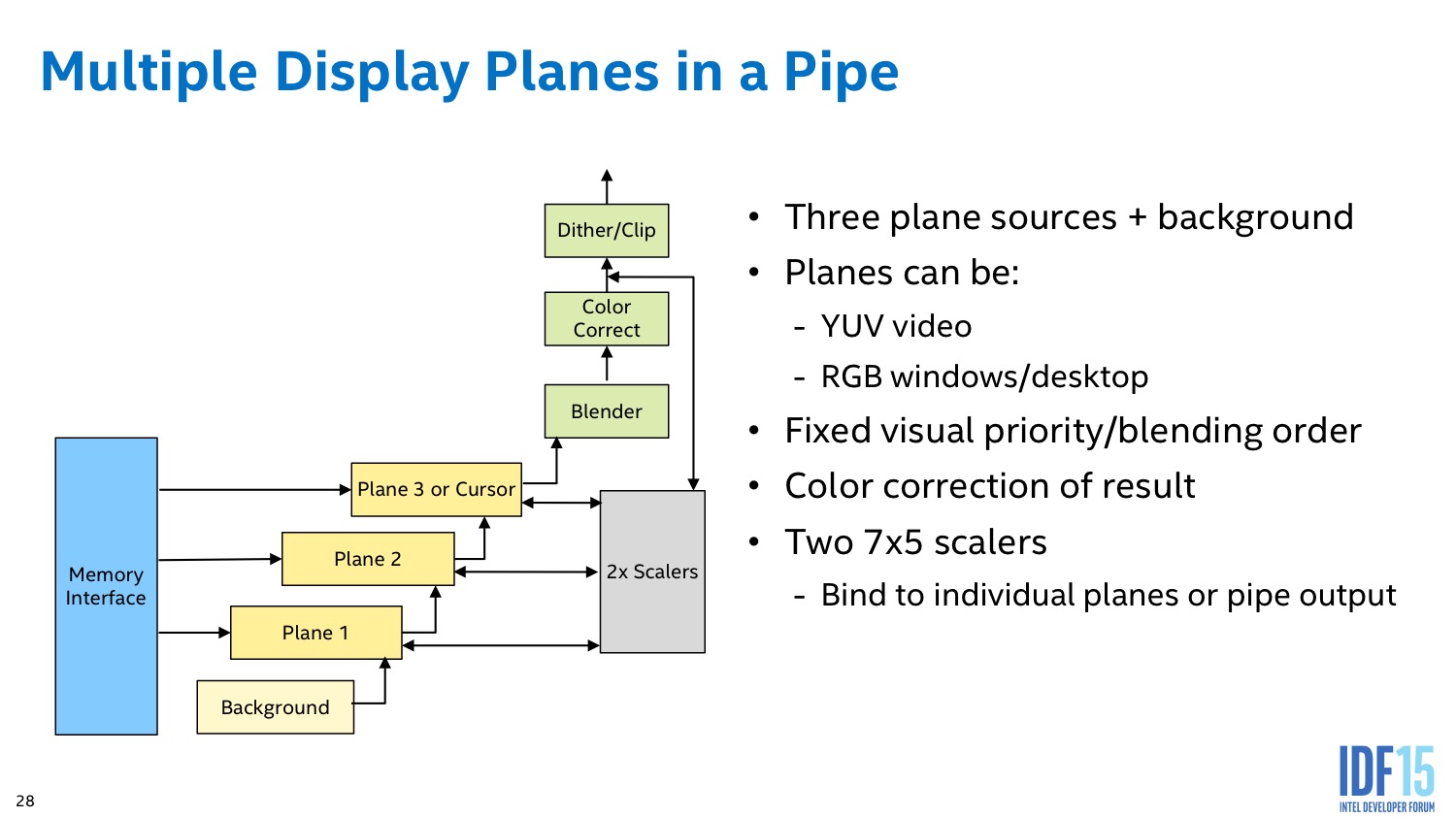

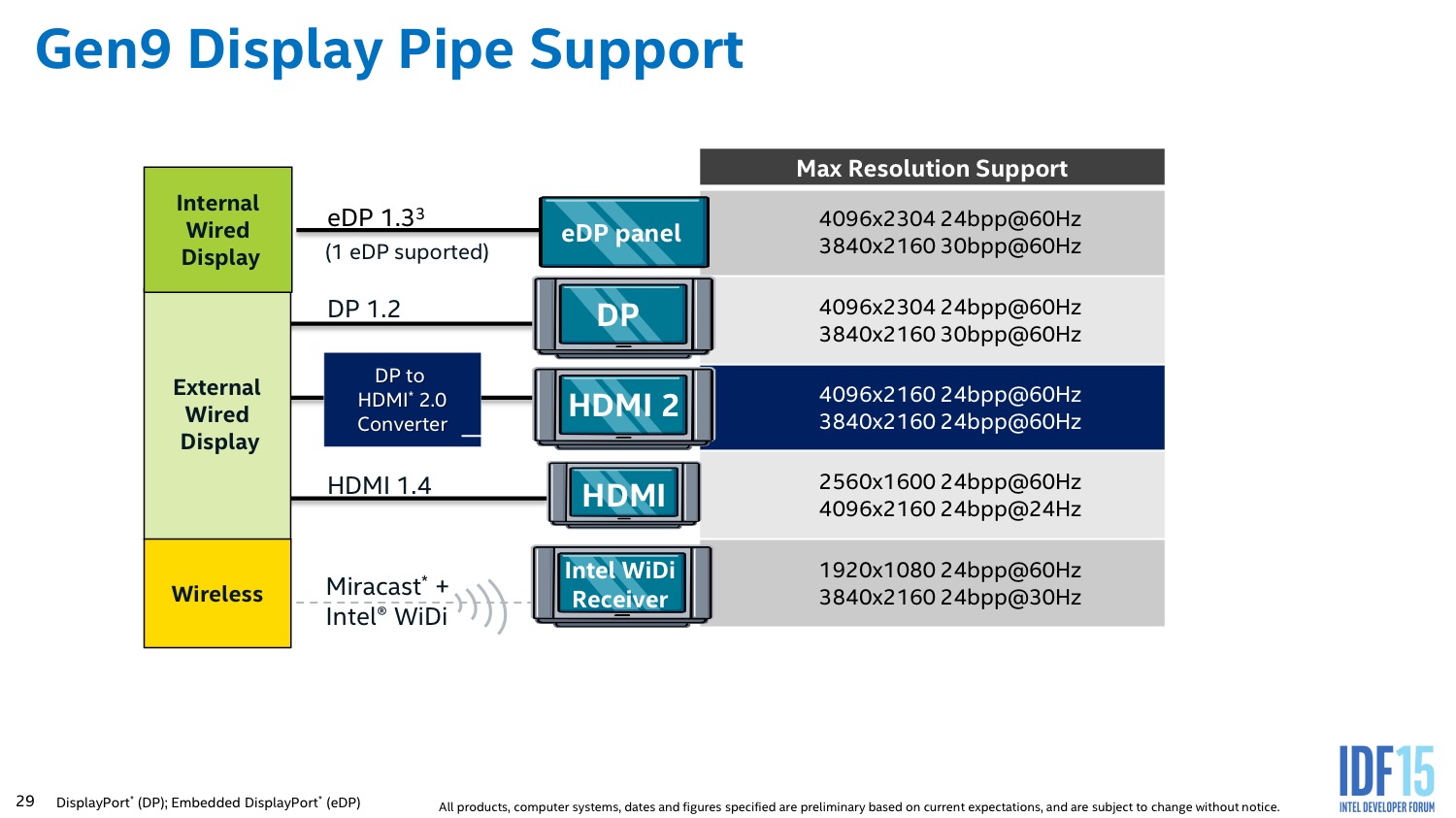

On retrouve toujours à l'intérieur trois « display pipe » qui peuvent être utilisées en simultané pour gérer jusque trois écrans. En pratique chaque pipe est capable de « composer » les images à partir de plusieurs plans (4 dans Skylake, une nouveauté). Typiquement en plus d'un fond fixe, on peut avoir une ou plusieurs vidéos, ainsi qu'un plan dédié en général à l'affichage du curseur de souris. Les pipes composent ainsi indépendamment jusque trois images. Ces sorties sont enfin multiplexées vers les trois sorties DDI, qui s'occupent de convertir les images générées vers le format de sortie (DisplayPort ou HDMI).

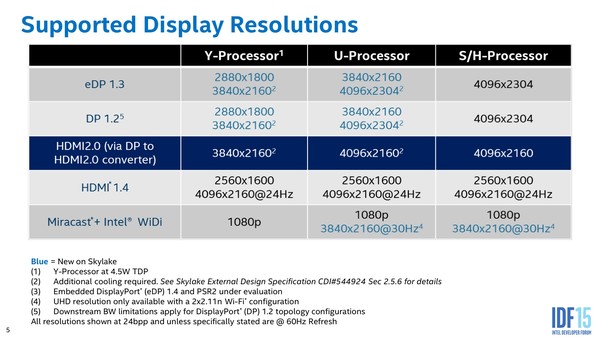

Avec Skylake l'autre nouveauté principale est qu'il est désormais possible d'atteindre le 4K 60 Hz pour les versions desktop. Comme nous l'avions indiqué à l'époque, Intel ne gère pas le HDMI 2.0, même s'il est possible en théorie de convertir la sortie d'un port DP 1.2 vers le HDMI 2.0. Plusieurs cartes mères Z170 avaient été annoncées avec ce support mais comme nous l'avons vu chez Gigabyte, l'annonce de ce support a été retirée des spécifications même si le convertisseur est bien présent sur la carte, sans que l'on sache s'il s'agit d'un problème de firmware ou d'autre chose.

Notez que le support diffère sur les modèles U (15W) et Y (4.5W) ou le constructeur limite la résolution maximale pour limiter la consommation. On note avec attention que certains modes sont autorisés uniquement si l'OEM propose un refroidissement suffisant.

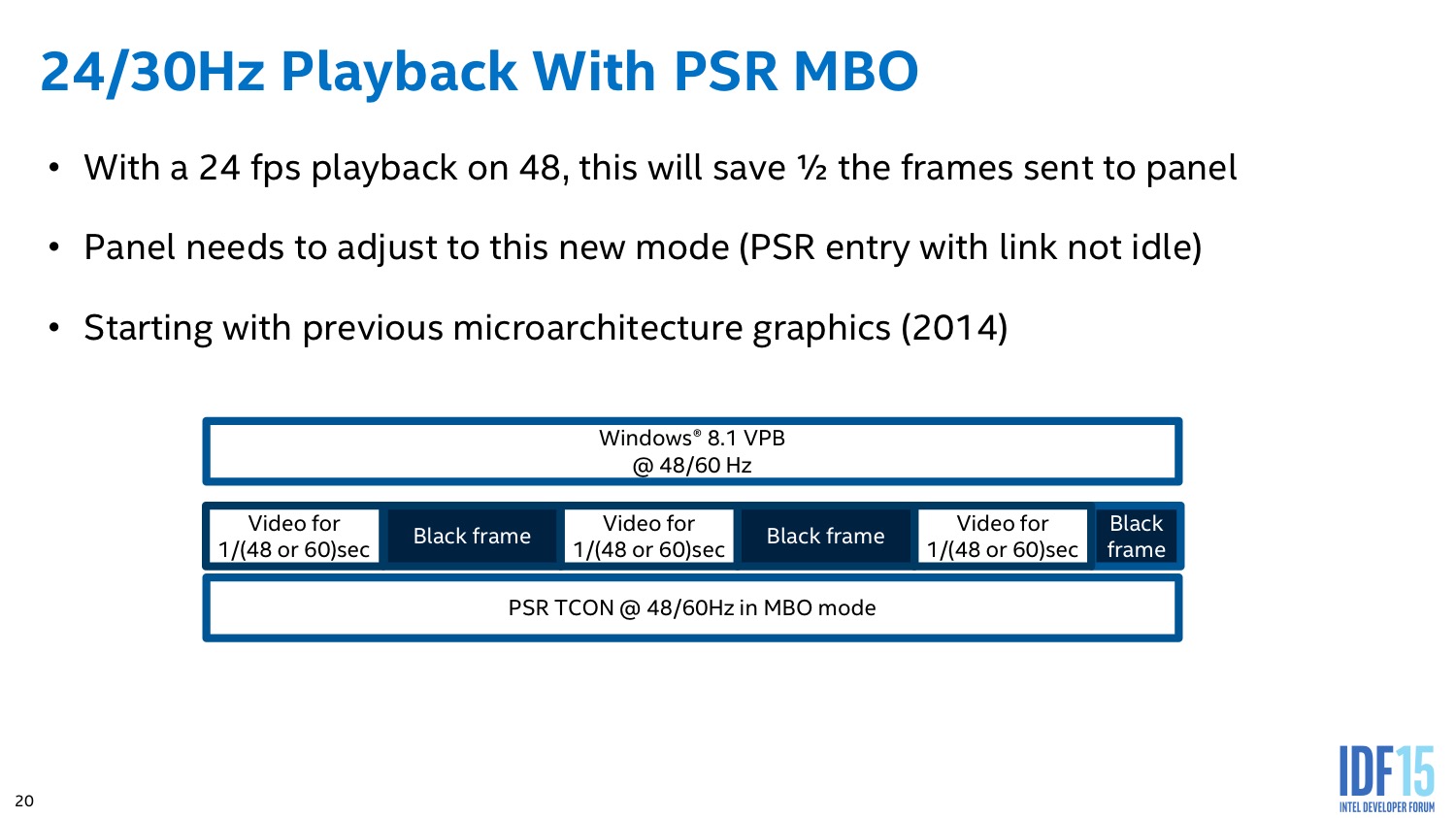

On notera enfin qu'en ce qui concerne l'affichage, Intel a indiqué être prêt à adopter l'extension « adaptive sync » de la norme DisplayPort. Cette extension qui permet de faire varier le taux de rafraichissement à la volée avait été développée pour rappel par AMD. On ne sait pas quand, ni avec quels iGPU l'adaptive sync pourrait être supporté par Intel. Théoriquement le support de la version eDP semble être présent depuis Broadwell mais rien ne dit que cela puisse s'appliquer aux DDI qui gèrent les sorties DP actuellement dans Broadwell et Skylake.

IDF: Alpine Ridge et Thunderbolt 3

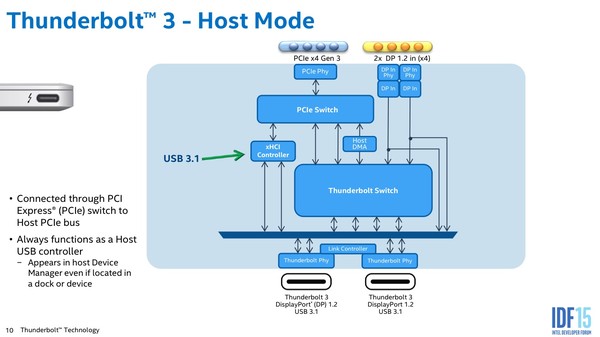

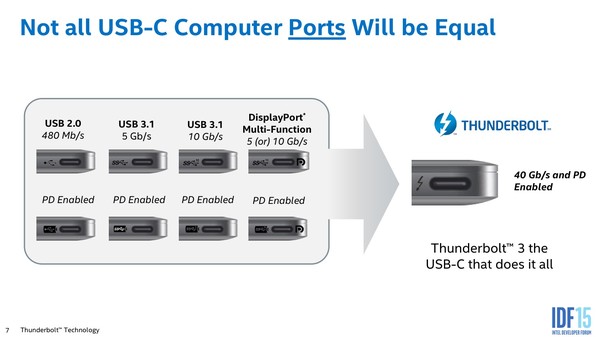

Au milieu des sessions sur l'USB 3.1, Intel présentait également Thunderbolt 3. Pour rappel, Thunderbolt 3 a été annoncé l'année dernière par Intel et utilise lui aussi le connecteur USB Type-C.

Techniquement, Thunderbolt 3 repose sur ce que l'USB-IF appelle « l'alternate mode », un mode de fonctionnement alternatif qui permet, après négociation, de reconfigurer les quatre canaux de données présents dans les câbles USB Type-C.

L'alternate mode est déjà utilisé pour la gestion du DisplayPort au travers de l'USB. Un autre mode alternate est reconnu aujourd'hui par l'USB-IF, le MHL développé par le MHL Consortium . Le MHL vise plus particulièrement à résoudre les questions de connectivité avec les téléviseurs et autres périphériques grand public, ainsi que l'électronique embarqué dans les automobiles.

Une différence fondamentale entre DisplayPort, MHL et Thunderbolt 3 est que dans le cas des deux premiers, il s'agit de standards ouverts. Pour cela, l'USB-IF a crée une nouvelle classe d'identifiants (les SID) qui peuvent être partagés par les constructeurs qui adhèrent au standard.

Thunderbolt 3 est différent car il s'agit d'une norme propriétaire d'Intel, ce qui veut dire qu'Intel n'utilise pas de SID, mais des VID classiques (Vendor ID). Pour faire simple, seul Intel pourra développer des contrôleurs Thunderbolt à l'avenir car le mode alternatif ne peut s'activer qu'entre des périphériques qui disposent de SID ou de VID identiques. On ne s'attendra donc pas a voir Intel proposer des licences à d'autres constructeurs de contrôleurs USB à l'avenir.

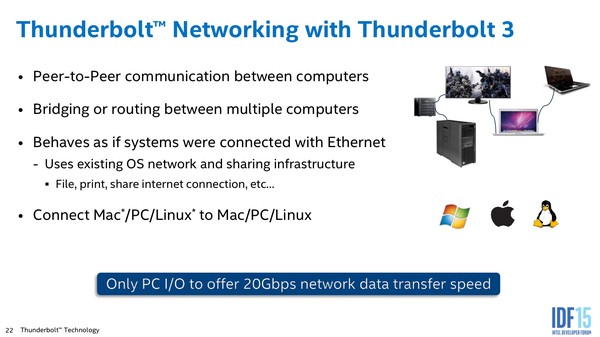

Thunderbolt 3 ajoute également un mode réseau peer to peer, qui est également possible avec l'USB 3.1, mais qui réclame un support dans le système d'exploitation. Un interlocuteur de Microsoft nous a confirmé que Windows 10 ajouterait sous peu un mode réseau via USB, ce qui est une magnifique nouvelle !

D'un point de vue technique, l'idée de Thunderbolt pour rappel est de faire passer des lignes PCI Express, dans le cas du 3, au travers de l'USB, une des rares choses (voir notre article précédent) qui n'a pas été standardisée par l'USB-IF. Interrogé sur le sujet, la question a pourtant bel et bien été envisagée. Dell, HP, et d'autres constructeurs de PC portables avaient commencé à développer un standard ouvert et interopérable en mode alternatif, qui aurait pu être utilisée pour standardiser le fonctionnement de docks par exemple.

Malheureusement l'effort n'a pas abouti et aujourd'hui la seule option pour faire passer du PCI Express par l'USB est Thunderbolt. Officiellement, l'USB-IF ne s'intéresse pas au développement d'une alternative même s'ils ont indiqué que la porte reste ouverte « si il y a de la demande ».

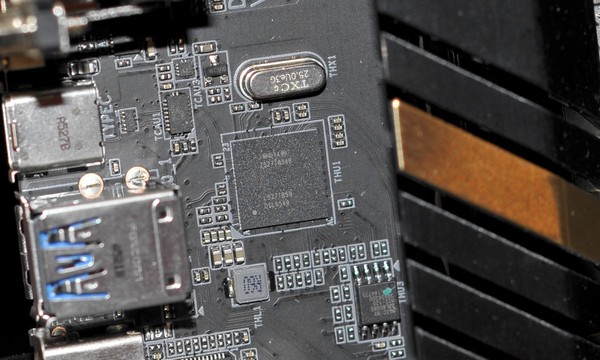

Le contrôleur USB 3.1/Thunderbolt 3 Alpine Ridge d'Intel

Aujourd'hui un seul contrôleur Thunderbolt 3 est « disponible », l'Alpine Ridge d'Intel. En pratique la disponibilité n'est pas encore effective et si Gigabyte a annoncé quelques cartes mères Z170 avec ce contrôleur, elles ne sont pas disponibles aujourd'hui.

La très très lourde Z170 G1 Gaming de Gigabyte dont même les ports SATA Express sont recouverts de métal !

Nous avons croisé quelques cartes sur le stand de Gigabyte mais en ce qui concerne la disponibilité, il semblerait au mieux qu'elle soit effective le mois prochain (Intel n'a pas voulu préciser officiellement mais la disponibilité d'ici un mois a été évoqué par un ingénieur dans les allées).

En pratique l'intérêt de Thunderbolt pourra se faire pour des docks, c'est le cas d'un portable MSI qui était montré avec un dock externe qui en plus d'avoir divers ports incluait un GPU graphique mobile AMD. Ce dock gère en même temps l'USB-PD pour charger le portable.

Une autre option montrée est un cas que l'on a vu de nombreuses fois au fil des années, celui d'utiliser une carte graphique desktop avec un portable. Un boitier de ce type était montré avec une Radeon R9 270 a l'intérieur. En pratique on reste limité à une connexion PCI Express x4.

Globalement notre avis ne change pas sur Thunderbolt. Si l'idée de partager des lignes PCI Express est excellente, Thunderbolt ne fait que fragmenter le futur écosystème de l'USB 3.1/Type-C. La stratégie d'Intel sera très probablement contre-productive a l'avenir et si le constructeur se vante dans ses présentations du fait que seul ses ports Thunderbolt 3 gèrent « toutes » les options de l'USB Type-C, en pratique cela ne fait qu'ajouter à la confusion. D'autant plus problématique quand ses propres contrôleurs sont en retard !

Il serait salutaire que l'USB-IF poursuive son effort de développement d'un standard d'encapsulation du PCI Express ouvert, pour mettre un terme définitif à l'aventure propriétaire Thunderbolt.

IDF: L'USB Type-C en route pour l'universalité

Une des sessions les plus intéressantes auxquelles nous avons pu assister concernait l'USB, et plus spécifiquement les standards autour du nouveau connecteur plat et reversible Type-C, et de la norme de chargement (USB PD 2.0/2.1).

De nombreux sujets ont été couverts mais on retiendra quelques grandes lignes. D'abord, la volonté de l'USB-IF (et d'Intel) de faire du connecteur USB Type-C le connecteur universel pour les 20 prochaines années ne fait aucun doute.

Au delà de l'augmentation du débit (10 Gb/s pour le 3.1 « Gen2 »), l'USB couvre de plus en plus d'utilisations. Le choix de DisplayPort d'utiliser les connecteurs USB Type-C devrait contribuer grandement à cette vision, même si l'on attend encore de voir des implémentations côté cartes graphiques et côté écrans.

Le prochain endroit ou l'USB Type-C devrait arriver en masse est celui des casques audio. L'USB-IF travaille actuellement sur la remise à niveau du protocole audio (USB Audio Device Class) pour permettre de transférer le son plus facilement de manière numérique, et surtout d'une manière beaucoup plus simple à implémenter dans les périphériques. Le but est relativement simple : proposer une alternative aux prises jacks analogiques. La finalisation de la norme est prévue pour les prochains mois, en s'assurant qu'un minimum de travail sera requis dans les périphériques pour permettre de réaliser des casques et oreillettes dans les années à venir sans avoir un surcout important sur le prix de fabrication.

Au delà des types de périphériques gérés par l'USB Type-C, le connecteur lui même a été prévu pour l'avenir. Nous avions déjà eu l'occasion d'en parler, les câbles USB Type-C incluent deux paires de lignes de données haute vitesse, dont seulement une seule est utilisée actuellement pour l'USB 3.1 Gen 2. Le mode Gen2 (10 Gbit/s) requiert une vitesse de transfert de 5 GHz, cependant les cables USB Type-C sont actuellement validées pour pouvoir supporter un minimum de distorsion à des fréquences plus élevées.

Les ingénieurs de l'USB-IF sont assez confiants sur le fait que tous les câbles Type-C actuels devraient pouvoir au minimum supporter une future fréquence de 10 GHz, et, si tout va bien, de 20 GHz. 20 GHz reste un challenge et si des normes ont été mises en place, il n'est pas dit qu'elles soient suffisantes pour la future implémentation de l'USB 20 GHz. L'USB-IF, même s'il ne s'y engage pas, pense avoir mis toutes les chances de son côté.

Techniquement on devrait donc pouvoir, avec la première génération de câbles à venir, voir arriver deux à trois nouvelles générations d'USB. Le choix technique de viser plus haut que nécéssaire est une très bonne chose et l'on ne peut que féliciter l'USB-IF sur ce choix !

Un autre point important à été évoqué : la sécurité. La première spécification de l'USB date de 1996, et malheureusement le modèle de sécurité n'a pas réellement évolué depuis. Avec les prises et chargeurs qui se multiplient (dans les lieux publics, transports en commun, etc) et les capacités qui explosent en nombre, de nombreux nouveaux vecteurs d'attaques ont été développés ces dernières années. Le plus simple est celui d'un chargeur USB qui ne fait pas que charger, et accède a la machine hôte en insérant par un biais ou un autre un malware. On a également vu des clefs USB dont le firmware était altéré pour insérer un device additionnel (en plus du « Storage Device » USB) capable de corrompre le système.

Une partie du problème de sécurité vient des systèmes d'exploitations évidemment, mais aussi de l'aspect universel de l'USB ou tout à été fait pour que les connexions soient les plus transparentes possibles. Un protocole d'authentification et des recommandations pour les développeurs de systèmes d'exploitations vont être mises en ligne d'ici 2016 pour tenter de limiter ces nouvelles attaques.

Du côté du chargement, un travail important a été fait pour simplifier la manière dont on peut connecter des périphériques ou il peut y avoir une ambiguïté (un PC portable et une batterie externe), pour pouvoir proposer de retourner facilement la relation. On retiendra surtout côté grand public que des logos ont été créés pour identifier les ports qui gèrent le chargement. Les logos cumulent chargement ainsi qu'une indication du niveau de performance mais malheureusement ils ne donnent pas d'indication sur la puissance maximale transférable, notamment au niveau des câbles.

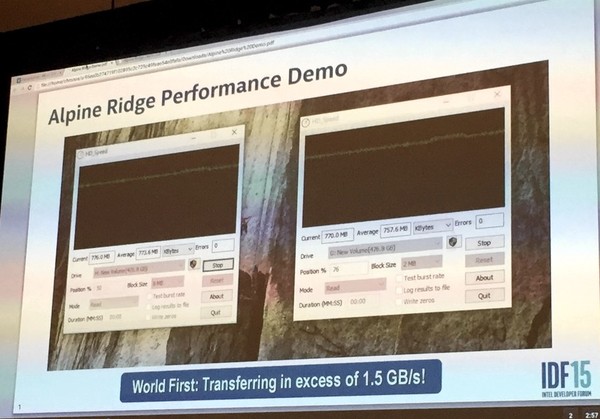

On terminera par une petite démonstration du contrôleur Alpine Ridge d'Intel. Il s'agit pour rappel du contrôleur USB 3.1/Thunderbolt 3 d'Intel que l'on retrouvera sur certaines cartes mères haut de gamme, particulièrement chez Gigabyte (voir notre actualité). Deux périphériques RAID avec contrôleur Asmedia, incluant chacun deux SSD M.2 étaient branchés sur le contrôleur d'Intel, avec un débit total atteint de 1.5 Go/s !

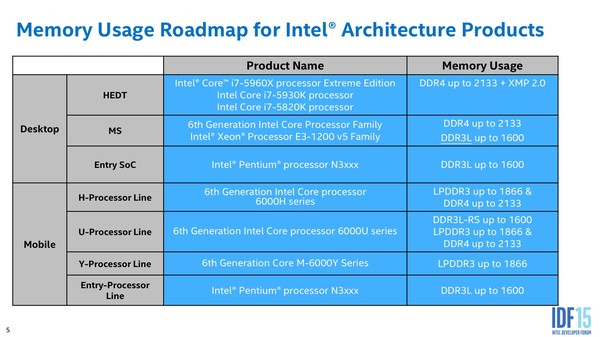

IDF: Support de la mémoire DDR3 sur Skylake

Lors d'une session sur la mémoire, Intel est revenu sur la question du support de la mémoire DDR3 traditionnelle. Pour rappel, Intel indique sur son site que les processeurs Skylake, dans le cas de l'utilisation d'une carte mère DDR3, ne supportent que la mémoire DDR3L (avec une tension de 1.35V).

Officiellement Intel nous a confirmé que Skylake ne supporte pas directement la mémoire DDR3 classique à 1.5V, cependant il est possible de modifier les cartes mères pour pouvoir supporter une tension de 1.5V ou supérieure, ce que semblent faire la majorité des constructeurs via une modification du BIOS.

Avec le passage au 14nm, les tensions à l'intérieur du processeur sont en baisse ce qui pose un problème pour le contrôleur mémoire. En pratique Intel ne valide pas l'utilisation de tensions mémoires au delà de 1.35V pour la DDR3 même si cela ne semble pas poser de problème majeur à l'usage. Selon notre interlocuteur il peut effectivement y avoir un risque (léger) pour le processeur ce qui pousse Intel a ne pas valider de tensions au delà de 1.35V.

Malgré tout les constructeurs de cartes mères "prennent le risque" en effectuant eux même la modification. Pour être complet, sachez que nous avons réalisés des tests CPU et GPU en DDR3 dansnotre article Skylake avec de la mémoire alimentée en 1.5V et même 1.65V sans le moindre problème. Il est cependant possible que certains modèles de cartes mères Skylake DDR3 se limitent à un support officiel en bloquant la tension, un point que nous essayerons d'éclaircir auprès des fabricants de cartes mères.

IDF: L'architecture CPU Skylake en détails !

Enfin ! Comme promis, Intel profite de l'IDF pour commencer a parler des détails de l'architecture de Skylake au travers de plusieurs sessions qui ont eu lieu en cette première journée. Nous avons tenté de regrouper le maximum d'informations dans cette longue actualité, en sachant que le constructeur tend a lâcher au compte goutte les détails d'une session à l'autre, il n'est pas impossible que certains détails ne soient dévoilés que dans les jours à venir ! Nous allons tenter de noter les différences par rapport à Haswell, vous pouvez vous rafraichir la mémoire en relisant notre article.

Avant de commencer, on notera que le constructeur travaille sur Skylake depuis plusieurs années (plus de 5) et que le projet, réalisé en Israel (Intel alterne deux équipes, une en Israel, l'autre dans l'Oregon) aura été modifié plusieurs fois pour rajouter successivement des TDP de 15 watts (avec les Ultrabook lancés à partir de 2008) puis de 4.5W (Core M) ainsi que des variations de packaging. On notera aussi, et c'est une première, que les détails que nous indiquons en dessous ne concernent que la version grand public de Skylake. La version serveur profitera de choix différents au niveau de l'architecture, on sait par exemple que seule la version serveur de Skylake supportera l'AVX512, mais les différences devraient être plus larges.

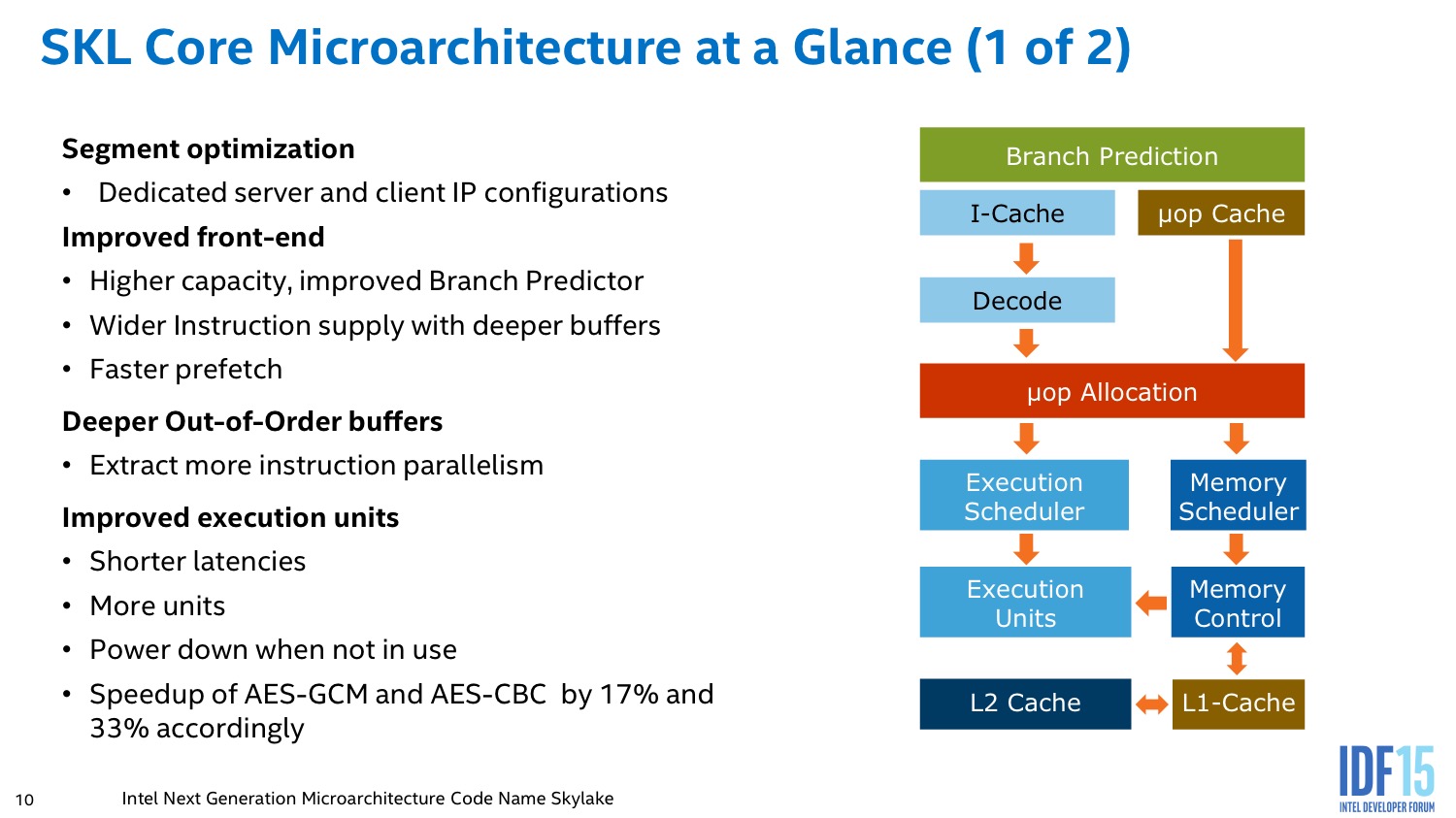

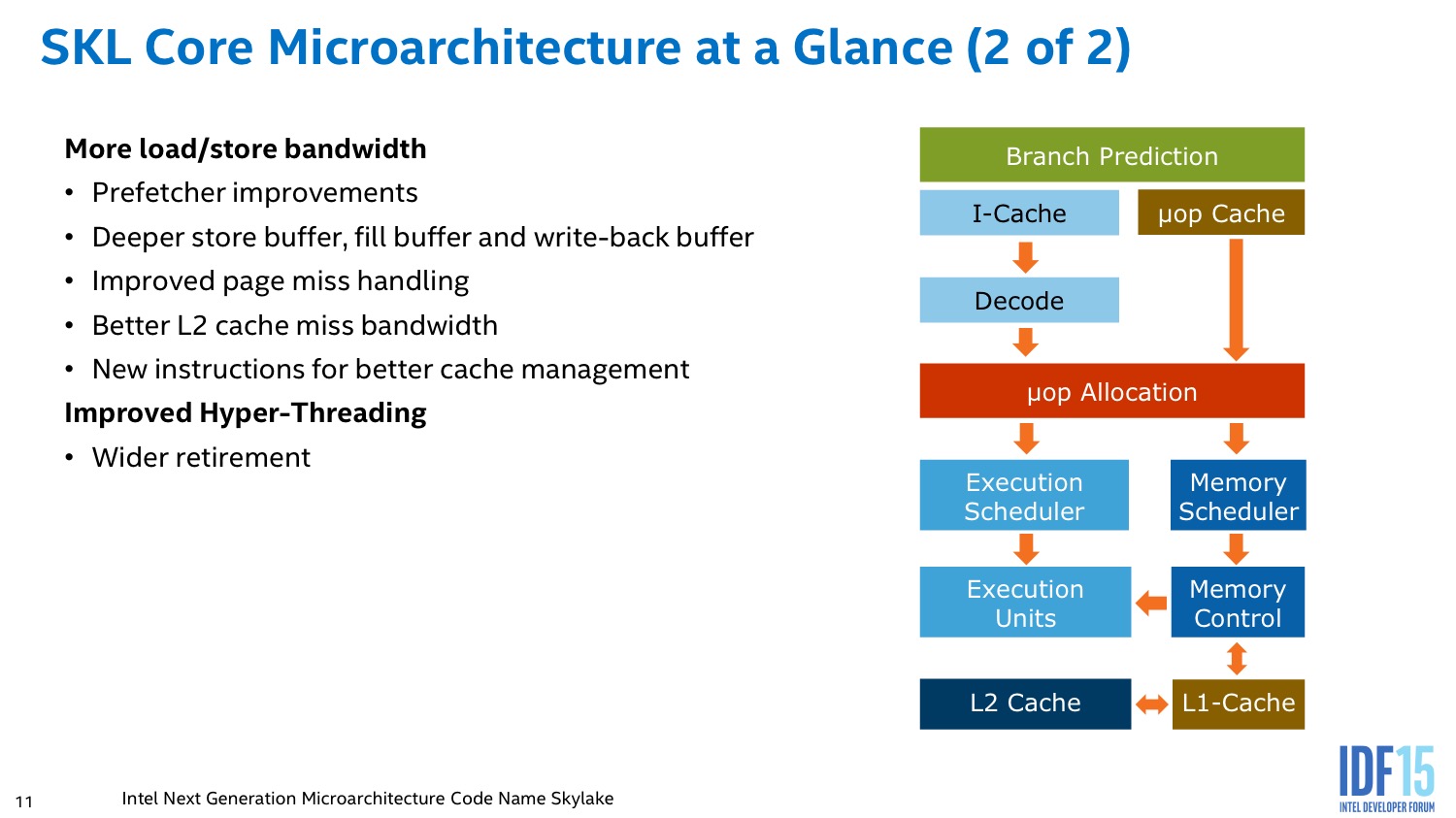

Frontend, scheduler et unités d'execution

Dans les grandes lignes on ne notera pas de changement majeur sur le frontend qui reste de type 4-way (jusque 4 instructions x86 décodées en simultanées) comme pour Sandy Bridge et Haswell. En pratique de ces quatre instructions CISC, jusque 6 micro-ops (les instructions RISC) peuvent toujours être générées.

En amont du décodage, on retrouve la prédiction de branchement qui évolue par contre significativement. Intel ne rentre pas dans les détails de l'algorithme mais indique qu'il est plus intelligent et capable de considérer des branchements beaucoup plus longs qu'auparavant. De la même manière, Intel a augmenté la taille des différents buffers durant les différentes étapes du front-end, un changement que l'on retrouve a presque toutes les nouvelles architectures.

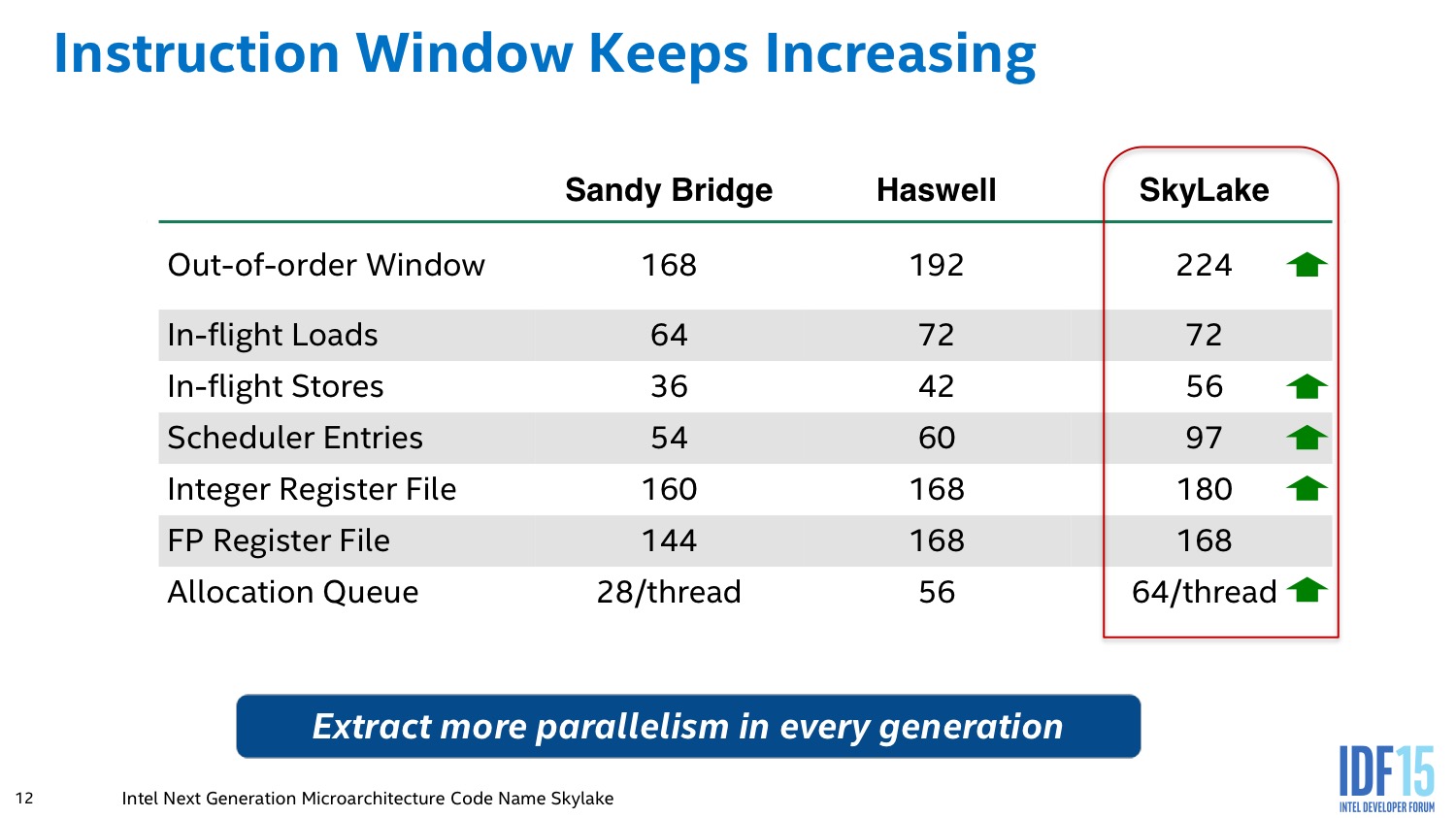

Les micro-ops décodées sont en effet stockées dans deux files capables d'en stocker 64 par thread (contre un buffer unique de 56 pour Haswell), un changement majeur qui permet au scheduler de tenter d'extraire un maximum de parallélisme.

Le scheduler a pour but de dispatcher les micro-ops vers les unités d'exécution. Il profite des files rallongées et de certains changements au niveau de ses algorithmes dans la gestion de l'hyperthreading.

Le point le plus flou pour l'instant concerne les unités d'exécution. Pour rappel, avec Haswell on disposait de 8 ports sur lesquels étaient répartis de multiples unités d'exécution (ALU pour les instructions sur les entiers, des unités AVX/flottants, les chargements/sauvegardes de données en mémoire, les branchements ). Pour l'instant tout ce que l'on sait, c'est que le nombre d'unités a augmenté sans savoir celles qui ont été ajoutées. Deux autres détails ont été donnés par les ingénieurs d'Intel : l'unité en charge des divisions gagne en flexibilité, tandis que la latence de traitement de certaines instructions FPU serait en baisse. Intel nous a promis que nous aurions plus de détails sur ces points dans une session à venir.

Globalement les changements sont intéressants dans le sens ou ils permettent en théorie de maximiser un peu plus l'utilisation des unités d'exécution de chaque coeur, ce qui peut se traduire dans certains cas par une augmentation importante des performances. Le constructeur a par ce biais réussi à améliorer significativement ses résultats dans un des benchmarks SPEC sur un coeur (ce qui a valu à nos confrères allemands de ressortir la rumeur - évidemment fausse - d'un hyperthreading inversé en fin de semaine dernière !). Les changements restent cependant très localisés et dans l'absolu, Intel continue d'affiner les grandes lignes d'une architecture Core, certes excellente, mais qui reste la même dans les grandes lignes depuis des années.

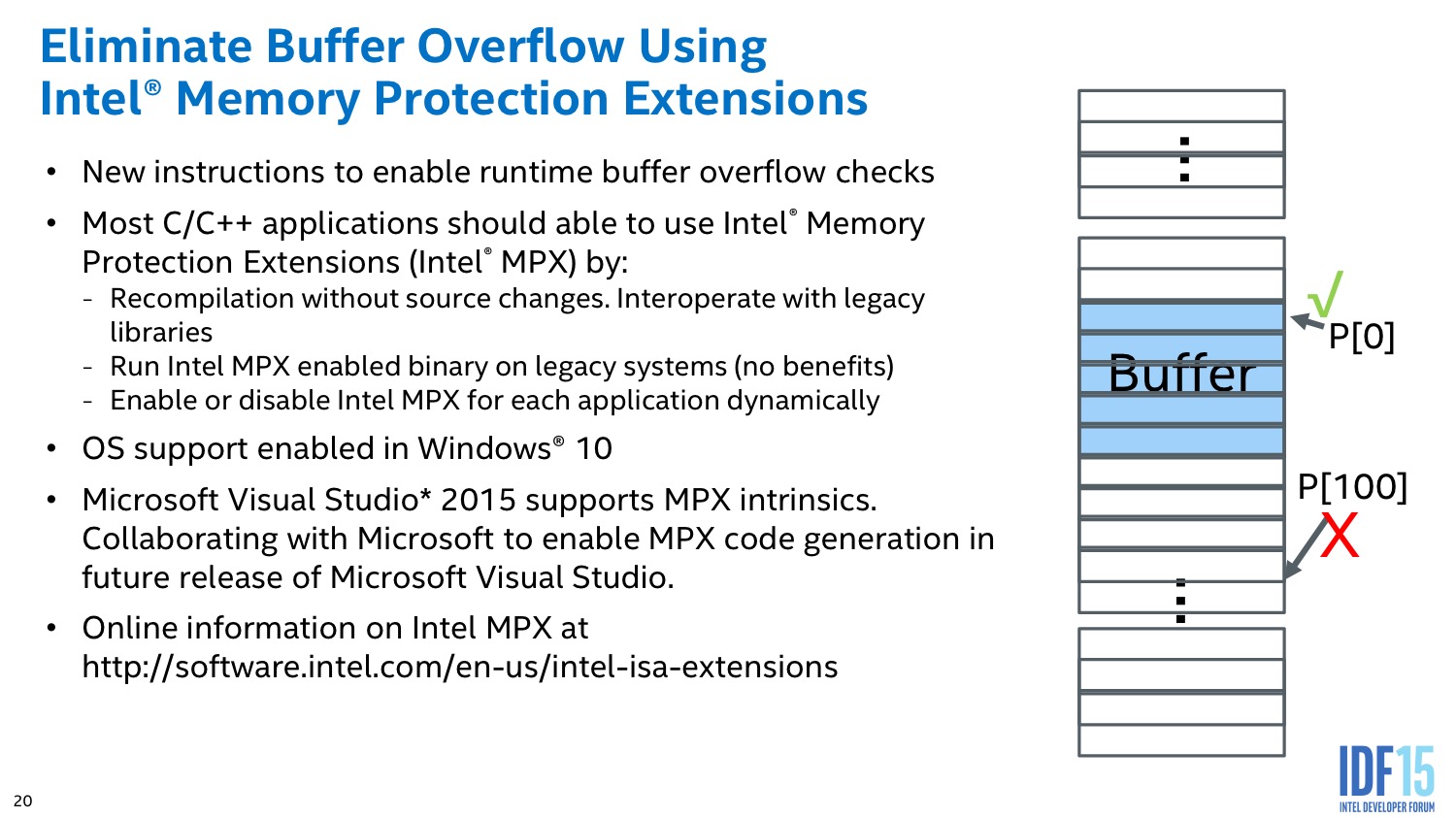

Jeu d'instruction

Lors de notre test de Skylake, nous avions noté la présence d'une nouveauté dans le jeu d'instruction : MPX, Memory Protection Extension. Ces instructions permettent de rajouter des vérifications sur les adresses mémoires accessibles pour éviter les attaques type buffer overflow et empêcher un processus d'accéder a de la mémoire a laquelle il n'a pas droit. Nous n'avons pas encore obtenu plus de détail sur ces instructions.

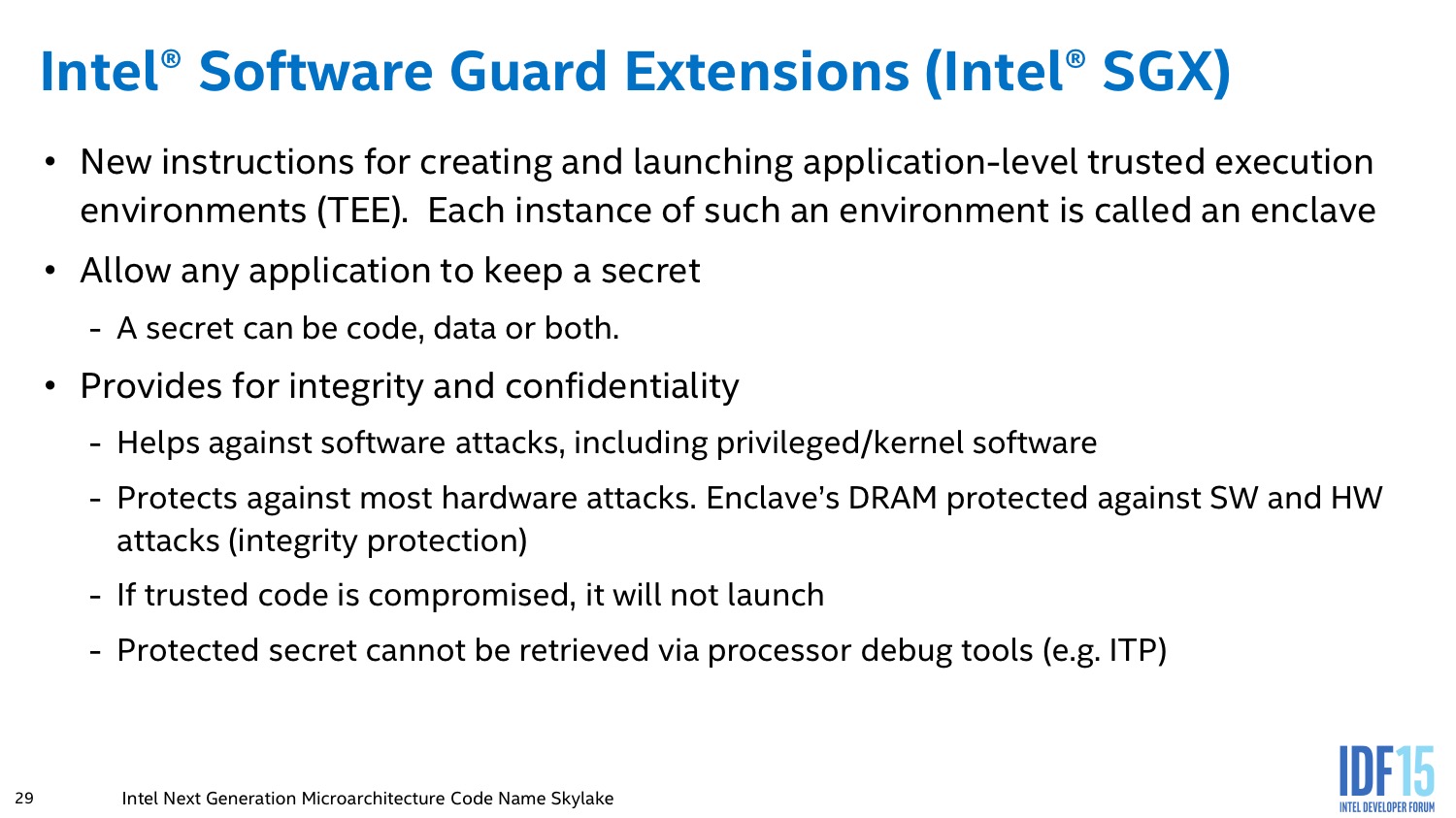

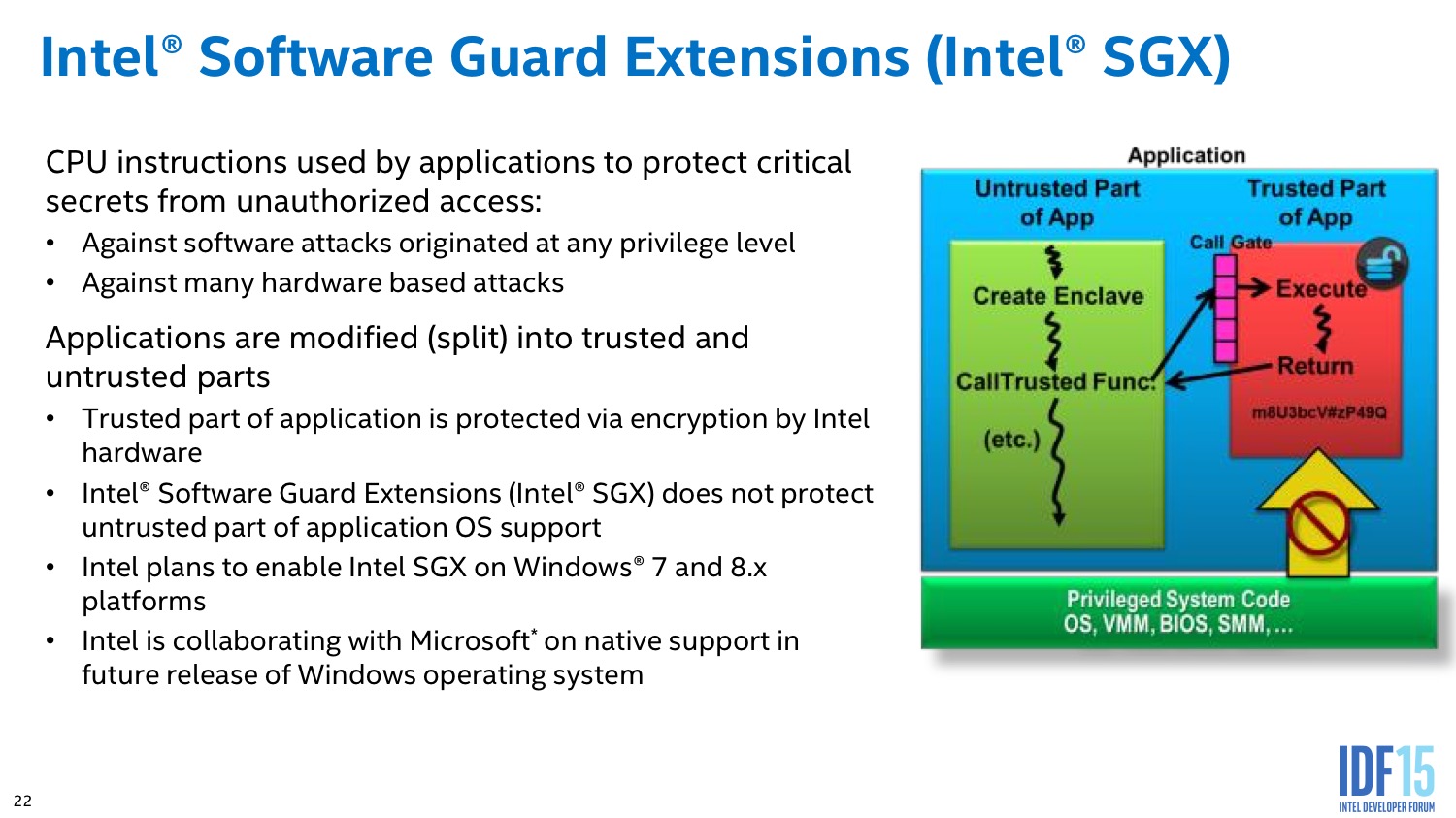

Par contre, une autre nouveauté complémentaire concerne ce que le constructeur appelle SGX, pour Software Guard Extension. Ces instructions permettent de créer des zones mémoires protégées qui ne sont accessibles qu'au processus qui les a crée, et qui, dans le cas ou les données auraient été tout de même corrompues, couperait le fonctionnement du process concerné afin de maximiser sa sécurité. De la même manière, l'utilisation d'une zone mémoire sécurisée (Secure Enclave) désactive toutes les possibilités de deboguage sur le système.

Si l'on imagine aisément l'utilité de ces extensions dans certaines situations dans le monde de l'entreprise, d'un point de vue grand public on pensera surtout aux implémentations éventuelles de DRM qui pourraient utiliser ces technologies à l'avenir.

Gestion de l'alimentation

Un gros travail a également été réalisé sur la gestion de l'alimentation avec un usage accru du power gating de certaines unités gourmandes, c'est notamment le cas des unités AVX2 qui sont éteintes lorsqu'elles ne sont pas sollicitées. Des économies ont été réalisées à tout les niveaux, particulièrement celui des interconnexions et des I/O pour limiter au maximum la consommation.

Les ingénieurs ont travaillé plus spécifiquement sur les scénarios idle ou « presque » idle comme la lecture vidéo pour augmenter au maximum la longévité de la batterie en usage mobile. Parmi les solutions retenues pour arriver à ce but, on retrouve l'ajout de domaines d'horloges séparés pour le System Agent, le contrôleur mémoire et l'I/O eDRAM (pour les modèles qui en sont pourvus).

Un travail important a également été réalisé sur l'unité de gestion de l'énergie (Power Control Unit) pour la rendre un peu plus intelligente dans de multiples scénarios ou elle devient capable d'estimer un risque de throttling et de réduire a l'avance la fréquence pour éviter d'atteindre la température maximale à laquelle un throttling sévère est inéluctable.

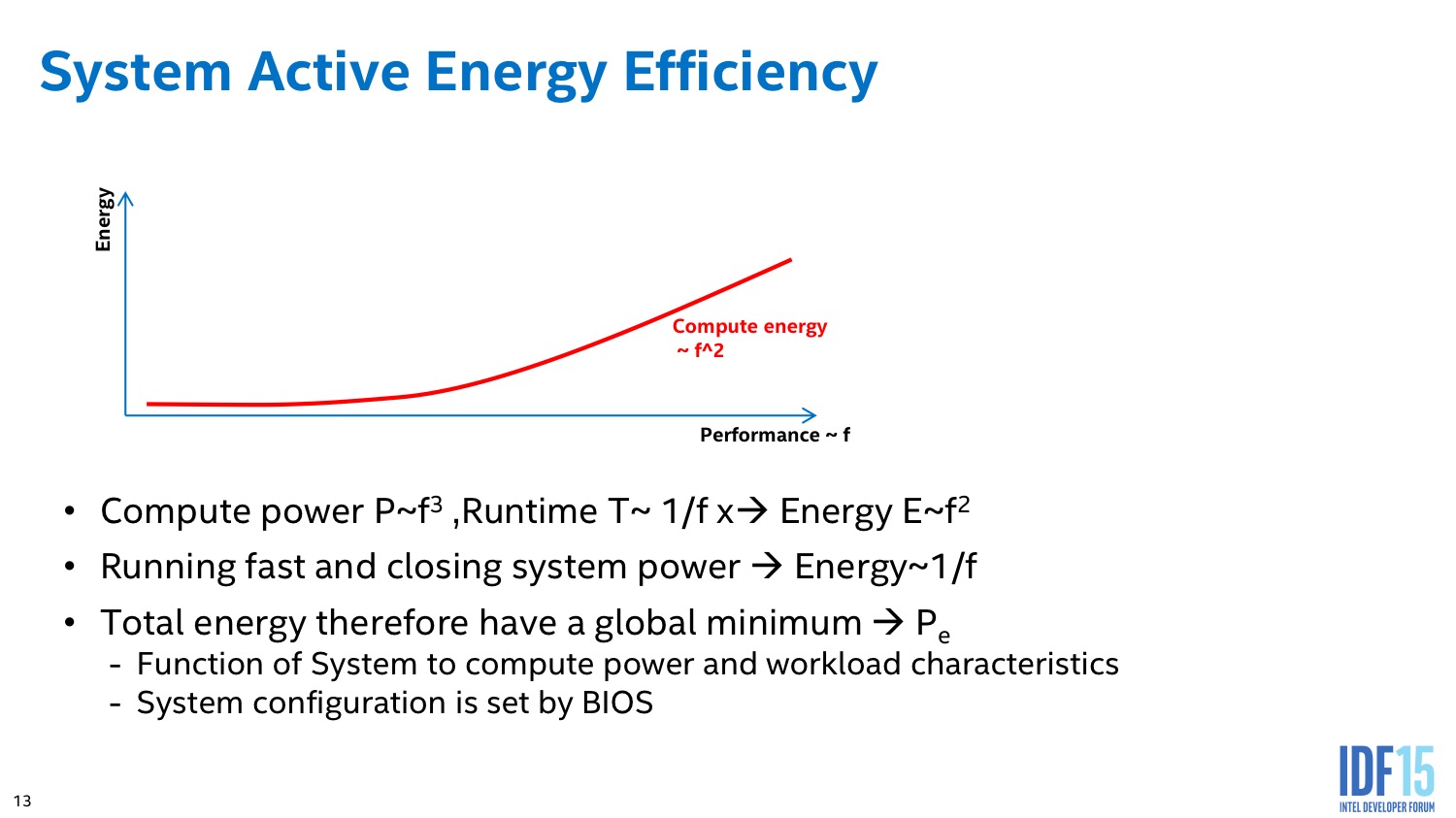

L'autre choix concerne l'utilisation du Duty Cycle Control en lieu et place d'un changement de fréquence. Comme indiqué par Intel, réduire la fréquence (via les P-States pour les coeurs) permet de diminuer la consommation de manière linéaire, et il est souvent plus efficace d'éteindre et d'allumer (un peu a la manière d'un contrôleur PWM) les unités tout en gardant une fréquence plus élevée.

Speed Shift

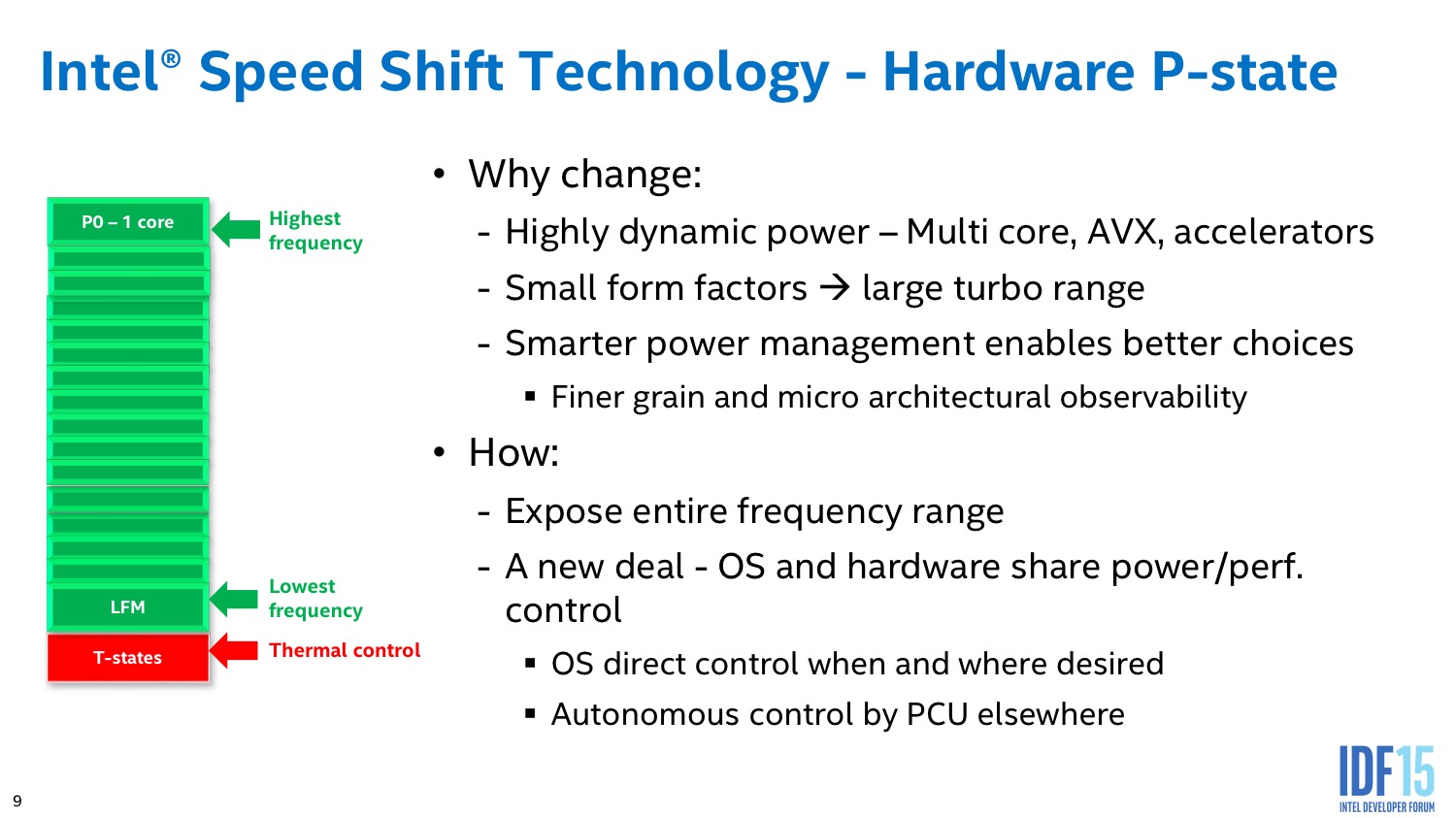

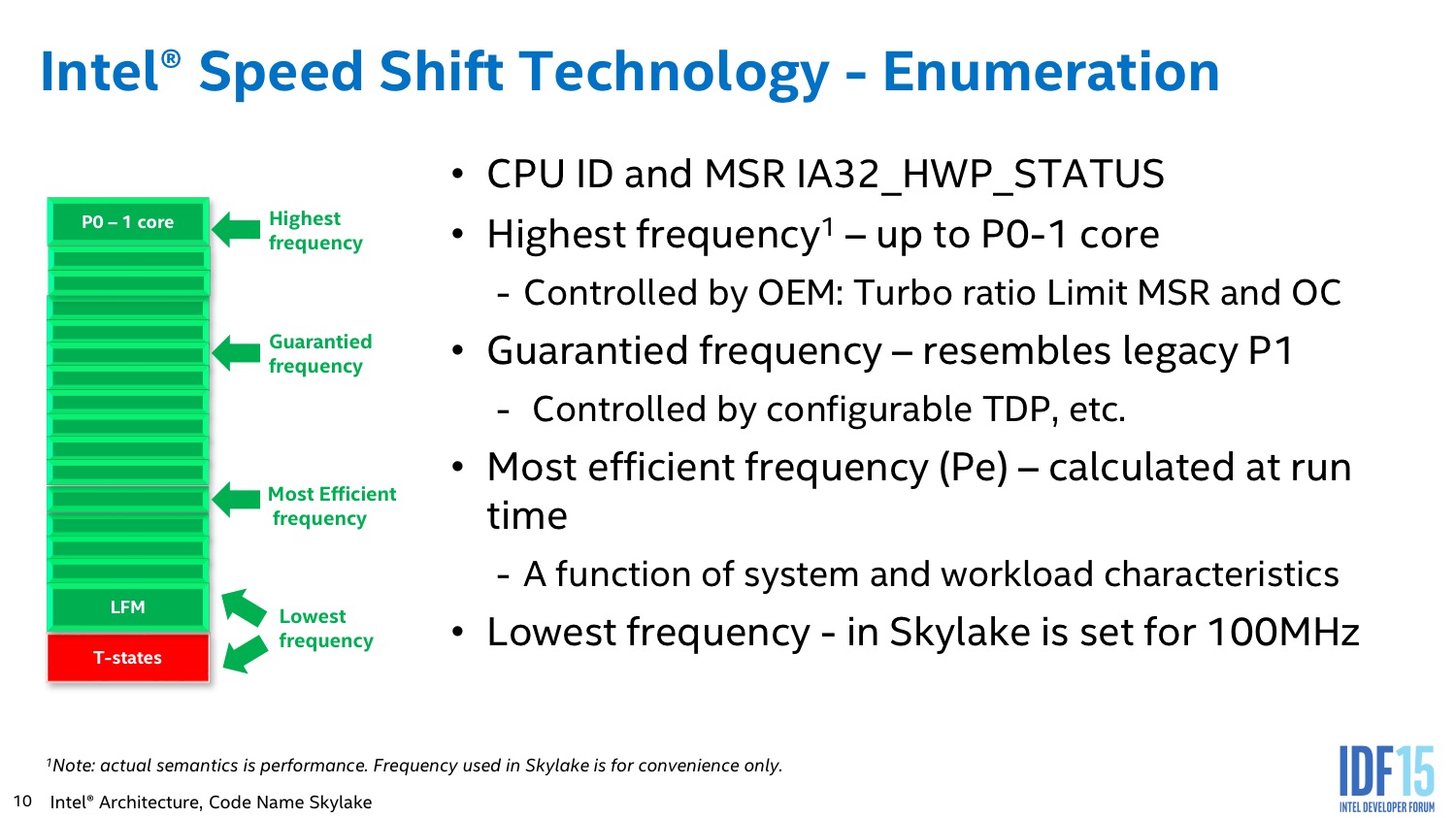

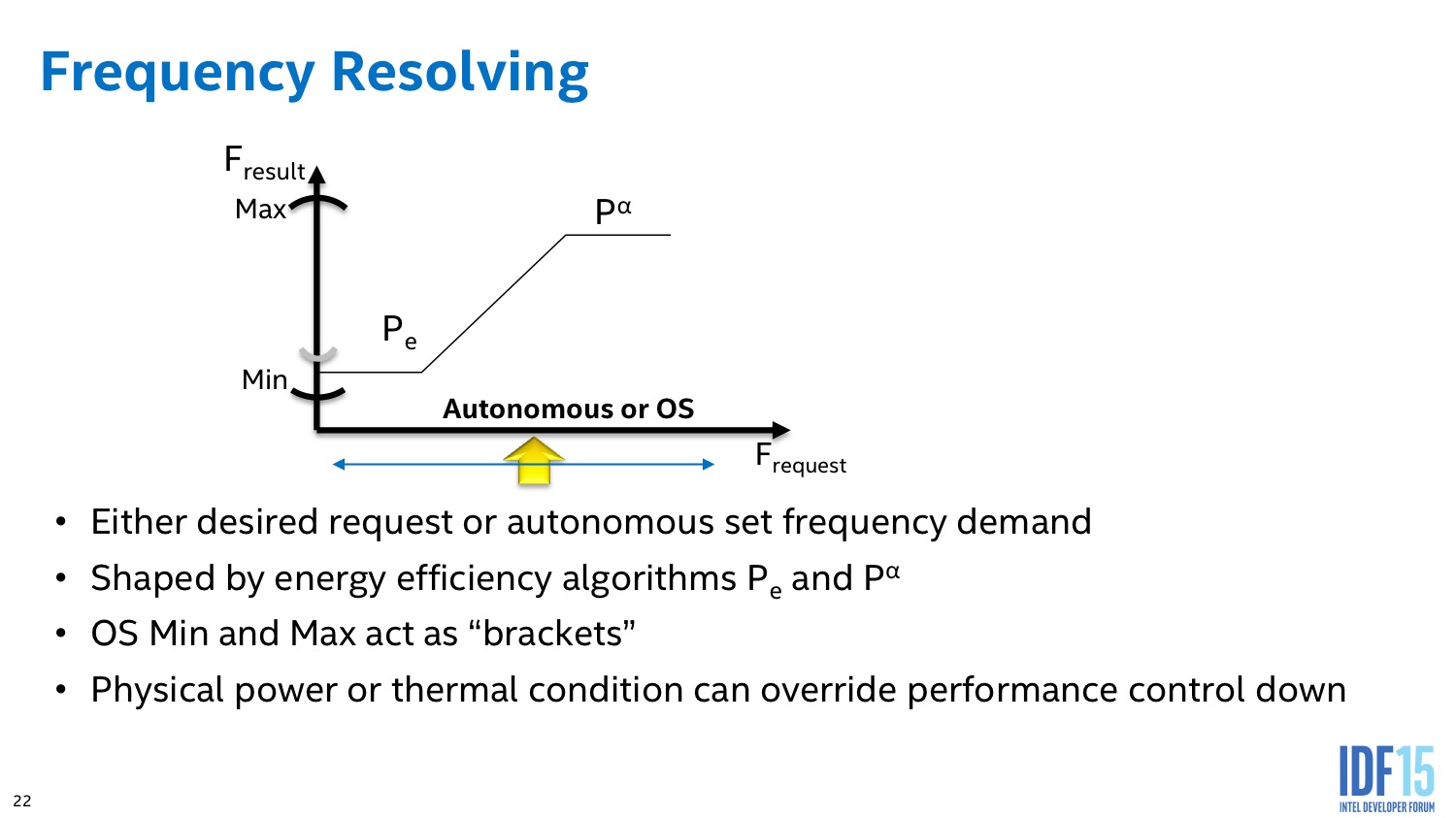

L'autre changement majeur concernant la PCU est ce qu'Intel appelle Speed Shift, un changement fondamental du fonctionnement des P-States. Pour rappel, la fréquence du processeur est gérée à la fois par le processeur lui même et le système d'exploitation. Le processeur propose une table dite de P-States (via les tables ACPI) qui indique les différents couples de tensions/fréquences qu'il peut utiliser.

Dans un fonctionnement classique, le système d'exploitation, en fonction de la charge qu'il traite, va contrôler explicitement les changements de P-States (ce qui requiert une latence d'environ 30ms selon Intel) en choisissant un niveau (par exemple, P1, la fréquence maximale « non turbo »). Il y a cependant - chez Intel - deux exceptions à cette règle. La première concerne les fréquences Turbo qui varient en fonction du nombre de coeurs actifs. Cette gestion s'effectue directement par le processeur. L'autre est le cas du throttle lorsque l'on dépasse la température de fonctionnement critique. Dans ce cas le processeur effectue seul (heureusement !) le throttling en passant dans les modes dits de contrôle thermique.

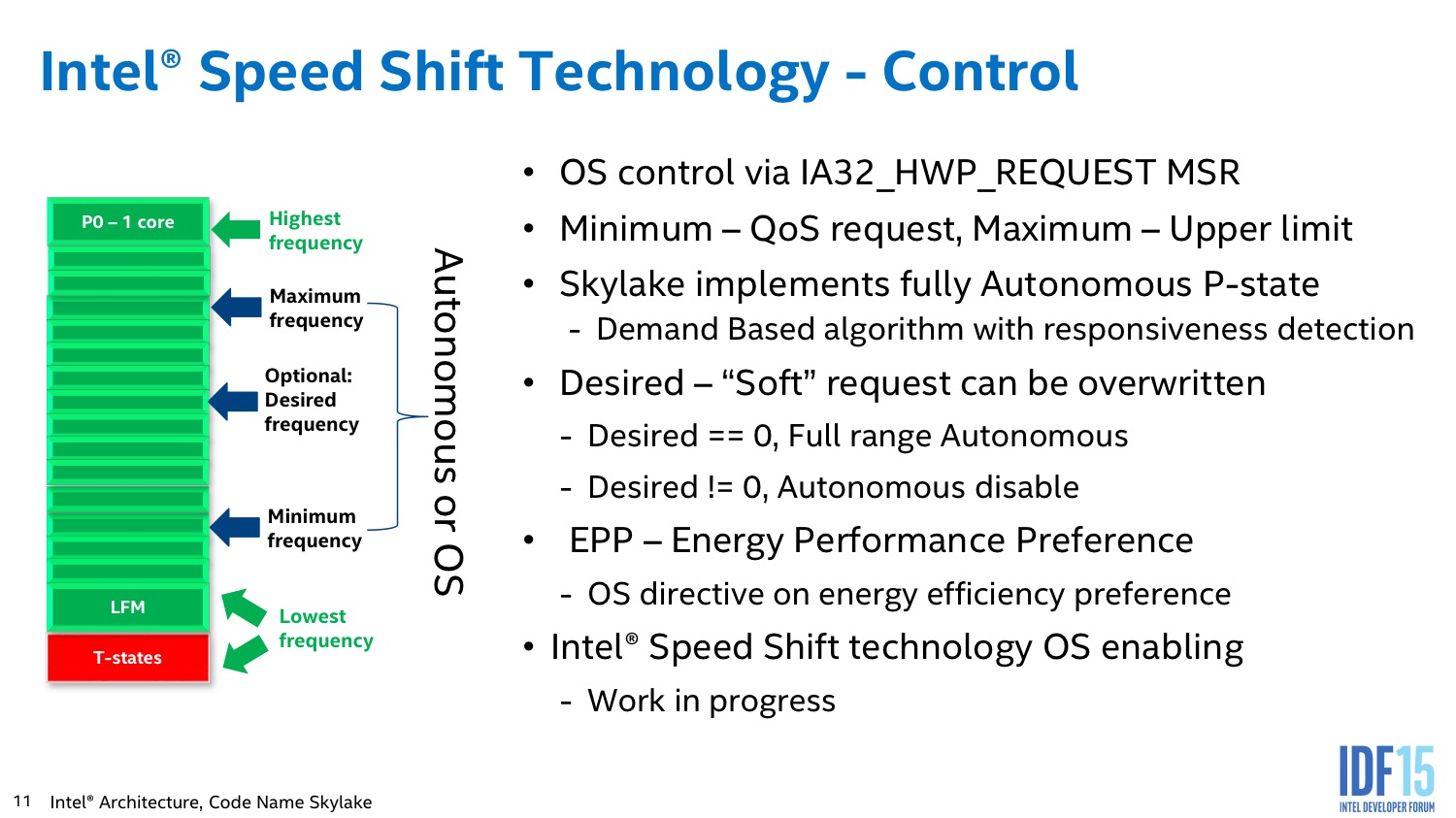

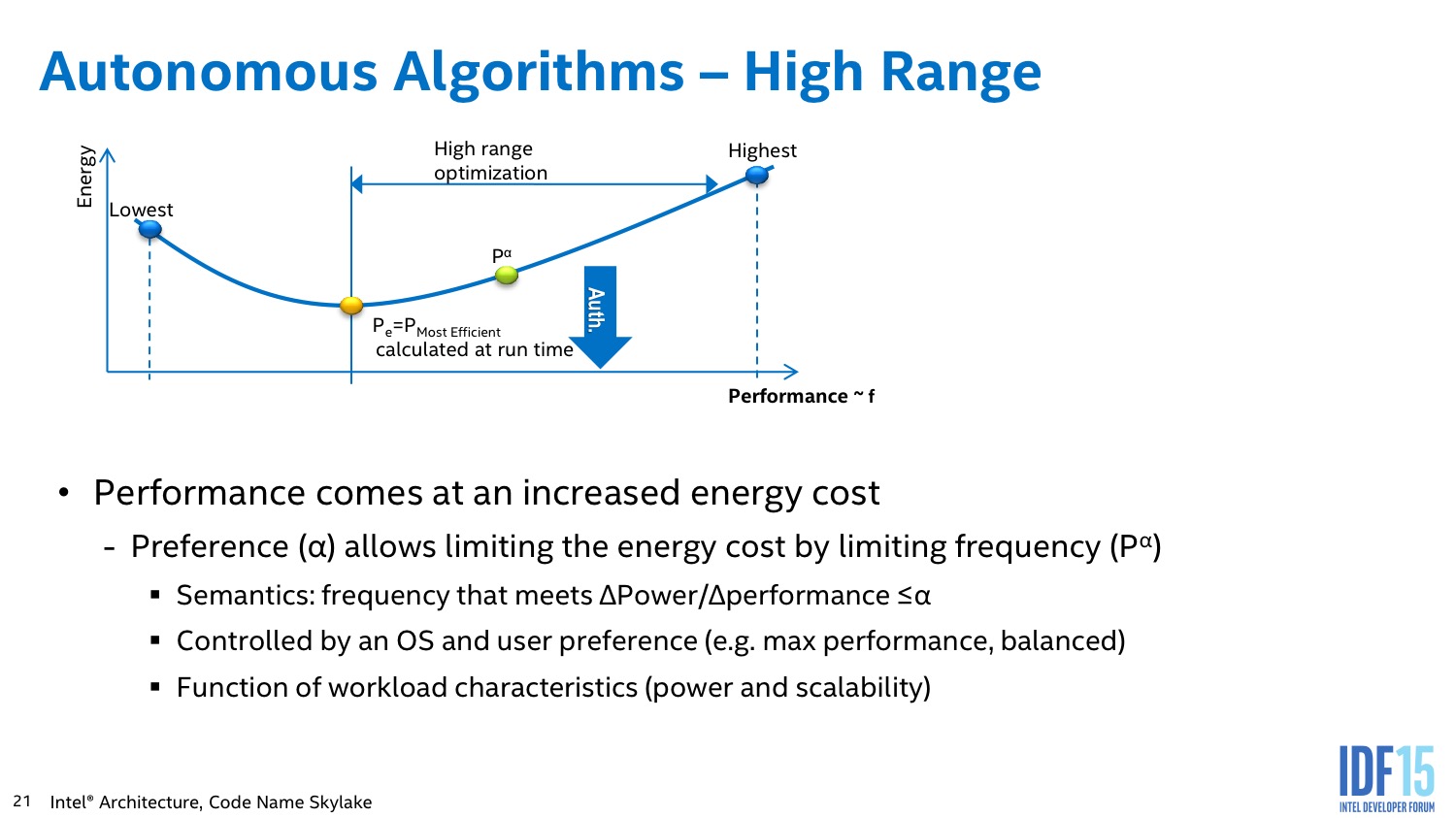

L'idée de Speed Shift est de changer la relation entre le système d'exploitation et le processeur. D'une, avec Speed Shift le processeur expose désormais la totalité des fréquences disponibles, y compris les modes Turbo gérés jusqu'ici de manière transparente. Ensuite, le système d'exploitation va donner une sorte d'indication globale pour indiquer s'il faut privilégier la performance ou l'économie d'énergie (remplaçant le concept des modes performance/balanced/etc que l'on retrouvait par exemple sous Windows 7, ainsi que le mode batterie/alimentation pour les portables). Enfin, par défaut le PCU est capable de gérer tout seul les P-States en choisissant automatiquement le mode qui semble le plus adapté à la volée et de manière complètement autonome.

Par dessus ceci, le système d'exploitation peut décider d'intervenir, mais cela se fait d'une manière nouvelle. En effet, le système définit une fréquence minimale ainsi qu'une fréquence maximale, laissant là encore au PCU une marge de manoeuvre pour optimiser automatiquement au mieux en fonction de la charge. Il est également possible de demander une fréquence précise, de manière optionnelle, mais cela se fait en plus des fréquences mini et maxi et n'est en rien garanti.

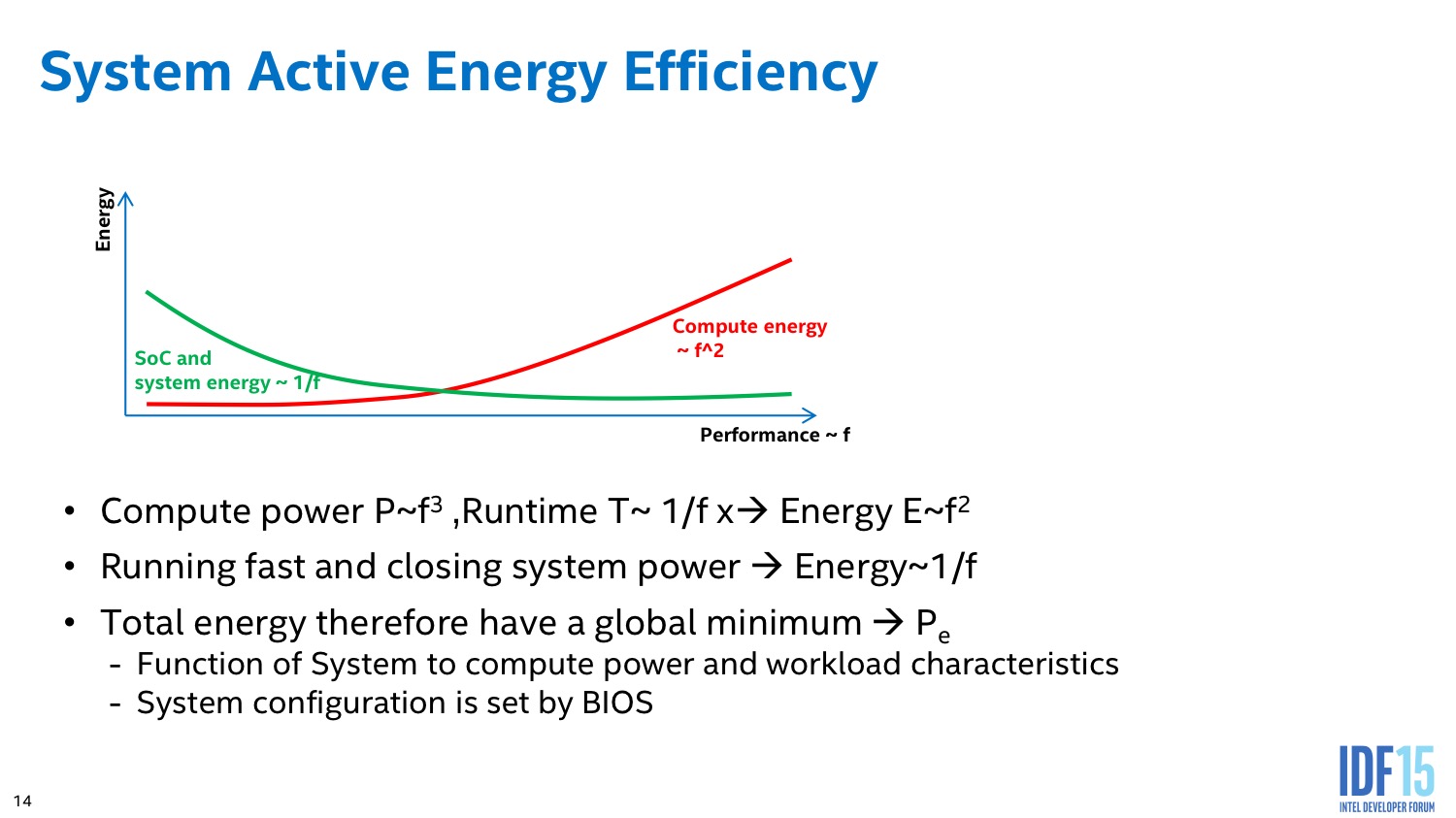

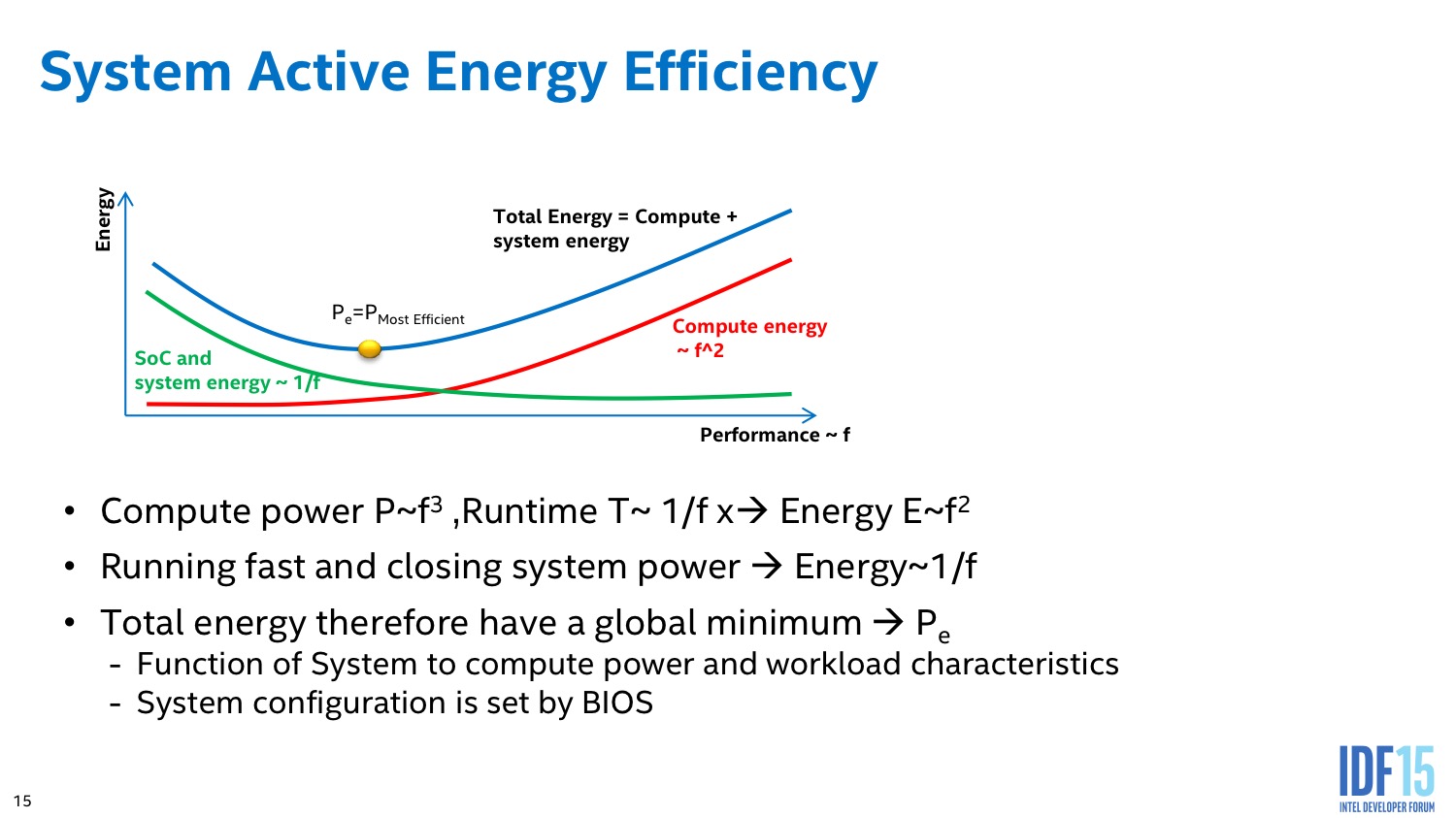

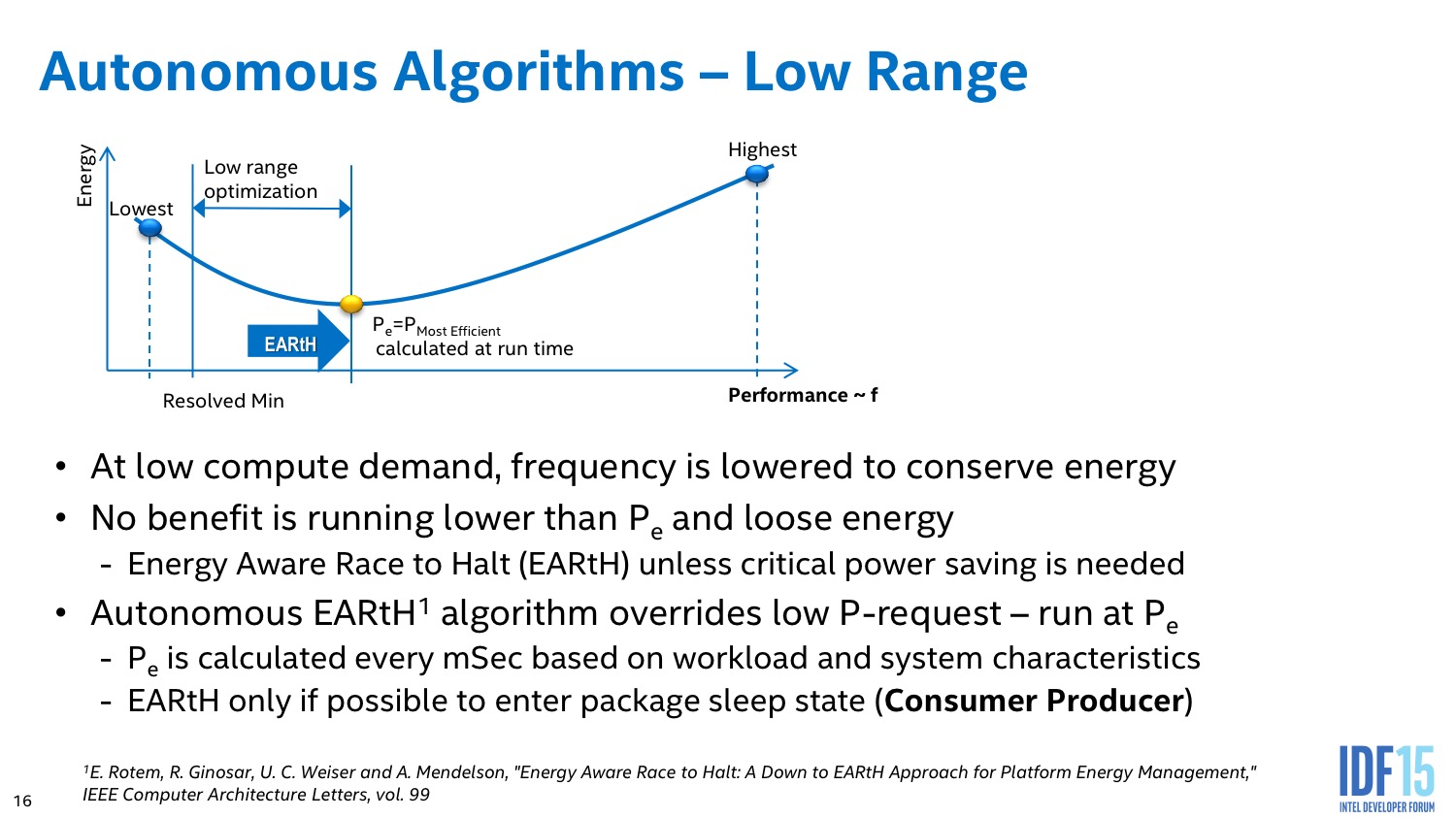

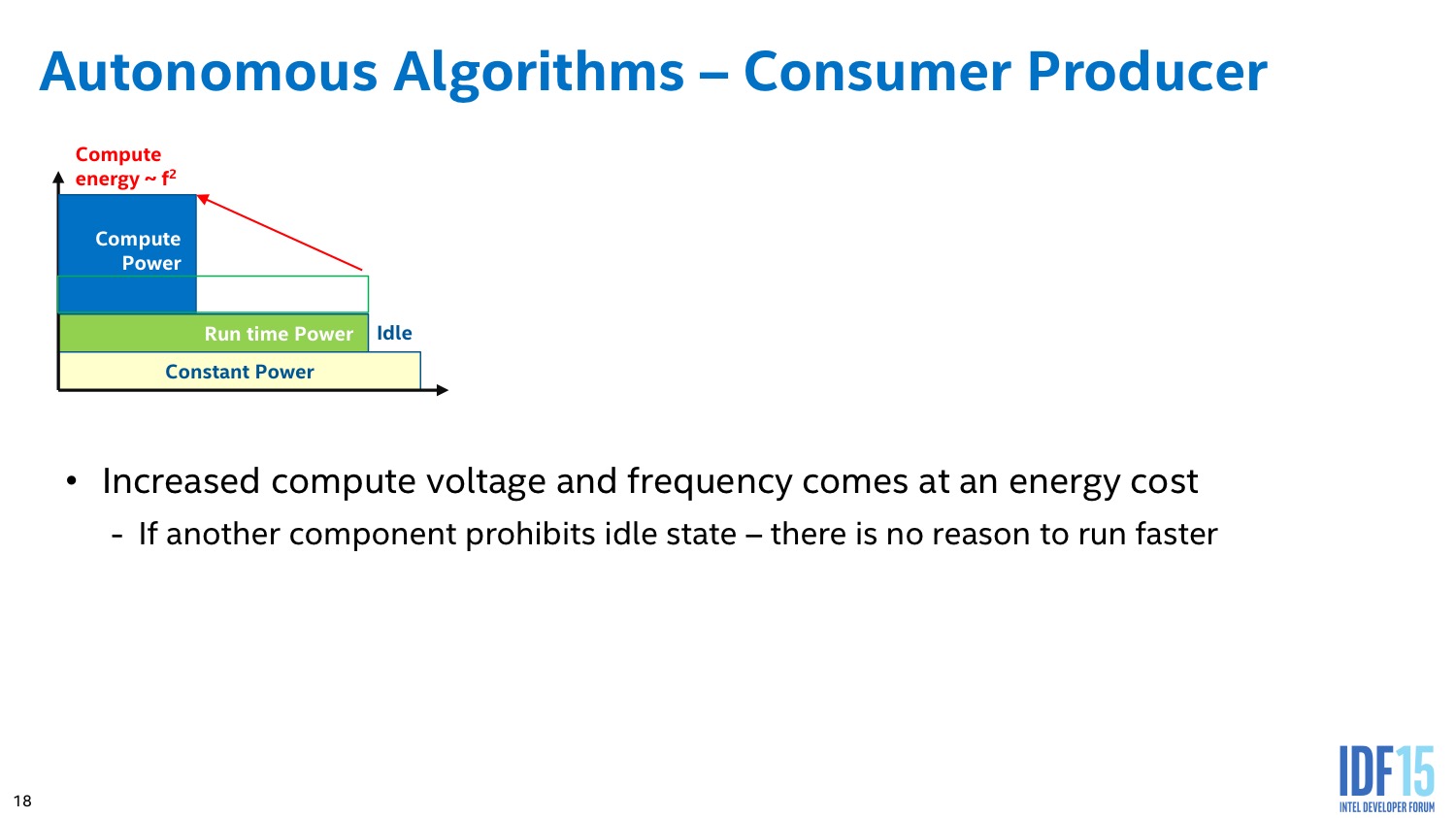

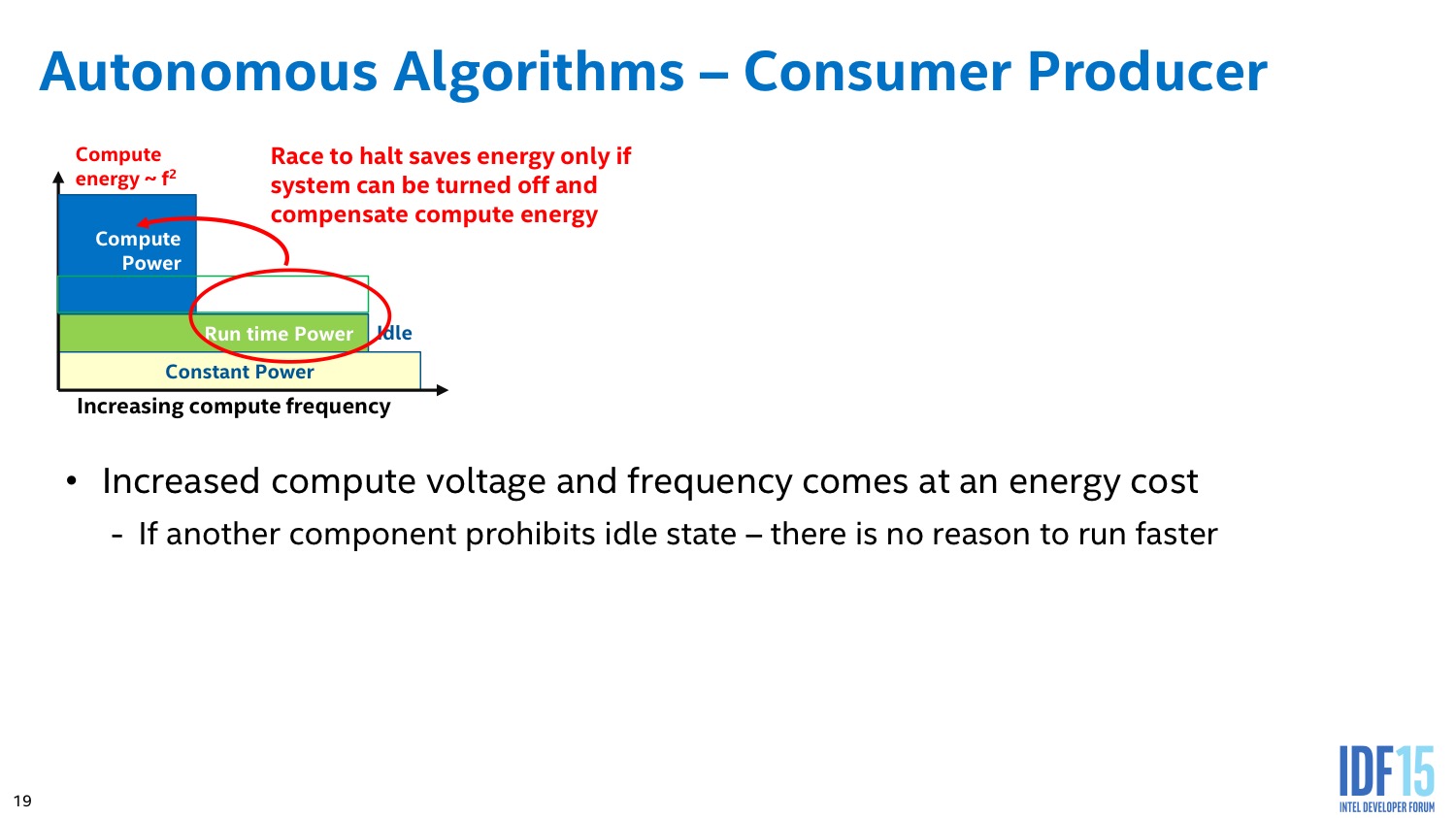

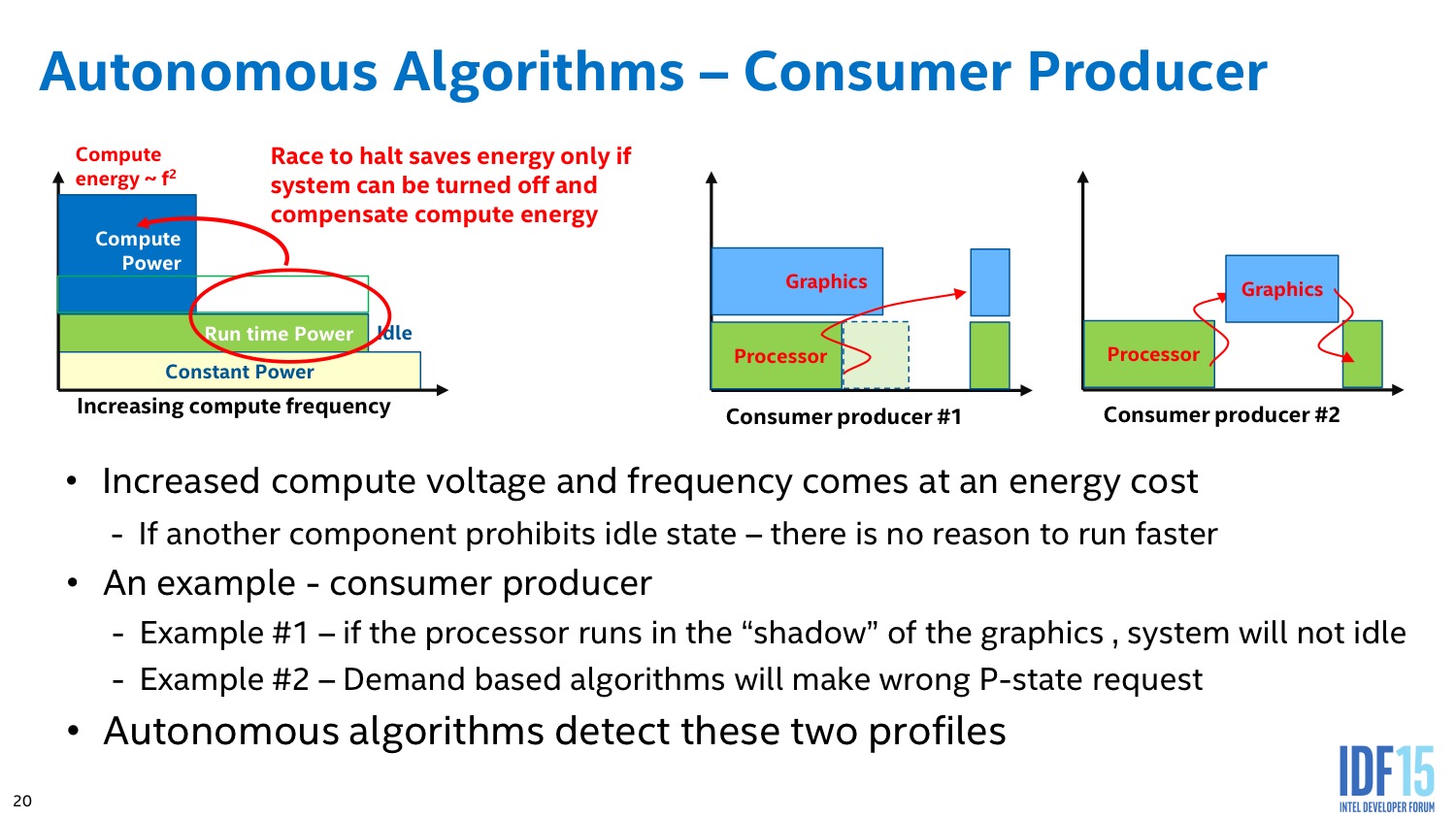

Intel implémente des algorithmes avancés dans son PCU qui tentent d'estimer en permanence s'il est plus intéressant de limiter la fréquence dans le cas d'une charge légère constante, ou au contraire de pousser la fréquence pour pouvoir éteindre le plus rapidement possible les unités et sauver de l'énergie au final.

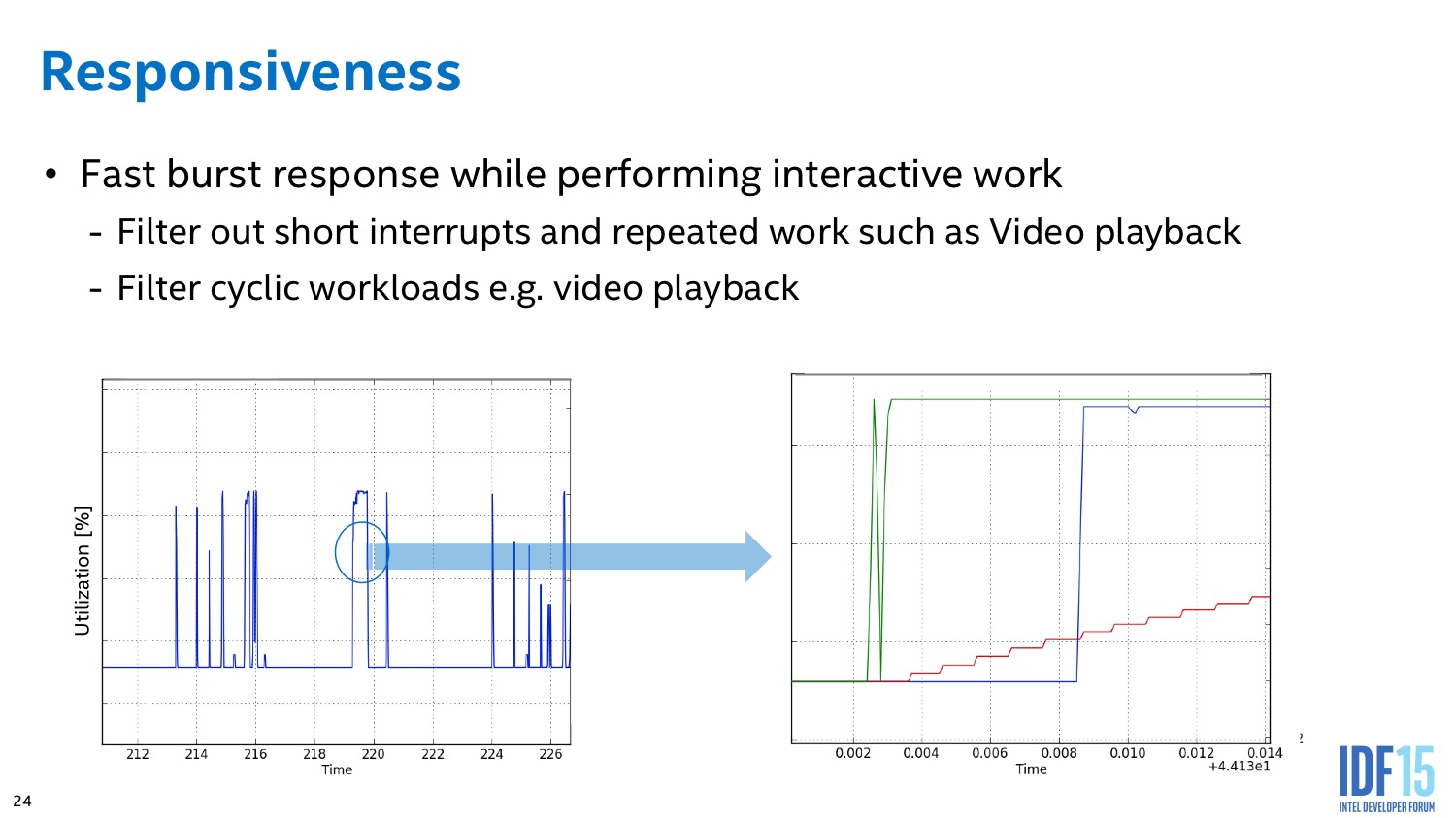

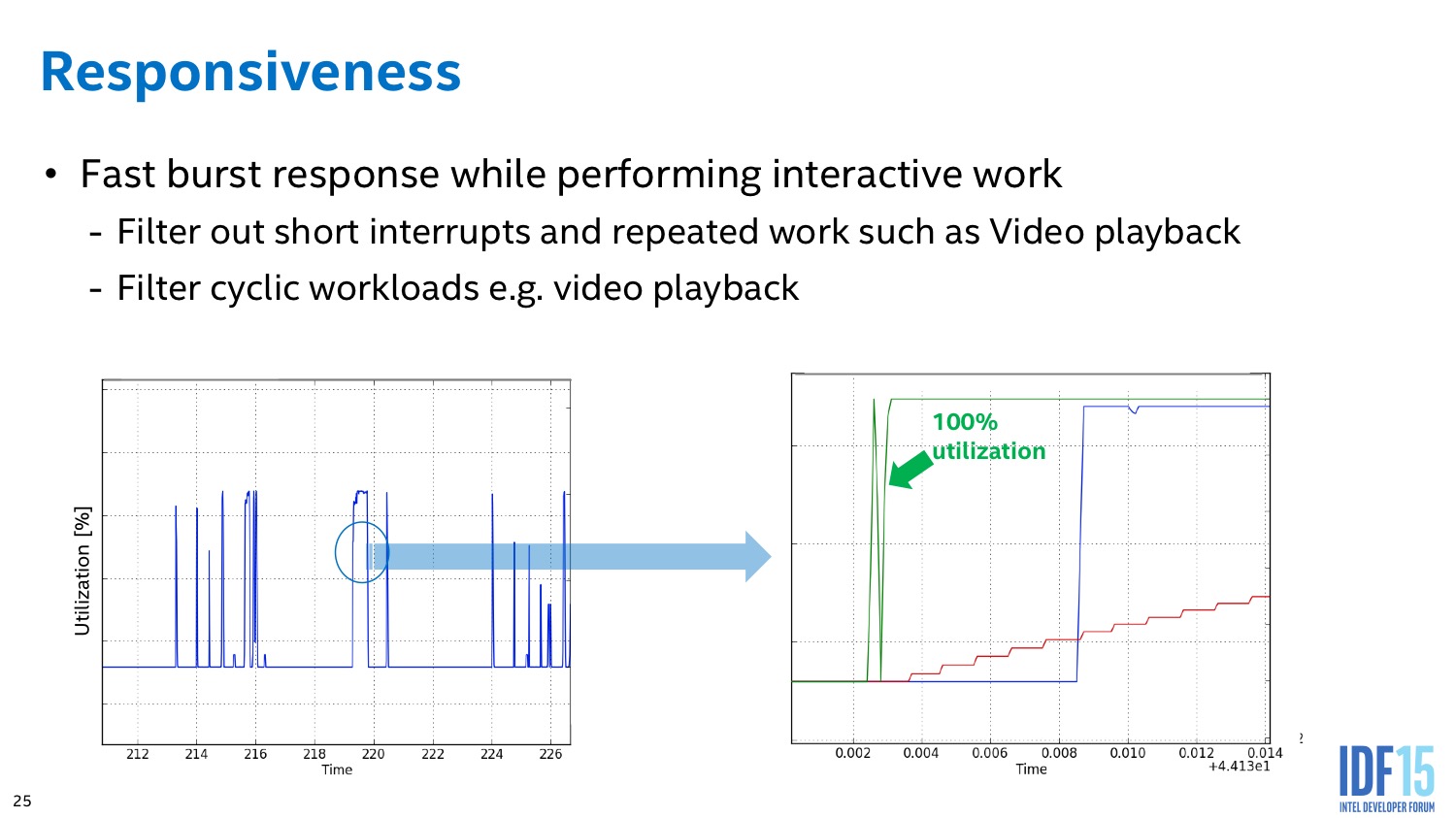

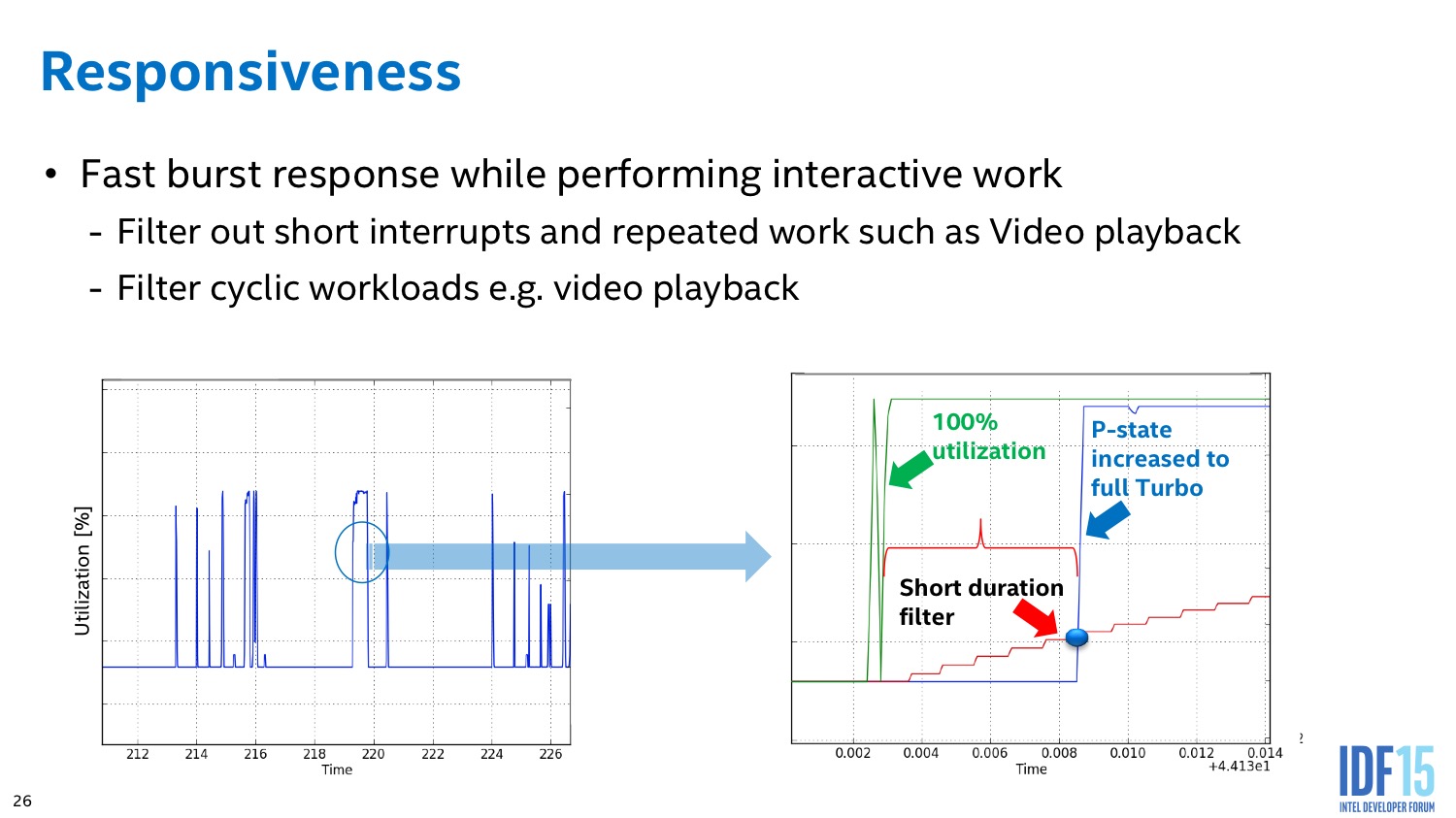

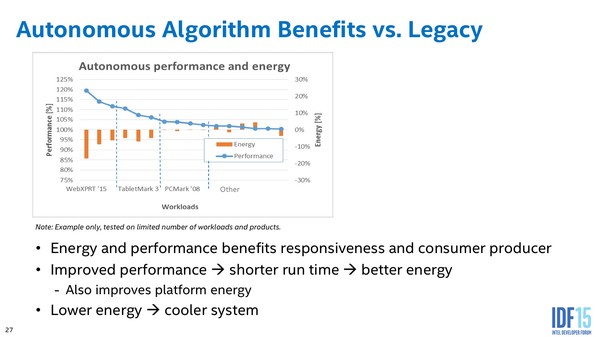

L'algorithme du PCU tente également de détecter les situations ou l'on interagit avec le système pour améliorer le côté responsif du système. L'idée de base telle que voulue par les concepteurs du système était de passer le plus rapidement possible en mode turbo lorsque l'on détecte une interaction (réveil, souris, etc) pour donner l'impression que le système est plus réactif. En pratique le PCU tente de détecter les charges typiques d'une interaction et utilise plusieurs systèmes pour filtrer des charges plus longues (lecture vidéo), ou tellement courtes qu'elles ne mériteraient pas que la fréquence augmente.

En pratique en tout cas,Intel indique être capable de réduire à la fois la consommation tout en ne sacrifiant pas sur les performances. Vous pouvez voir sur ce slide quelques résultats annoncés par le constructeur même s'il n'est pas rentré plus dans les détails !

Speed Shift changeant fondamentalement le mode d'interaction entre le processeur et système d'exploitation, on ne sera pas surpris d'apprendre que son support doit être explicite, et est donc aujourd'hui limité. Aujourd'hui, seul Windows 10 est capable de l'exploiter. Sur tous les autres OS, le fonctionnement reste à l'ancienne.

Il est intriguant de voir qu'Intel n'a pas encore publié de patch pour Linux pour y ajouter le support de Speed Shift. D'autres technologies de Skylake comme MPX ont en effet eu droit à un support dès janvier sous Linux. Malgré tout, l'idée de rénover le concept fort vieux des P-States est une excellente idée, laisser la main au processeur sur sa fréquence parait presque une évidence et il sera très intéressant de voir l'impact pratique qu'aura cette technologie sur la conservation de la batterie sur les versions mobiles de Skylake.

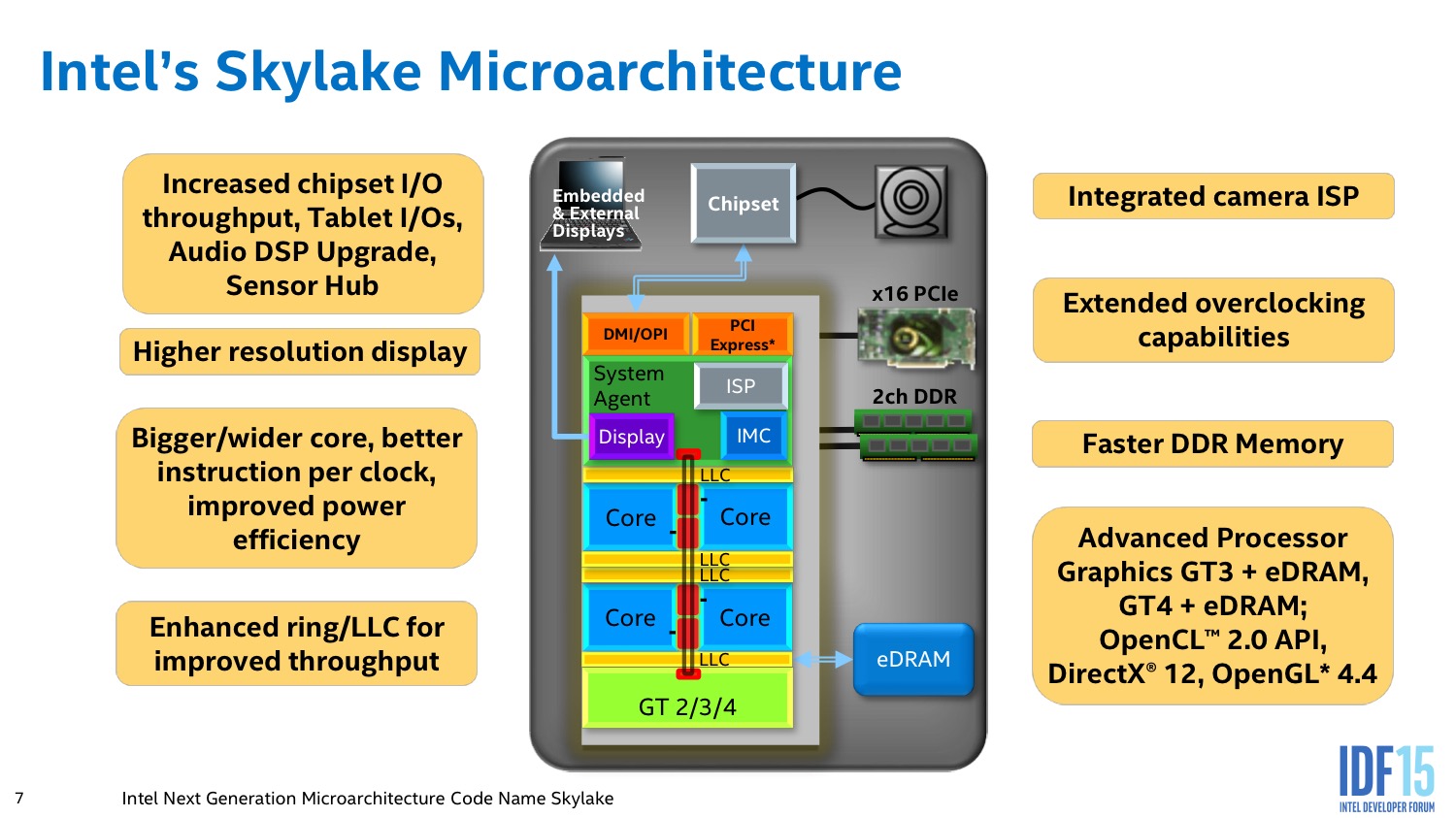

eDRAM, IVR, Chipset

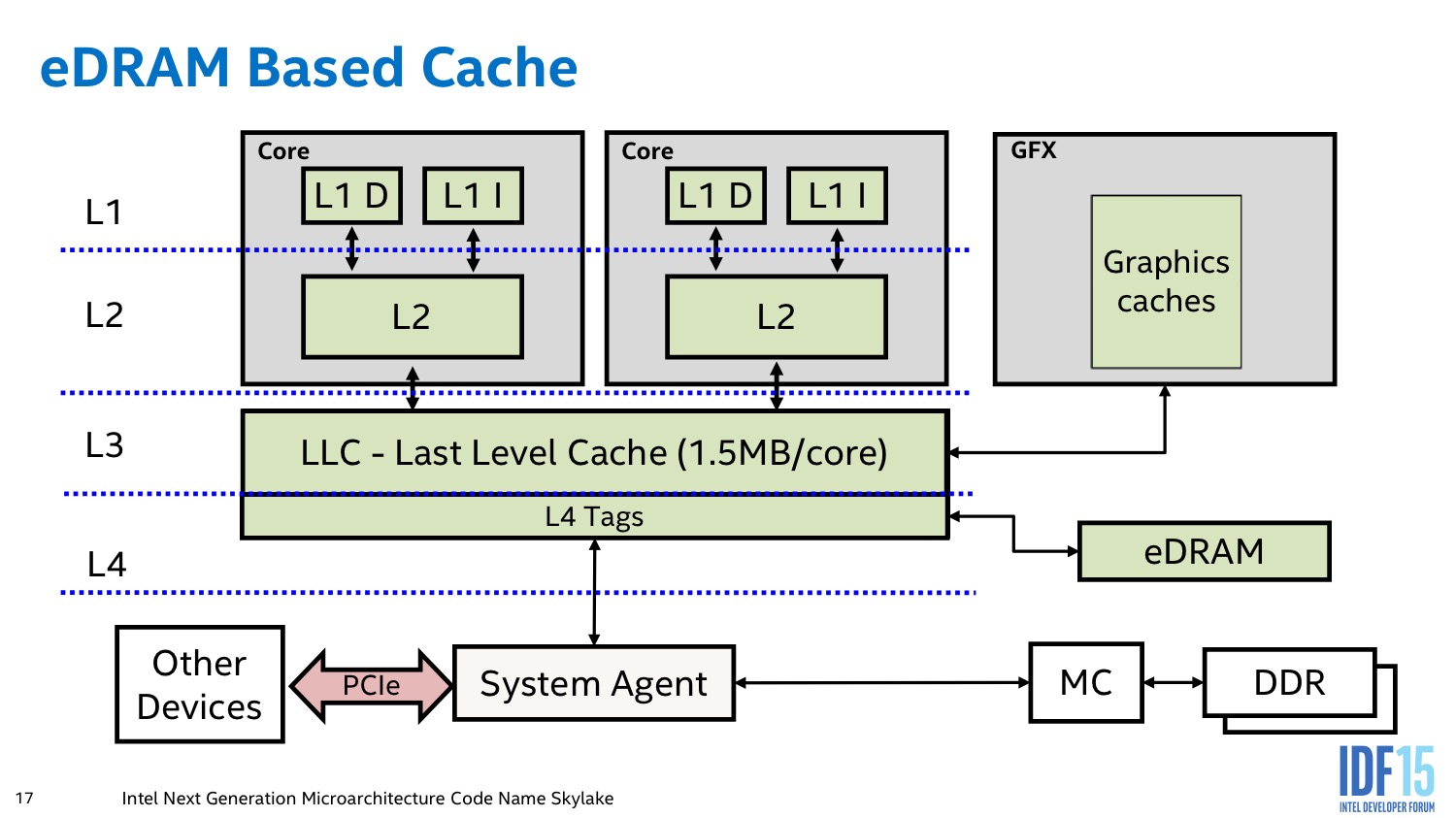

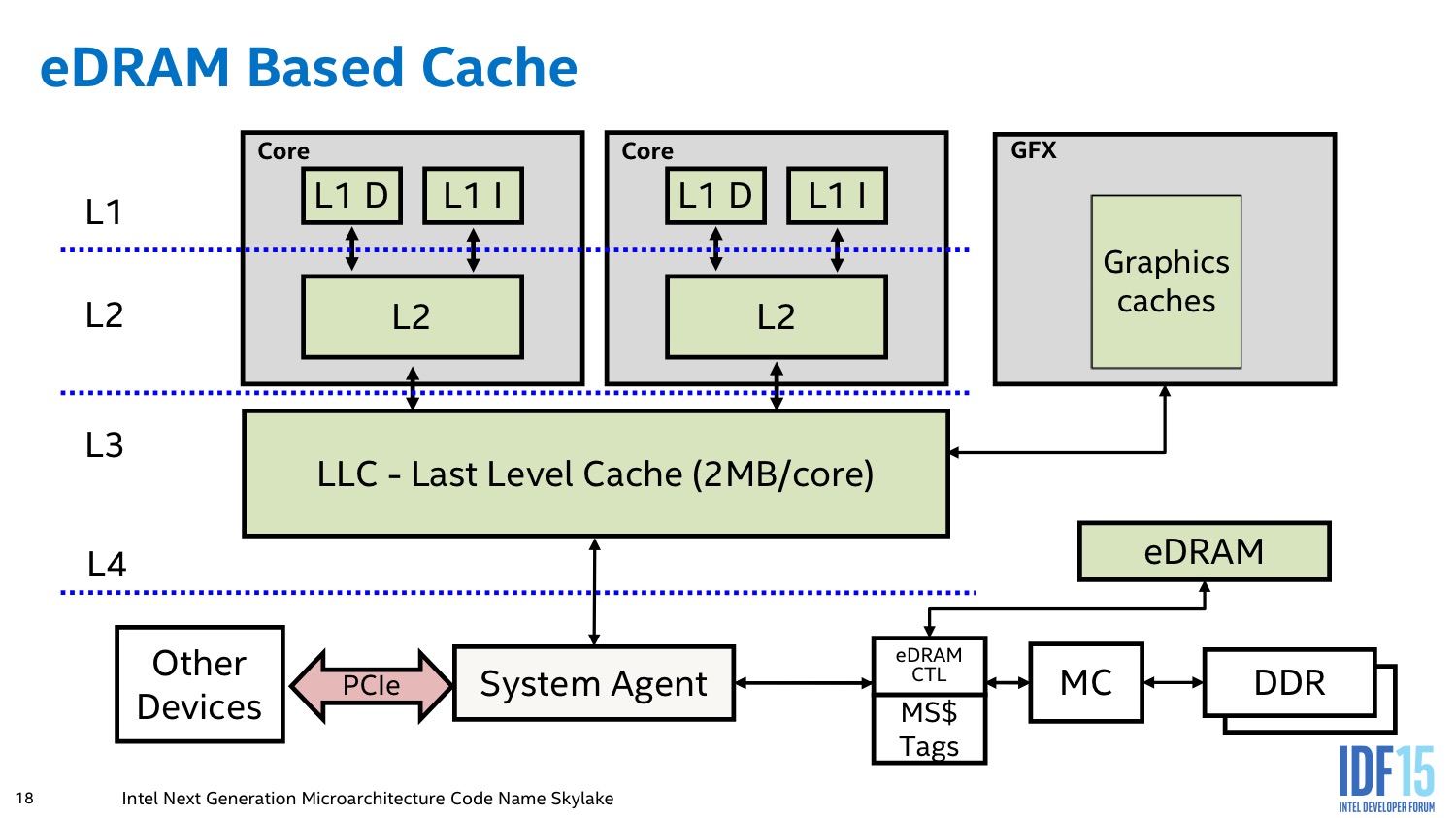

Un autre changement important concerne la manière dont la mémoire eDRAM est interfacée avec le processeur. Avec Broadwell par exemple, l'eDRAM est interfacée derrière le cache LLC et peut contenir de la mémoire utilisée par l'IGP ou par les coeurs mémoires (des tags dans le LLC marquent qui utilise quoi).

Avec Skylake l'eDRAM se retrouve placée entre le LLC et le contrôleur mémoire, s'intégrant de manière encore plus transparente dans la hiérarchie mémoire. En pratique ce changement permet de mettre en cache des données qui peuvent venir d'un peu partout. Le L4 peut ainsi contenir en cache des requêtes PCI Express ou du chipset.

Cette transparence est cependant débrayable dans le cadre d'une utilisation graphique. Le pilote graphique Intel dispose d'un mode d'accès spécifique qui lui permet de demander où il souhaite que soit mises en cache certaines informations. Il peut demander a ce que des informations soient stockées dans le L3, ou dans l'eDRAM au choix, ou au contraire nulle part. Des décisions que le pilote, selon Intel, est plus a même d'estimer correctement. L'impact réel de ce changement est difficile à évaluer même si potentiellement il devrait profiter aux utilisations non graphiques.

On notera sur la question de la suppression du régulateur de tension intégrée que les ingénieurs nous ont donné une réponse : la décision de les supprimer a été prise spécifiquement à cause des modèles 4.5W ou l'IVR était inefficace. Une « meilleure » solution, s'ils avaient eu plus de temps selon les ingénieurs d'Intel aurait été de supprimer l'IVR uniquement sur les modèles basse consommation et de les garder sur les autres. Un sous-entendu qui laisse penser que le constructeur pourrait opter pour cette séparation a l'avenir pour Cannonlake.

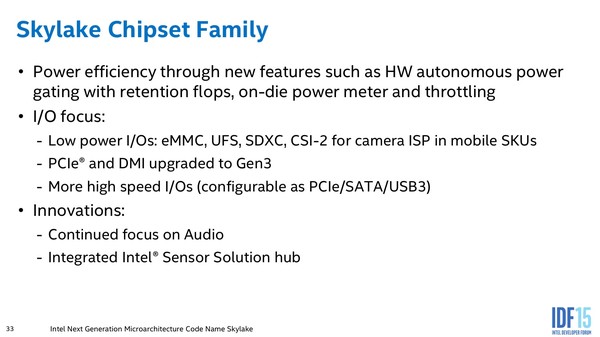

Notons pour terminer que le chipset, au delà des changements déjà évoqués dans notre article, propose une particularité originale : il est désormais capable d'entrer en mode throttling en cas de surchauffe. L'idée est surtout d'éviter la situation ou, a cause d'une surchauffe de la plateforme, le PCH pourrait mettre en péril le système. Intel gagne surtout un peu de marge pour les puces 4.5 et 15W qui incluent dans le package le PCH, jusque à côté du die cpu/graphique.