Les contenus liés aux tags AFDS et GCN

AFDS: FirePro W9000 et aperçu d'une carte biGPU

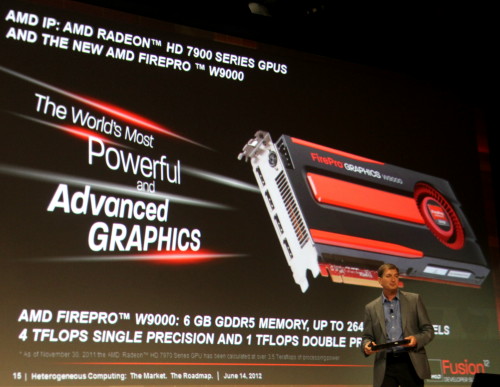

Lors de la keynote de clôture de l'AFDS, Mark Papermaster, Chief technology Officer (CTO) d'AMD, a présenté une future carte graphique professionnelle haut de gamme basée sur l'architecture GCN : la FirePro W9000.

Une présentation qui s'est faite tout d'abord à travers un slide qui présente une carte mono-GPU équipée de 4 sorties DisplayPort, de 6 Go de mémoire. Parmi ses spécifications AMD parle de 264.8 millions de pixels sans que nous n'ayons la moindre idée de ce à quoi ce chiffre correspond, le débit de pixels du GPU qui l'équipe étant plus de 100x supérieur. Pour le reste AMD mentionne une puissance de calcul de 4 Teraflops en simple précision et de 1 Teraflops en double précision, ce qui correspond à un GPU Tahiti tel qu'utilisé dans la Radeon HD 7970 mais cadencé à 1 GHz.

Marc Papermaster a ensuite indiqué qu'il allait nous montrer cette FirePro W9000, sauf que la carte qu'il a sortie était de toute évidence différente. Si elle affiche bien la marque FirePro à travers les divers stickers apposés sur ses 3 ventilateurs, il s'agit cette fois d'une carte bi-GPU, de toute évidence un dérivé FirePro de la future Radeon HD 7990. La présence de 6 puces mémoire pour chaque GPU à l'arrière de la carte confirme qu'il s'agit bien de 2 GPU Tahiti (dont le bus mémoire est de 384 bits) alors que les 2 connecteurs d'alimentation PCI Express 8 broches indiquent un TDP qui pourra monter à 375W (voire plus en dehors des spécifications PCIE officielles).

La conception d'une carte bi-GPU étant relativement complexe, il est peu probable qu'AMD prévoie des designs différents pour la FirePro par rapport à la Radeon HD 7990 dont nous pouvons donc supposer qu'il s'agit ici du système de refroidissement qui l'équipera. Contrairement aux designs bi-GPU habituels d'AMD, la turbine est abandonnée au profit de 3 ventilateurs axiaux qui refroidissent un large radiateur en aluminium à travers lequel nous pouvons distinguer de nombreux caloducs.

AFDS: AMD lance la FirePro W600

AMD profite de l'AFDS pour introduire la FirePro W600, qui est la première à reposer sur l'architecture GCN. Il s'agit d'une FirePro milieu de gamme, basée sur Cape Verde et donc dérivée des Radeon HD 7700. AMD ne précise pas les spécifications détaillées mais elles seront probablement proches de celles de la Radeon HD 7750 si ce n'est pour la mémoire vidéo qui passe de 1 Go à 2 Go.

La FirePro W600 est avant tout prévue pour gérer les murs d'écrans et propose pour cela 6 sorties mini-DisplayPort 1.2. Elle se contente de 75W et d'une alimentation via le port PCI Express et affiche un encombrement réduit sur un seul slot, de quoi faciliter l'intégration de deux cartes pour piloter 12 écrans.

AFDS: 1 Teraflops pour l'APU Kaveri

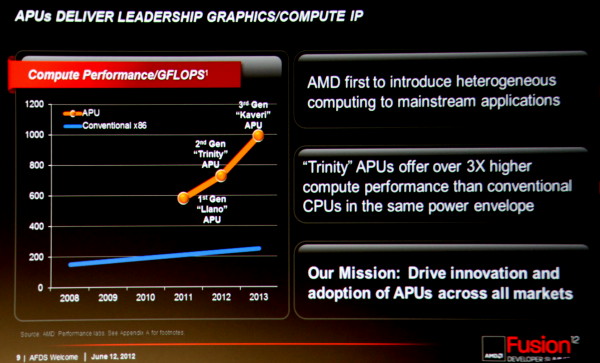

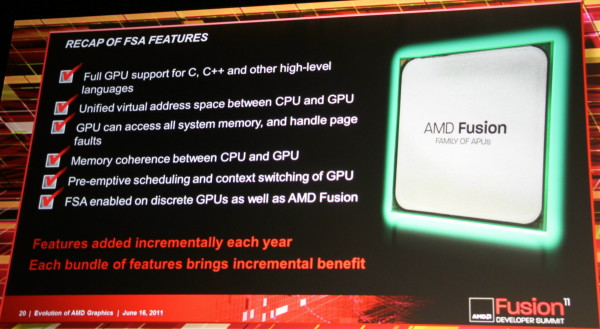

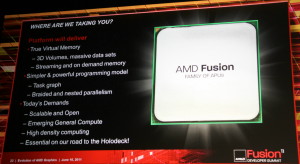

Dans la vision d'AMD concernant le calcul hétérogène, les APU jouent comment vous vous en doutez un rôle important, d'une parte parce qu'elles permettent de démocratiser la technologie et d'autre part parce qu'elles autorisent une communication plus efficace entre les cores CPU et GPU.

En 2013, l'APU Kaveri apportera de nouvelles évolutions importantes pour le calcul hétérogène et profitera en partie pour cela de l'architecture graphique GCN introduite dans les Radeon HD 7000. Si AMD ne rentre pas encore dans ces détails, les objectifs en termes de puissance de calcul ont été dévoilés lors de l'AFDS : 1 Teraflops pour l'ensemble CPU/GPU.

Par rapport à Trinity et l'A10-5800K qui culmine à 738 Gflops, il s'agit d'un gain de 35% qui proviendra en toute logique avant tout du GPU dont nous pouvons supposer qu'il passera de 384 à 512 unités de calcul. Notez que l'architecture GCN étant plus efficace que l'architecture VLIW4 de Trinity, les gains devraient être en pratique supérieurs à ce que ne laissent penser ces premiers chiffres.

AFDS: Retour sur le futur GPU d'AMD

Lors du dernier keynote de l'AFDS, Eric Demers, Chief Technology Officer pour la partie GPU chez AMD, est revenu sur la future architecture GPU qui a été présentée avec de très nombreux détails cette semaine, de manière à en mettre en avant les grandes lignes d'une manière simplifiée. Il a également été confirmé qu'AMD espérait lancer cette architecture à la fin de l'année, si le procédé de fabrication 28nm n'entrave pas ces plans.

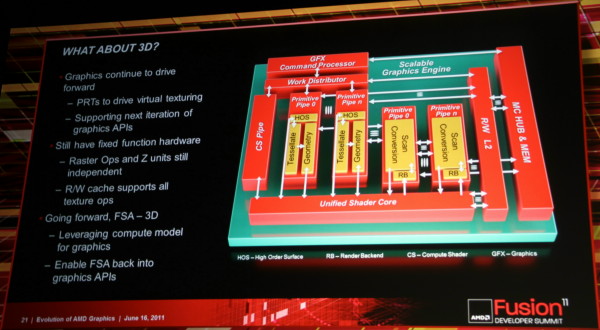

Eric a rappelé que l'évolution des GPUs ATI/AMD nous a fait passer d'une architecture au comportement vec4 + 1 vers une architecture vec5 à partir des Radeon HD 2900 puis enfin vers une architecture vec4 avec les Radeon HD 6900 qui sera déclinée dans de futurs GPUs milieu et bas de gamme ainsi que dans Trinity. Ces choix architecturaux s'expliquent par la présence de nombreuses opérations vec4 mais aussi scalaires dans le rendu graphique qui reste la tâche principale des GPUs. La flexibilité des unités de calcul de type MIMD/VLIW des derniers GPUs a permis de se passer du canal scalaire et de laisser le compilateur se charger de mixer toutes les opérations dans les 5 ou 4 canaux disponibles.

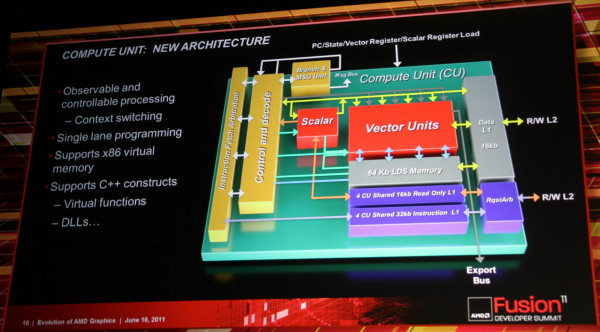

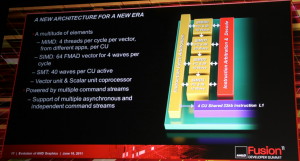

Avec sa future architecture, AMD a voulu conserver une organisation similaire. Si le modèle VLIW est abandonné, les blocs fondamentaux de ces GPUs vont garder ces 4 canaux, non pas pour exécuter des opérations vec4 mais pour conserver un ratio similaire et vu comme le plus adapté pour le graphique. Les tâches de type "compute" devenant de plus en plus importantes et affichant souvent une utilisation moindre des unités vec5 ou vec4, il fallait revenir à un modèle scalaire du point de vue du programmeur.

L'architecture proposée par AMD permet de combiner ces deux aspects en plaçant dans chaque Compute Unit non pas une grosse unité MIMD mais 4 plus petites unités SIMD indépendantes. Par ailleurs, AMD leur adjoint une unité scalaire qui sera destinée à éviter de monopoliser la puissance de calcul vectorielle par des opérations simples. Comme pour les blocs fondamentaux des GPUs actuels, chaque CU recevra 4 unités de texturing. Une CU est donc, sur le plan des unités d'exécution, très proche de ce qu'AMD appelle actuellement les SIMDs. C'est au niveau de l'exploitation de ces unités d'exécution que le changement est radical. Le GPU Cayman des Radeon HD 6900 peut d'ailleurs être vu comme une étape intermédiaire vers cette nouvelle architecture. Un côté hybride/prototype qui explique probablement son efficacité discutable.

Un autre aspect important de la nouvelle architecture est le multitâche puisque ces nouveaux GPUs seront capables de gérer différentes commandes simultanément ainsi que la priorité à donner à chacune d'elles. Tout ceci se passera au niveau du GPU et non au niveau du système d'exploitation.

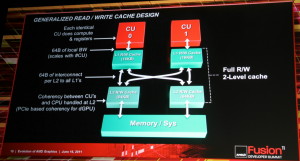

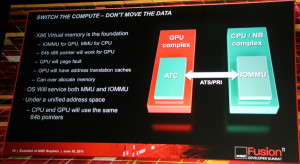

Le cache L2 utilisable en lecture et en écriture est la troisième grosse évolution. Il permet également l'existence d'un espace cohérent entre toutes les CUs ainsi qu'avec le CPU, que ce soit à l'intérieur d'un APU ou avec une carte graphique dédiée.

Ce cache L2 généralisé, le fonctionnement scalaire des unités de calcul, le support de l'espace mémoire virtuel x86 et du C++ vont faire exploser l'intérêt du GPU computing. Notez cependant que sur certains de ces points, AMD ne fait que rattraper le retard pris sur Nvidia.

Une interrogation importante que nous avons par rapport à cette nouvelle architecture est son efficacité énergétique. Comme nous avons pu le voir avec les Radeon HD 6970, elle était quelque peu en baisse. Augmenter le rendement d'une Compute Unit va donc faire progresser sa consommation relative. Si le procédé de fabrication 28nm permettra d'en faire baisser la consommation absolue, la question reste importante.

Nous avons pu nous entretenir avec Eric Demers à ce sujet et selon lui il s'agit d'un faux problème. Dans l'architecture actuelle, quand certaines lignes des unités vec4 ou vec5 ne sont pas utilisées, elles restent alimentées. Leur consommation est moindre que quand elles sont exploitées, mais elles gaspillent malgré tout beaucoup d'énergie. Ce gaspillage va disparaître avec la future architecture. En d'autres termes, nous nous approcherons probablement plus souvent de la consommation maximale des Compute Units, mais leur rendement énergétique serait dans tous les cas supérieur.

Enfin, nous avons demandé au CTO d'AMD s'il envisageait d'inclure à l'avenir dans les GPUs plus de CUs que ne le permet le TDP, tout en sachant qu'ils ne pourraient pas tous être exploités en rendu 3D (limités par PowerTune par exemple), mais en supposant qu'ils pourraient l'être dans le mode compute qui n'exploite pas certaines parties du GPU très gourmandes telles que les unités de texturing. Eric Demers nous a répondu qu'AMD envisageait effectivement cela et qu'une telle possibilité pourrait éventuellement être retenue à l'avenir, si les simulations le justifiaient, notamment pour un GPU qui viserait le HPC.