Les contenus liés au tag Haswell

Afficher sous forme de : Titre | Flux6 USB 3.0 et 6 SATA 6G pour Lynx Point

DirectX 11.1 pour Haswell

Une date pour Haswell

Focus: Haswell et mémoire transactionnelle

Ivy Bridge et Windows 8

IDF: Haswell : retour sur la partie graphique

En plus de ce que nous indiquions ce matin, nous avons glanés quelques détails supplémentaires sur la partie graphique intégrée à Haswell

D'abord au niveau du support des écrans. A l'image d'Ivy Bridge, trois framebuffers distincts sont gérés dans la puce pour piloter jusque trois écrans. Une possibilité qui réclame que deux ports DisplayPort soient présents sur la carte mère (voir notre test d'Ivy Bridge pour plus de détails) et qui n'est en pratique pas exploitée.

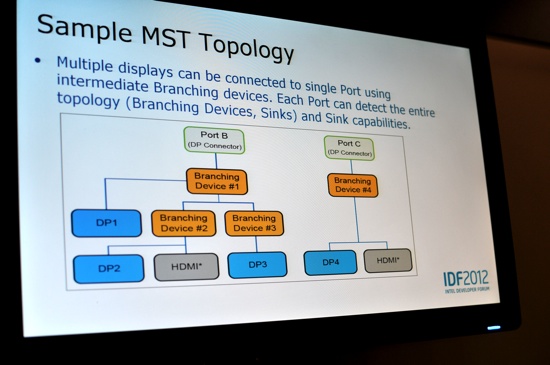

Haswell améliorera un peu la situation en supportant officiellement les hubs Display Port (MST pour Multi Stream Transport). Une démonstration d'Intel nous a montré l'utilisation de trois écrans simultanés connectés via trois hubs 2 ports chainés les uns aux autres (en pratique deux hubs 2 ports auraient suffit, Intel mettait simplement en avant pour sa démonstration sa gestion du chainage).

Sur ce schéma, on peut voir l'exemple d'une carte mère ou six écrans (4 DP et 2 HDMI)sont connectés sur deux ports Display Port. Attention cependant : s'il est possible de connecter plus de trois écrans, en pratique seuls trois images distinctes peuvent être générées côté GPU. Intel met simplement en avant avec ce schéma la possibilité d'effectuer du mirroring. Intel n'est pas le premier a gérer le support des hubs MST, AMD par exemple le propose depuis les HD 6000. Seul problème, ces hubs sont encore aujourd'hui introuvables. Rayon d'espoir sur ce point : selon notre interlocutrice, le modèle utilisé (basé sur un contrôleur ST Micro) pour la démonstration sera réellement disponible avant la fin du mois !

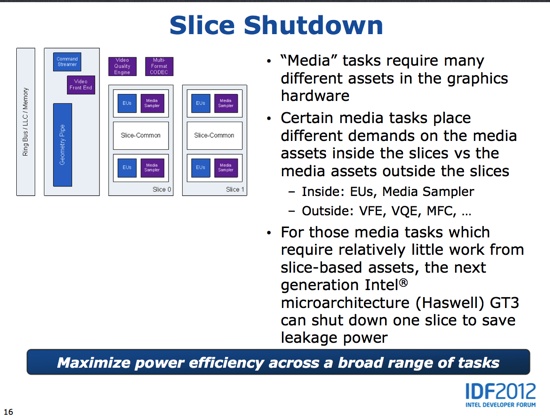

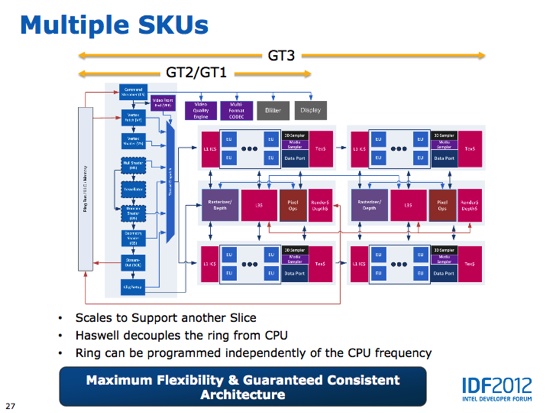

Terminons avec quelques détails supplémentaires sur les coeurs graphiques proprement dits. D'abord, une des particularités de la version GT3 de l'IGP est qu'elle dispose de deux partitions indépendantes, Intel les appelle «slice». L'intérêt de ce découpage est que dans le cas d'une charge graphique «légère», Haswell peut désactiver complètement l'un de ses slices pour limiter la consommation, une fonctionnalité qui a été ajoutée dixit le présentateur de la conférence pour les Ultrabook. Une confirmation du fait que l'on devrait retrouver ce GT3 dans des SKUs mobiles !

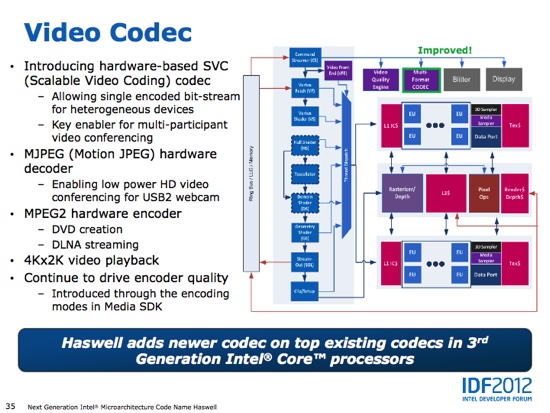

Enfin, Intel a ajouté quelques détails sur la partie codec de son IGP. On trouve quelques ajouts qui visent principalement l'accélération de la vidéo conférence. D'abord, l'encodeur H.264/AVC (connu sous le terme marketing QuickSync, voir ici) gère désormais la version «Scalable» du format. Il s'agit d'une extension du H.264 adaptée à la transmission de vidéo en ligne qui rajoute une notion de robustesse, le format peut en effet continuer a décoder une version dégradée de la vidéo en cas de fluctuation de la bande passante par exemple. Deux autres formats sont également gérés, le MPEG2 en encodage et le MJPEG en décodage. Dans les trois cas, le but est le même : ces formats serviront à accélérer des applications de type vidéo conférence (avec la possibilité d'améliorer le streaming également dans le cas du SVC).

IDF: Haswell : premiers détails !

Si la Keynote n'a pas été l'occasion de grandes annonces, les sessions techniques de l'IDF sont toujours beaucoup plus riches en détails ! Une première session de la matinée était dédiée à l'architecture d'Haswell, celle qui prendra place dans les remplaçants d'Ivy Bridge.

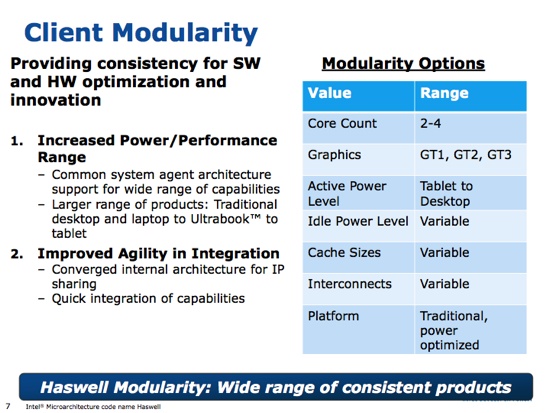

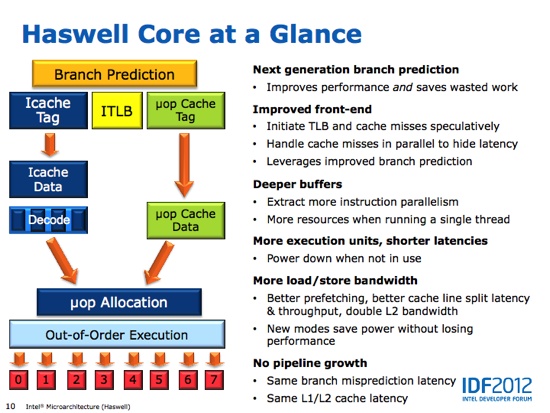

D'abord dans les grandes lignes, trois versions seront disponibles. Outre la version desktop et mobile, une version spécifique deux coeurs dédiée aux ultrabook sera également au programme. Différence principale avec la version mobile, elle intégrera (au sein du package) directement le chipset, pour un TDP de 15 watts (Intel n'ayant pas précisé si la version sous les 10 watts dont nous parlions précédemment intègrera également le chipset).

La modularité est le maitre mot utilisé par Intel pour Haswell. Outre le nombre de cores qui variera de deux à quatre, on trouvera trois coeurs graphiques distincts.

La nouveauté vient de l'arrivée de GT3, une troisième option graphique qui double ce qu'Intel appelle le slice. On trouvera donc deux blocs de rasterisation, de Z, de Stencil et de blending en plus des unités de calculs doublées. La partie en amont du GPU a été redimensionnée en fonction pour pouvoir gérer ces blocs supplémentaires. La présence du bloc mémoire additionnel a été éludée dans la présentation.

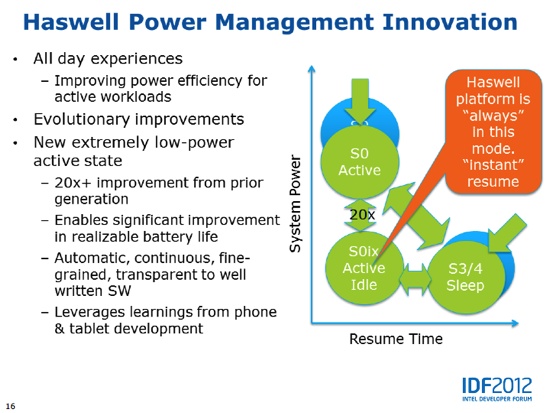

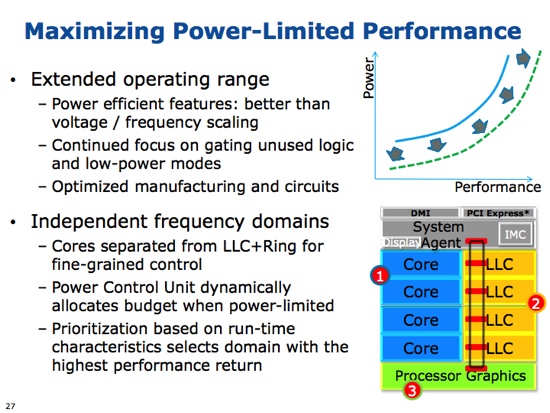

Du côté de la gestion de l'énergie, la plateforme gère les états SOix (1, 2 et 3) notamment supportés par Microsoft pour Windows 8 sous le nom de Connected Standby . L'intérêt de ces états est de proposer une plus grande finesse dans la gestion de l'économie d'énergie avec la possibilité de sortir de ces modes de veille avancés en 100 micro secondes, 3 milli secondes et 300 milli secondes (pour SOi 1, 2 et 3 respectivement).

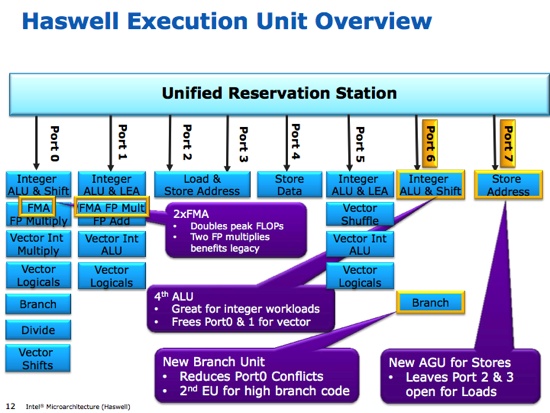

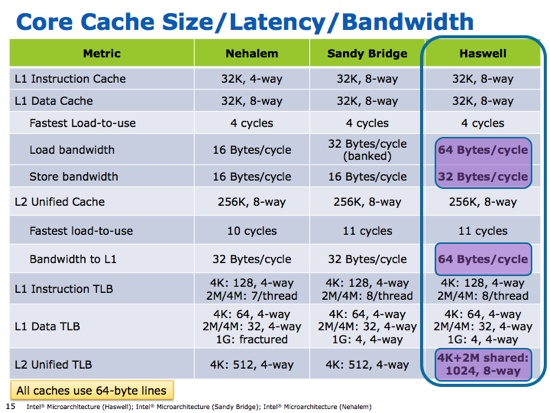

Comme nous l'indiquions précédemment, Intel a effectué quelques changements dans son architecture CPU. D'abord du côté des instructions par cycles, deux ports sont ajoutés ce qui permet au moteur OoO de traiter jusque 8 instructions par cycle. Deux ports peuvent être utilisés pour les instructions FMA (A=A+BxC en virgule flottante), doublant leur capacité théorique de traitement.

Les modifications ne s'arrêtent pas là avec des changements (non documentés) sur l'unité de prédiction de branchements et une augmentation de la taille de multiples buffers.

Intel est revenu sans plus de précisions sur le support de la mémoire transactionnelle, avec TSX. Nous avions pour rappel parlé de cette technologie en détails dans cet article. D'autres détails devraient être dévoilés dans des sessions techniques sur lesquelles nous reviendrons bientôt.

Dernier point notable au niveau de la PCU, Intel indique que le ring bus et la mémoire cache font désormais partie d'un plan d'alimentation complètement séparé.

Des premiers détails plutôt alléchants pour ces puces. Leur arrivée étant toujours prévue pour le second trimestre 2013.

Quelques détails sur Haswell-EP/EN

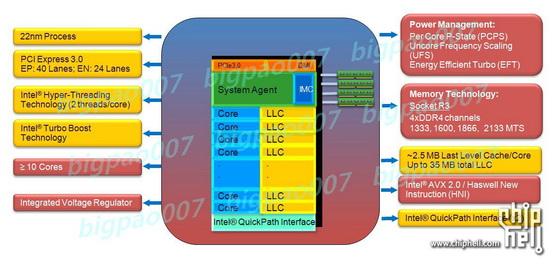

Nos confrères de CPU-World reviennent sur quelque slides qui ont été publiés sur le forum Chiphell et qui offrent quelques détails sur Haswell-EP/EN, la déclinaison Xeon bi-socket de l'architecture Haswell.

Côté caractéristiques on notera tout d'abord, comme nous l'avions indiqué un peu plus tôt, l'arrivée de la mémoire DDR4 sur cette plateforme, toujours gérée sur quatres canaux. Les puces pourraient disposer de plus de 10 curs (jusque 14 ?) avec jusque 35 Mo de cache commun, soit un maximum de 2.5 Mo/coeur.

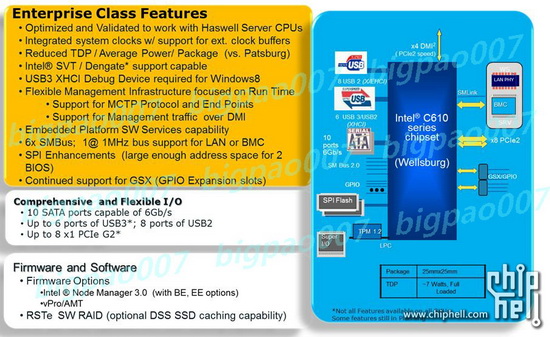

Côté chipset, le C610 (Wellsburg) ferait suite à l'actuel C602 (Patsburg) et l'on noterait parmi les nouveautés la gestion de dix ports Serial ATA 6 GB/s ainsi que l'introduction d'un contrôleur USB 3.0 gérant 6 ports en simultanée. Rappelons que si Haswell est attendu dans sa déclinaison classique pour 2013, cette version haut de gamme EP/EN n'est elle pas attendue avant 2014.

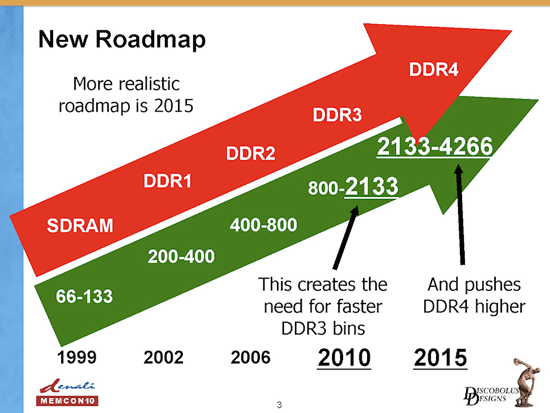

La DDR4 en 2014 pour Intel ?

Selon VR-Zone , Intel pourrait adopter la DDR4 dès début 2014 au sein de la plate-forme Haswell-EX. Destinée aux serveurs, cette plate-forme utilisera l'architecture Haswell 22nm qui sera introduite en 2013 sur LGA 1150, mais ira plus loin puisqu'il pourrait y avoir jusqu'à 16 curs par Socket, soit un besoin en bande passante énorme.

Côté desktop il ne faut toutefois pas attendre la DDR4 avant 2015 puisque la plate-forme LGA 1150 destinée à accueillir les Haswell au cours du premier semestre 2013 en restera à la DDR3. Broadwell, qui est un "tick" d'Haswell, c'est-à-dire une architecture proche mais portée sur un nouveau process 14nm, devrait a priori conserver cette infrastructure et donc la DDR3. Il faudra donc attendre la suite prévue pour 2015 pour un passage en DDR4. En attendant afin de satisfaire les besoins de l'IGP en terme de bande passante Intel aurait pour rappel l'intention de faire appel à un cache L4.

Un cache L4 pour Haswell ?

Alors que les Ivy Bridge ne sont pas encore lancés, les rumeurs circulent déjà sur les puces qui les remplaceront. Prévus pour le second trimestre 2013, les Haswell apporteront une nouvelle architecture sur le process 22nm du constructeur (un "tock" dans la nomenclature Intel, Ivy Bridge étant un "tick", une architecture proche de la précédente sur un nouveau procédé de fabrication).

Un certain nombre de détails sur ces nouveaux processeurs avaient déjà été dévoilés, souvent officiellement par Intel. Par exemple le jeu d'instruction AVX2 qui sera supporté, ou encore une démo fonctionnelle à l'IDF en septembre dernier. D'autres détails plus récemment avaient filtrés non officiellement, y compris le support de DirectX 11.1.

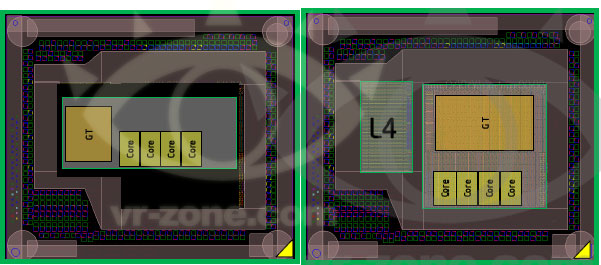

L'information publiée aujourd'hui par VR-Zone est cependant plus intrigante puisqu'elle évoque un éventuel quatrième niveau de cache pour Haswell. Ce quatrième niveau de cache pourrait prendre place sous la forme d'une puce annexe à l'intérieur du packaging, un système qui n'est pas sans rappeler la mémoire additionnelle ajoutée au GPU de la Xbox 360 par exemple. Selon nos informations, le die stacking aurait été également envisagé par Intel.

Disposer d'un quatrième niveau de cache fait sens puisqu'il permet de limiter les problèmes que l'on rencontre lorsque l'on partage une bande passante mémoire et un cache de dernier niveau entre un processeur et un GPU. Un problème que nous avions mis en évidence lors de notre test de Sandy Bridge, sans savoir à l'époque si cela était lié à la gestion d'énergie ou au partage du cache de dernier niveau (la seconde option nous ayant été indiquée comme la plus probable il y a deux semaines de cela). Un tel cache permettrait d'améliorer en prime la rapidité des accès mémoire graphiques, un des plus gros handicaps actuels des GPU intégrés aux CPU.

Quid de la taille et de la rapidité ? Nos confrères ne se prononcent pas mais différentes rumeurs qui nous sont parvenues font l'état de prototypes disposant de 128 Mo de cache L4. Rien ne dit cependant que c'est cette configuration qui sera retenue au final par Intel. De la même manière, tous les SKU ne devraient pas être équipés de ce quatrième niveau de mémoire cache cependant, les modèles desktop quad core haut de gamme (équipés du GPU le plus performant) seraient concernés par cette nouveauté en priorité selon nos confrères. Intel dispose d'une certaine flexibilité dans le domaine et ne manquera certainement pas l'occasion de segmenter sa gamme sur ce point.