Les contenus liés au tag Process

Afficher sous forme de : Titre | FluxIntel grave en 22nm

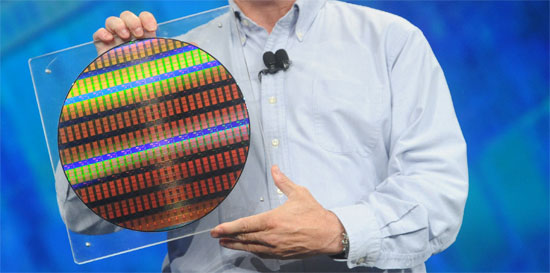

Intel a profité de lIDF pour montrer un wafer de puces SRAM gravées en 22nm. Il sagit des premières puces fonctionnelles au monde basées sur cette finesse de gravure, et comme dhabitude cest la SRAM qui est utilisée pour linaugurer. La puce intègres pas moins de 2.9 milliards de transistors.

Si tout se passe comme prévu, les premiers processeurs utilisant cette technologie devraient voir le jour courant 2011. Conformément au « tic-toc », il sagira dun die-shrink de larchitecture Sandy Bridge qui sera introduite lan prochain en 32nm.

Le 32nm d'Intel en route

Après avoir annoncé en juillet 2007 avoir gravé une puce de SRAM en 32nm, Intel indique quil est désormais arrivé au terme de la phase de développement de sa gravure en 32nm. Il sagit donc maintenant de passer à la phase de production, avec pour objectif de lancer la production en volume au quatrième trimestre 2009.

Après avoir annoncé en juillet 2007 avoir gravé une puce de SRAM en 32nm, Intel indique quil est désormais arrivé au terme de la phase de développement de sa gravure en 32nm. Il sagit donc maintenant de passer à la phase de production, avec pour objectif de lancer la production en volume au quatrième trimestre 2009.

Conformément au désormais célèbre « tic-toc » dIntel, le 32nm sera dans un premier temps utilisé pour un dieshrink de larchitecture actuelle. Le Nehalem 32nm, nom de code Westmere, devrait donc débarquer dans un an environ. Il sera suivi un an plus tard par une nouvelle architecture, toujours en 32nm, Sandy Bridge. Il intégrera lAVX (Advanced Vector Extension), qui nest ni plus ni moins que le successeur du SSE. Les registres passeront de 128 à 256 bits et permettra de travailler sur 3 opérandes, une idée qui sera également intégrée dans le SSE5 dAMD et qui permettra daller plus loin dans la fusion CPU/GPU.

IBM: 1ère cellule de SRAM 22nm

IBM annonce avoir fabriqué la plus petite cellule de SRAM du monde, gravée en 22nm (la longueurs des portes étant inférieure à 25nm) en partenariat avec AMD, Freescale, ST, Toshiba et l'University of Albany's College of Nanoscale Science and Engineering.

IBM annonce avoir fabriqué la plus petite cellule de SRAM du monde, gravée en 22nm (la longueurs des portes étant inférieure à 25nm) en partenariat avec AMD, Freescale, ST, Toshiba et l'University of Albany's College of Nanoscale Science and Engineering.

Si sa taille de 0,1micron² s'explique par sa simplicité, elle ne dispose que de six transistors, il faut souligner qu'elle a été réalisée avec des outils de production conventionnels (immersion lithographique de type high-numerical-aperture) sur un wafer de 300mm alors que ce type de record est souvent atteint avec du matériel non standard.

C'est donc une bonne nouvelle pour IBM et ses très nombreux "partenaires" parmis lesquels on retrouve aussi Infineon, Samsung ou encore Chartered Semiconductor mais en ce qui concerne l'utilisation du 22nm pour les CPUs AMD, il ne faut pas s'attendre à quoi que ce soit avant 2012 environ dans l'hypothèse la plus optimiste.

Chartered signe avec IBM pour le 22nm

Chartered Semiconductor, membre de l'IBM Alliance for 32nm bulk CMOS process technology development a annoncé qu'il travaillerait également avec Big Blue sur le 22nm. Depuis 2002, les deux firmes ont déjà collaborés ou collaborent pour le développement de la gravure en 90nm, 65nm, 45nm et 32nm.

Chartered Semiconductor, membre de l'IBM Alliance for 32nm bulk CMOS process technology development a annoncé qu'il travaillerait également avec Big Blue sur le 22nm. Depuis 2002, les deux firmes ont déjà collaborés ou collaborent pour le développement de la gravure en 90nm, 65nm, 45nm et 32nm.

Les recherches en commun auront lieu dans les installations 300mm d'IBM à East Fishkill, dans l'état de New York. Reste à savoir ce que les deux firmes entendent exactement par joint development, puisqu'en pratique il s'agit parfois plus de la simple revente des technologies nécessaires par IBM. Le communiqué de presse précise d'ailleurs qu'il y a des contreparties financières mais les montants de celles-ci ne sont bien entendu pas dévoilés. Espérons que l'accord incite IBM à progresser rapidement sur le 22nm afin qu'AMD qui a plusieurs dizaines d'employés dans les locaux d'IBM à East Fishkill puisse proposer des circuits bénéficiant de cette taille de gravure à l'horizon 2012...

TSMC s'étend sur les 45, 40, 32 et 22nm

Taiwan Semiconductor Manufacturing Company, connu du grand public essentiellement grâce à certains de ses clients tels que Nvidia, ATI ou VIA semble avancer de façon satisfaisante sur le 32nm à en croire Jack Sun, vice-président de la société. Ce dernier indique qu'une équipe de plus de 200 ingénieurs travaille sur cette taille de gravure et que les premiers circuits en bénéficiant devraient voir le jour au quatrième trimestre de 2009.

Taiwan Semiconductor Manufacturing Company, connu du grand public essentiellement grâce à certains de ses clients tels que Nvidia, ATI ou VIA semble avancer de façon satisfaisante sur le 32nm à en croire Jack Sun, vice-président de la société. Ce dernier indique qu'une équipe de plus de 200 ingénieurs travaille sur cette taille de gravure et que les premiers circuits en bénéficiant devraient voir le jour au quatrième trimestre de 2009.

Dans un plus proche avenir, si l'on savait déjà que le process 45nm allait entrer en production en septembre, l'on apprend maintenant que la compagnie avance rapidement sur une version plus avancée de celui-ci. Ainsi, des tests pour l'employer avec des types de circuits aussi variés que possible et ce, avec une meilleure densité et des fréquences plus élevées tout en maintenant le courant de fuite au même niveau sont prévus pour mai 2008. Toujours à la même période, le 40nm devrait être lancé officiellement.

Enfin, Jack Sun déclare qu'une étude pilote sur le 22nm est en cours, ce qui est très prudent et pragmatique puisque dans l'état actuel il semble peu probable de voir TSMC franchir cette étape seul.