Les contenus liés aux tags APU et Carrizo

Les 2 contenus de cette page

+29% de transistors pour l'APU AMD Carrizo

Quelques détails sur l'APU AMD Carrizo

+29% de transistors pour l'APU AMD Carrizo

Publié le 19/11/2014 à 14:26 par Marc Prieur

A l'occasion de l'International Solid State Circuits Conference (ISSCC) en février prochain, AMD devrait dévoiler des informations sur futur APU Carrizo. EETimes a pu avoir un résumé des différentes présentations qui seront faites à cette occasion qui dévoile quelques informations sur la puce. Gravée en 28nm, elle devrait mesurer 244.62mm² et intégrer 3,1 milliards de transistors.

Les curs Excavator, a priori la dernière évolution de l'architecture CMT introduite avec Bulldozer, seraient 23% plus petits que ceux de Piledriver et consommeraient 40% en moins, un chiffre important qui mérite des précisions. Côté taille un Kaveri intègre 2,41 milliards de transistors, soit +28,6%, toujours dans 245mm². La densité augmente donc fortement alors qu'on reste en 28nm, le surplus de transistors étant dédié à l'intégration d'un FCH allégé (cf. cette actualité) et peut être un nombre plus important de Compute Units GCN ou plus de cache.

Pour rappel Carrizo est attendu pour 2015 et devrait utiliser l'actuel Socket FM2+.

Quelques détails sur l'APU AMD Carrizo

Publié le 21/07/2014 à 10:45 par Marc Prieur

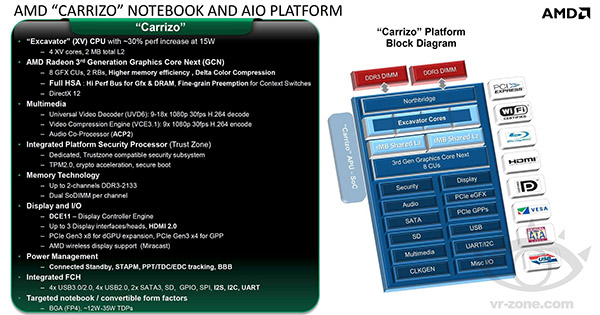

VR-Zone publie quelques informations qui proviendraient d'AMD concernant Carrizo, l'APU qui succédera aux actuels Kaveri.

En fait plutôt qu'un APU il faut parler de SoC puisque sur la version BGA pour portables ici présentée intègre directement le southbridge (appellé FCH chez AMD). Il gère ainsi 4 ports USB 3.0, 4 ports USB 2.0, 2 ports SATA 6 Gbps ainsi d'un lecteur de carte SD. Cette version de Carrizo BGA utilisera un nouvel emplacement de type FP4 et ne sera pas compatible pin à pin, intégration du FCH oblige, avec les actuels Kaveri en FP3. Sur plate-forme Desktop ce sera différent puisqu'a priori Carrizo sera compatible FM2+, le FCH intégré n'étant pas utilisé sur cette version.

On notera également l'intégration, comme sur Beema, d'un Platform Security Processor. Il s'agit en fait d'un core ARM Cortex-A5 ce qui permet à AMD de profiter de la plateforme de sécurisation TrustZone d'AMR et d'implémenter TPM 2.0.

Côté CPU, Carrizo intégrera 2 modules Excavator, qui devrait pour rappel être la dernière évolution de l'architecture CMT introduite avec Bulldozer. Les versions BGA auront des TDP allant de 12 à 35W, AMD parle d'un gain de performances très intéressant de 30% à 15W, probablement face à Steamroller tel qu'intégré dans Kaveri. Bien entendu lorsque le TDP sera moins restreint le gain de performance devrait être plus limité, probablement inférieur à 10%. On note au passage la baisse de la taille du cache puisqu'on passe à 1 Mo de L2 au mieux par module contre 2 Mo jusqu'alors.

Pour ce qui est du GPU il ne faut a priori pas s'attendre à des changements majeurs, ainsi la partie graphique sera composée de 8 Compute Units GCN et de 2 ROPs, comme c'est le cas sur Kaveri. Si la mémoire, qui est le principal goulet d'étranglement sur iGPU, restera de type DDR3 avec un mode DDR3-2133 au mieux en version mobile, son utilisation aurait été optimisée par AMD.

Les APU Carrizo devraient débarquer en 2015, ils seront a priori gravés en 28nm chez GlobalFoundries.

Les 2 contenus de cette page