Les contenus liés aux tags Micron et 3D NAND

Afficher sous forme de : Titre | FluxLa 3D NAND Intel fait son apparition

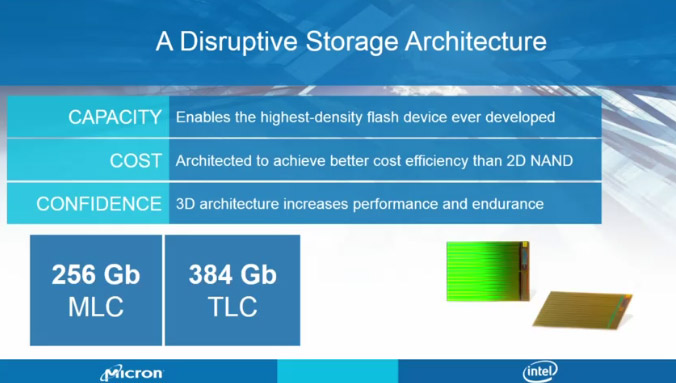

Alors que Samsung propose depuis quelques années maintenant de la 3D NAND, cette technologie se fait attendre chez les autres constructeurs. La puce de 256 Gbits MLC 32 couches développée par Intel et Micron et annoncée il y a un an vient enfin de faire son apparition sur une première gamme de SSD, les DC P3320.

Destinés aux serveurs et gérant le protocole NVMe, ils communiquent avec le système via un bus PCIe 3.0 x4 via un connecteur U.2 en version 2.5" (450 Go, 1.2 To et 2 To) mais sont également déclinés en carte fille pour les deux plus grosses capacités.

Côté performances ont a droit pour la version 2 To à 1600 Mo /s en lecture, 1400 Mo /s en écriture pour 365K IOPS en lecture mais "seulement" 22K IOPS en écriture, une valeur qui a toutefois le mérite d'être soutenue. Intel n'ayant rien communiqué sur l'endurance ou le positionnement tarifaire des SSD, il faudra attendre pour en savoir plus sur les apports concrets de cette 3D NAND.

IDF: Roadmap mémoire Micron

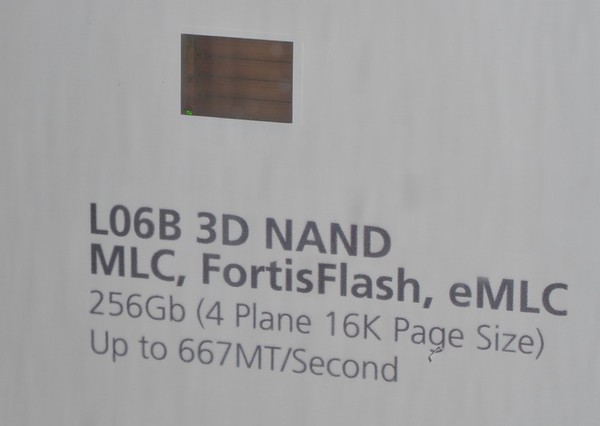

Le partenaire d'Intel sur la mémoire 3D XPoint était présent sur l'IDF avec un stand ou l'on pouvait apercevoir un wafer de NAND 16nm, ainsi qu'un module 3D NAND de 256 Gbits.

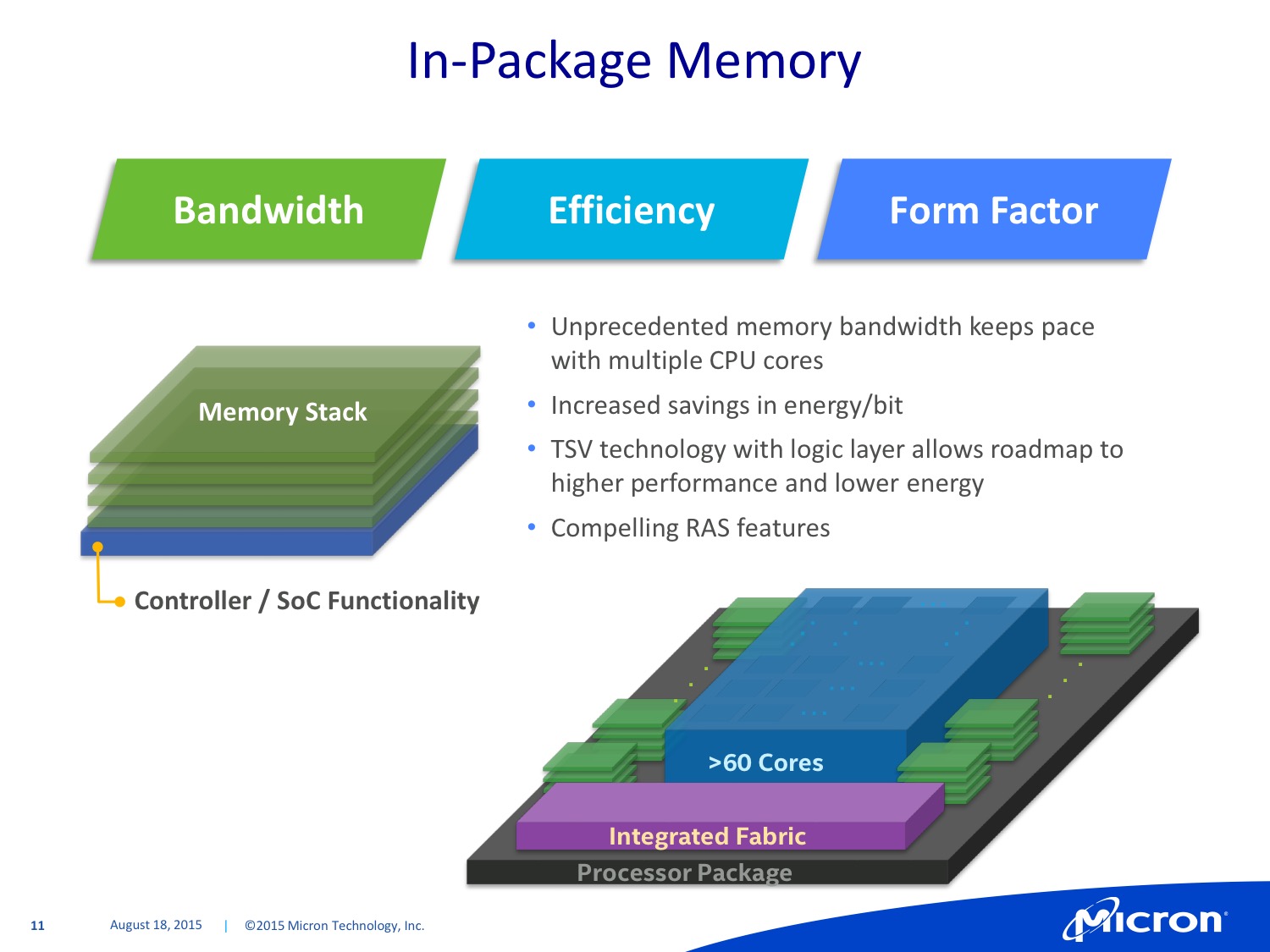

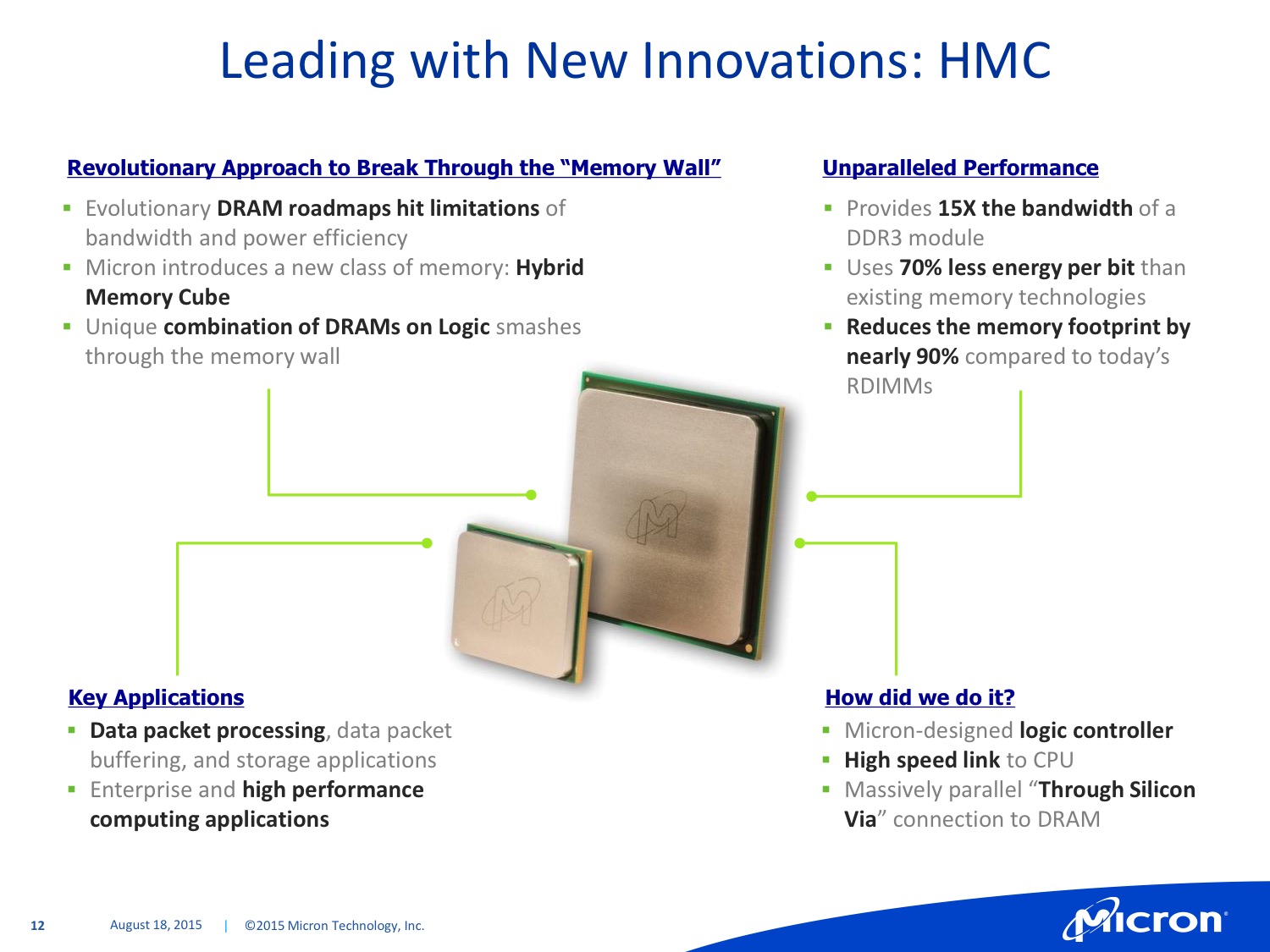

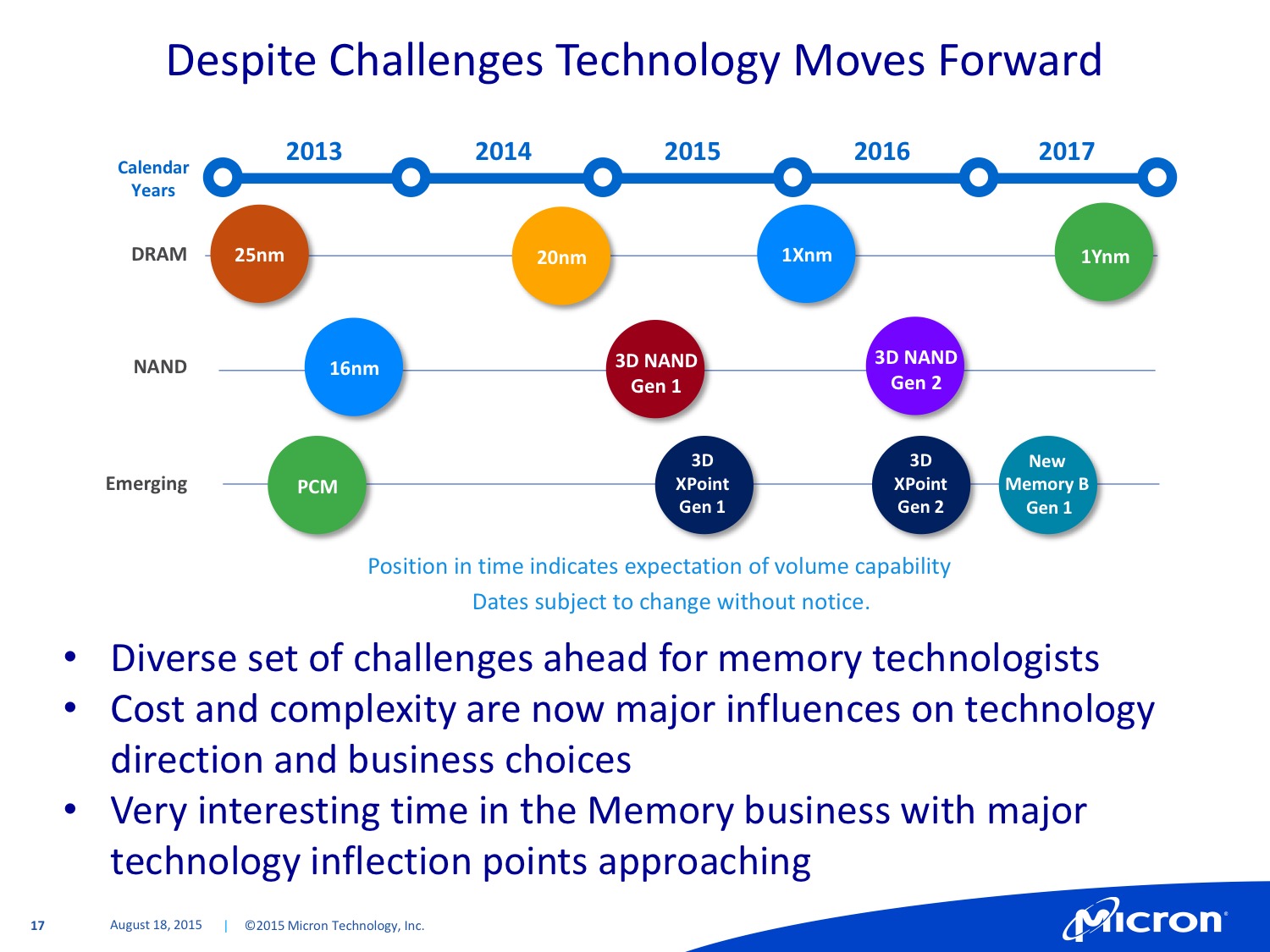

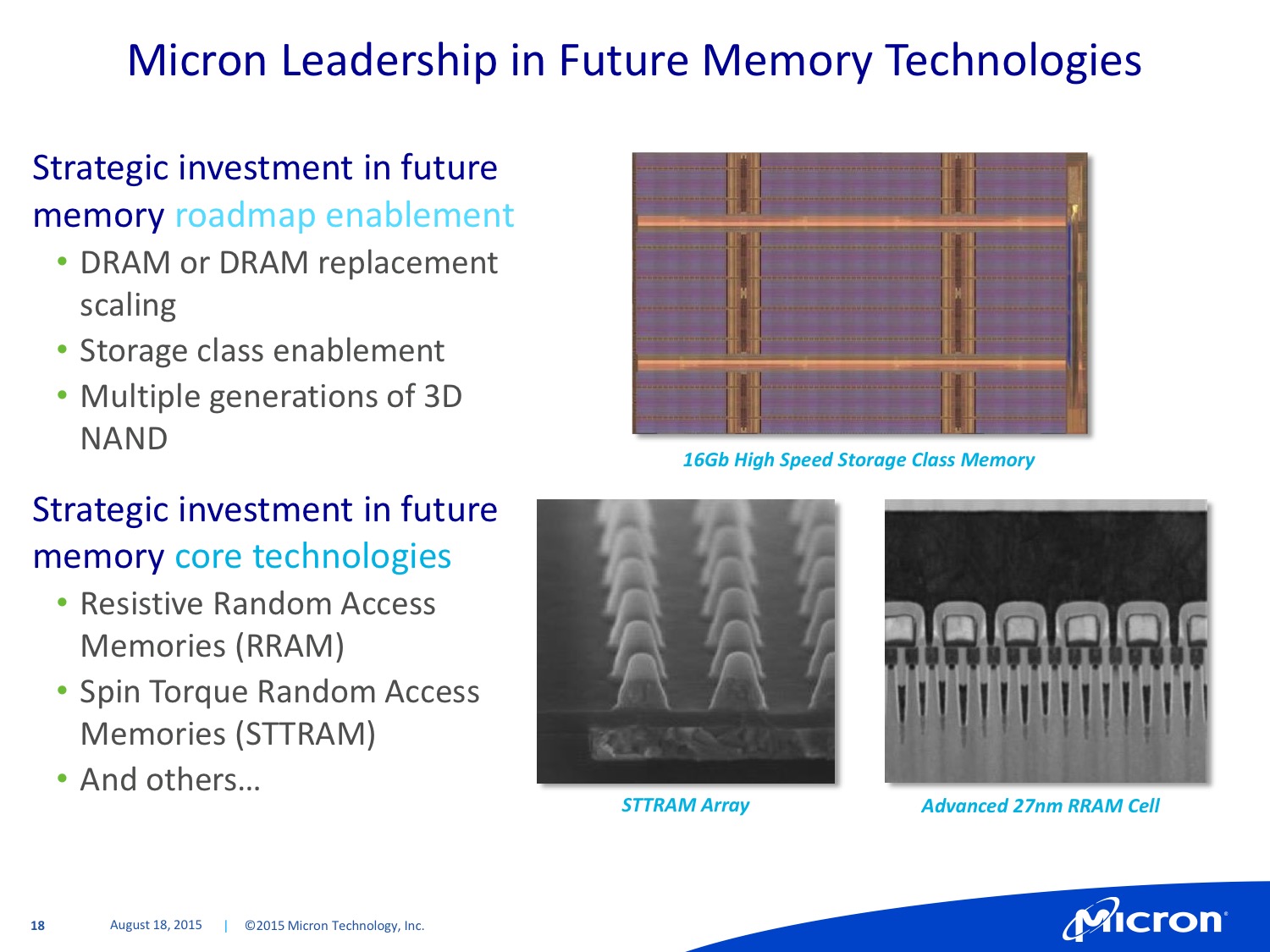

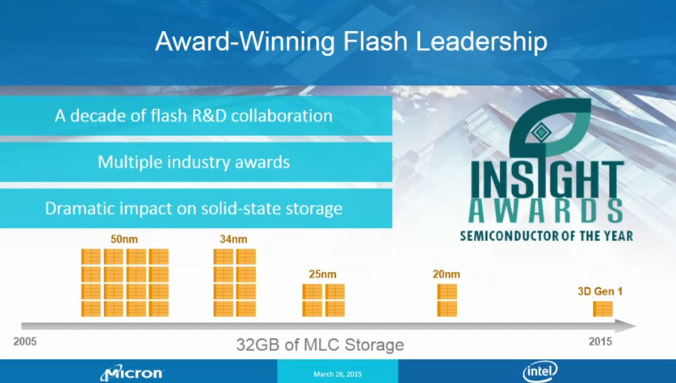

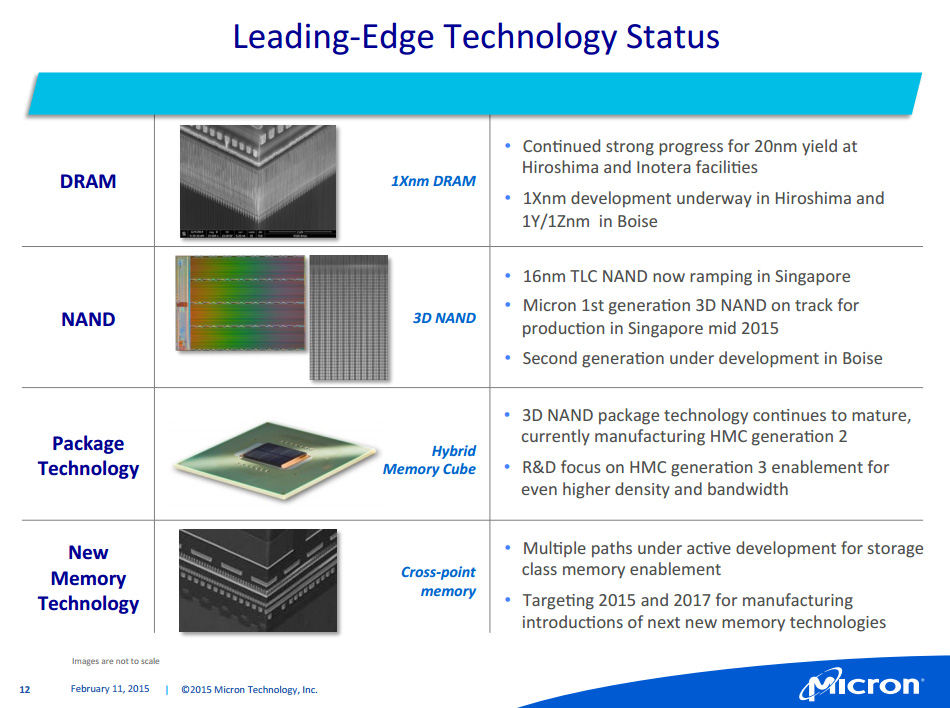

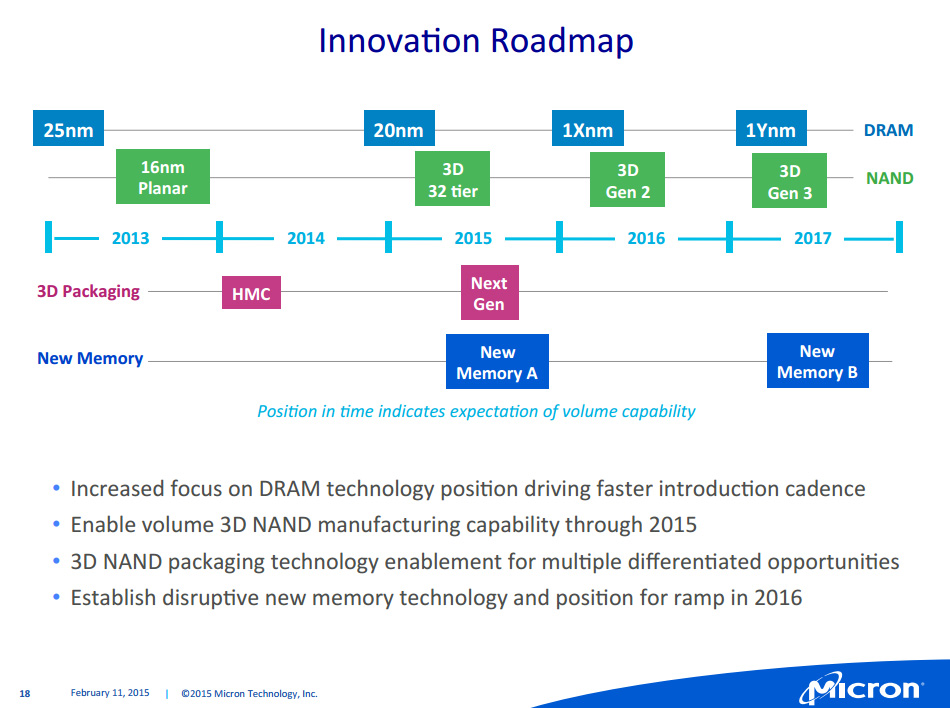

La société a également effectué une présentation ou elle a évoqué ses technologies mémoires. Le constructeur continue de travailler sur l'Hybrid Memory Cube (HMC), une technologie qui supperpose des dies de mémoires avec une couche de contrôleurs logiques. La troisième génération est en cours de développement même si l'on ne sait pas encore ce qu'elle apportera.

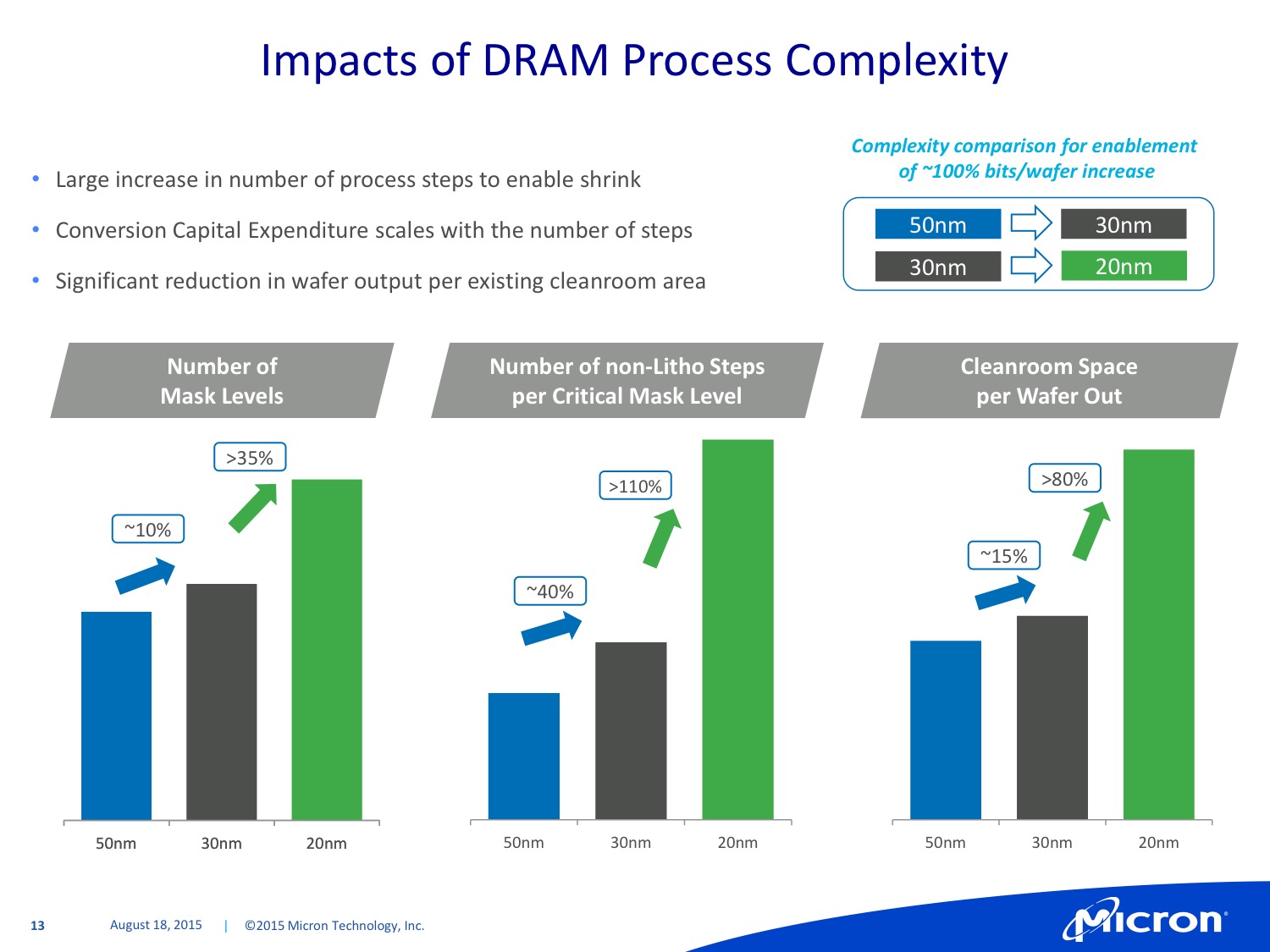

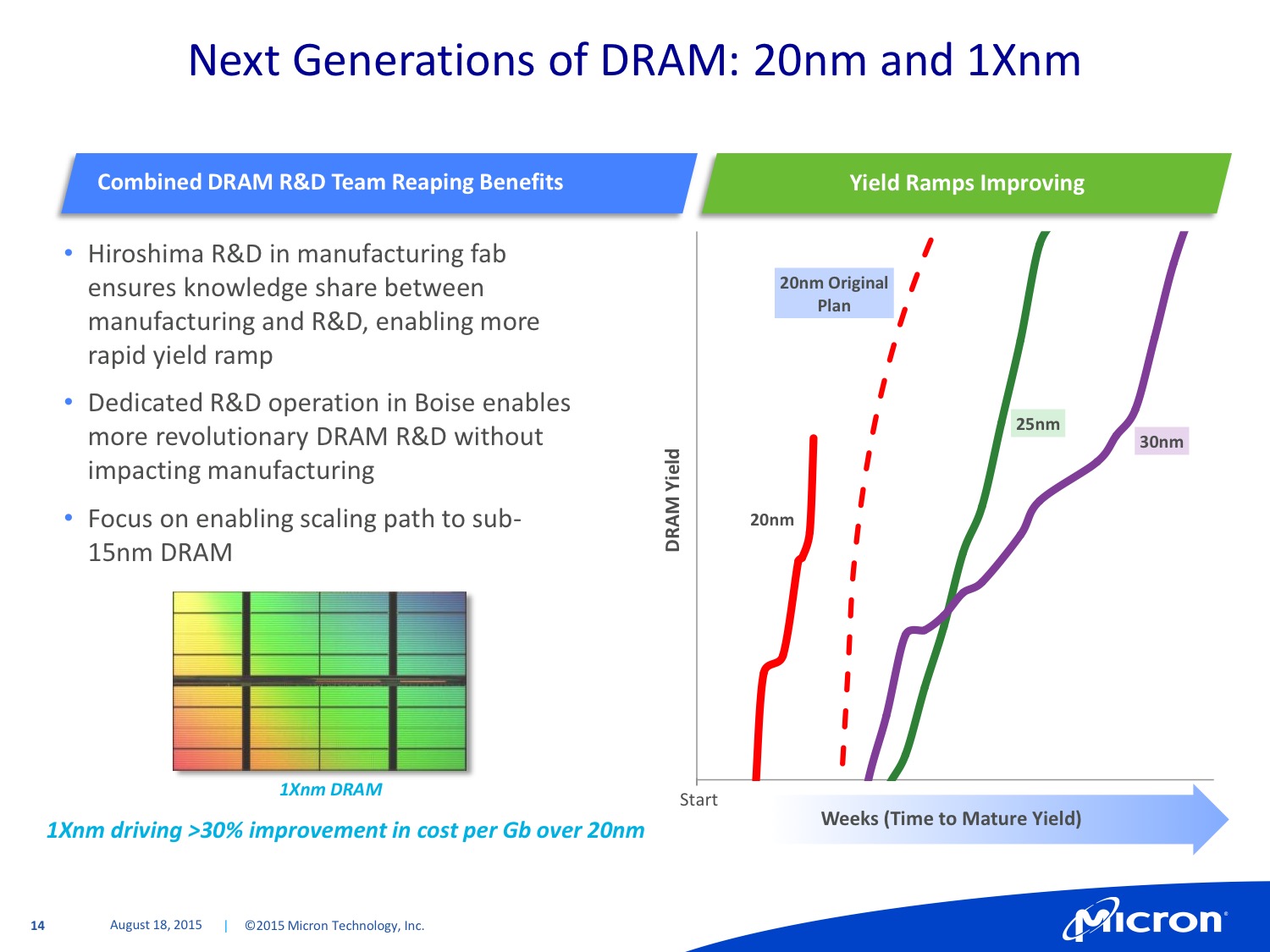

Micron est également revenu sur la complexité de la fabrication de la mémoire DRAM a 20nm et au dela. L'augmentation des coûts via les masques et les opérations rend de plus en plus difficile chaque passage à un nouveau node. Malgré tout le fabricant s'est felicité de ses yields atteint en 20nm et a indiqué travailler sur le 15nm et au delà.

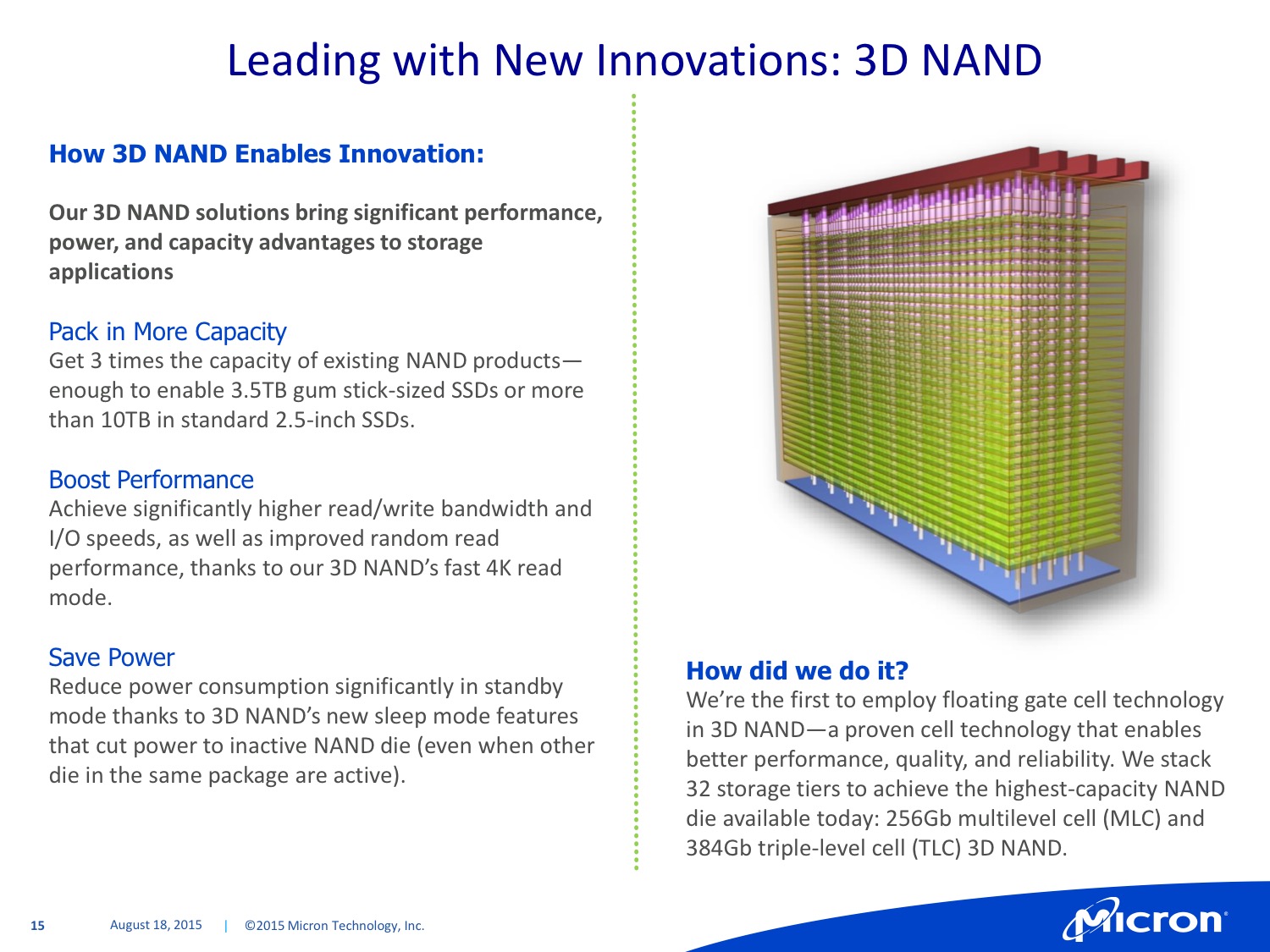

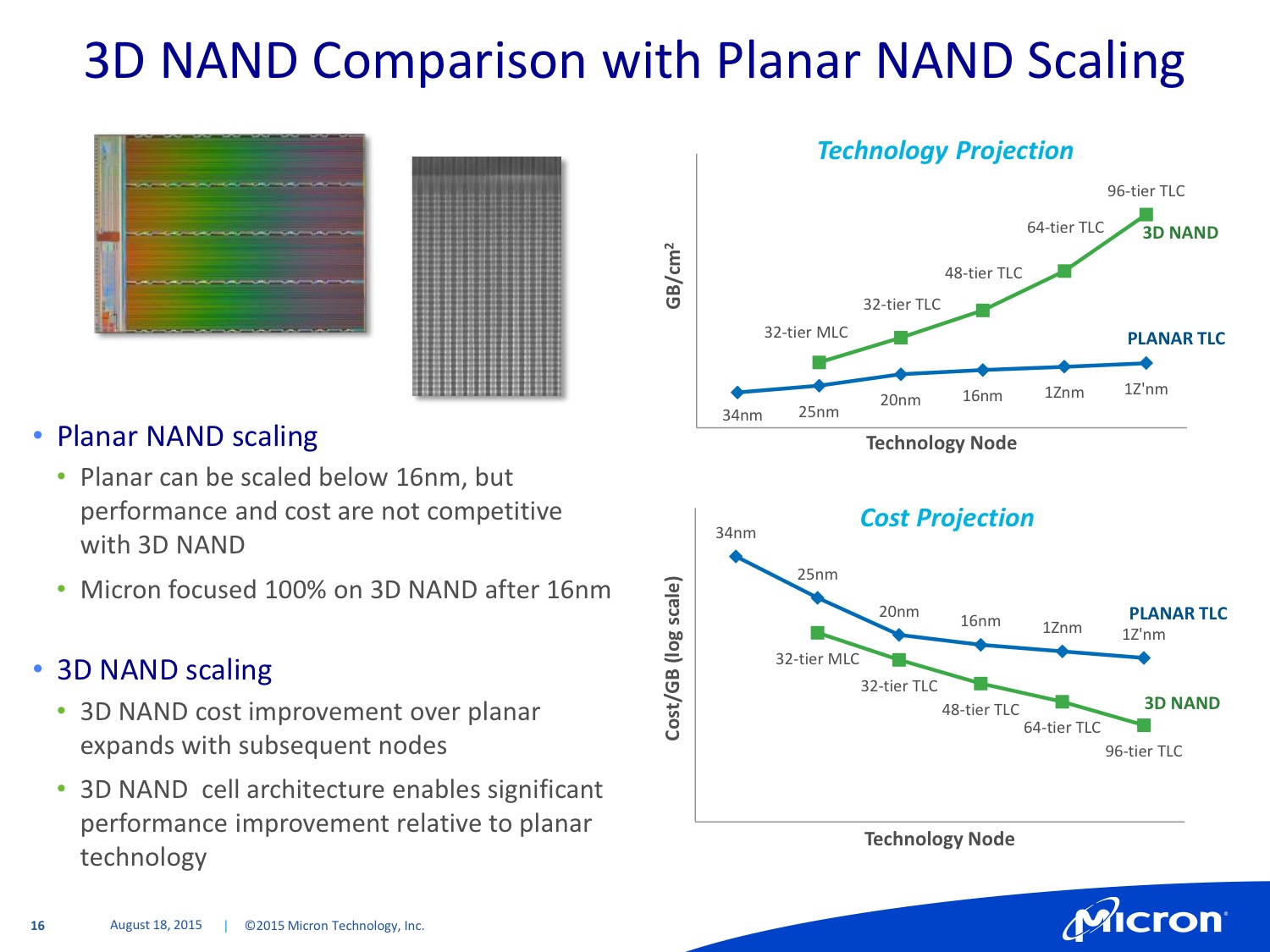

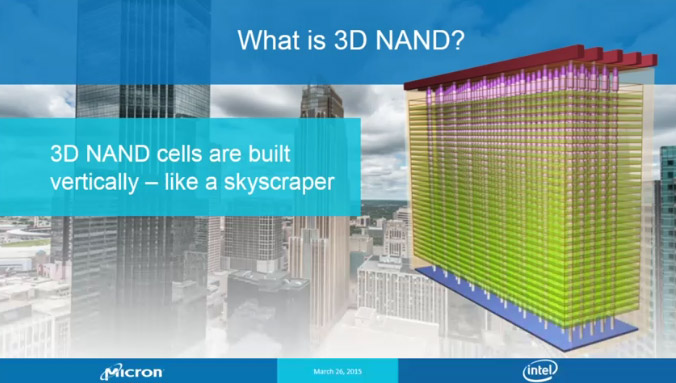

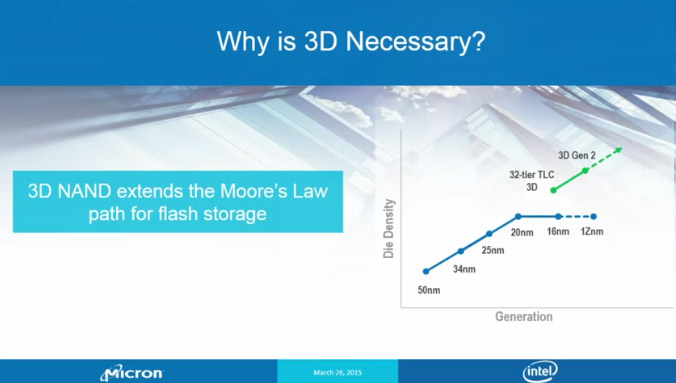

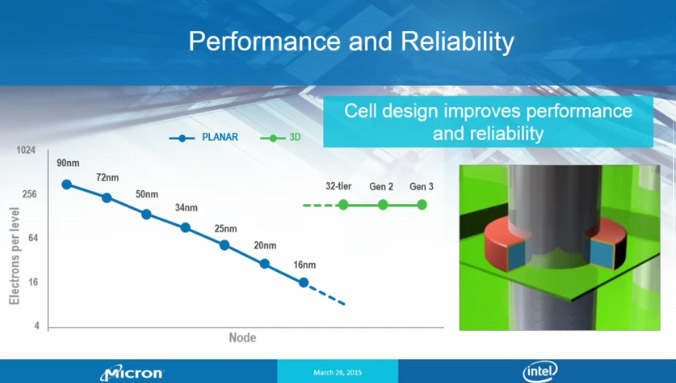

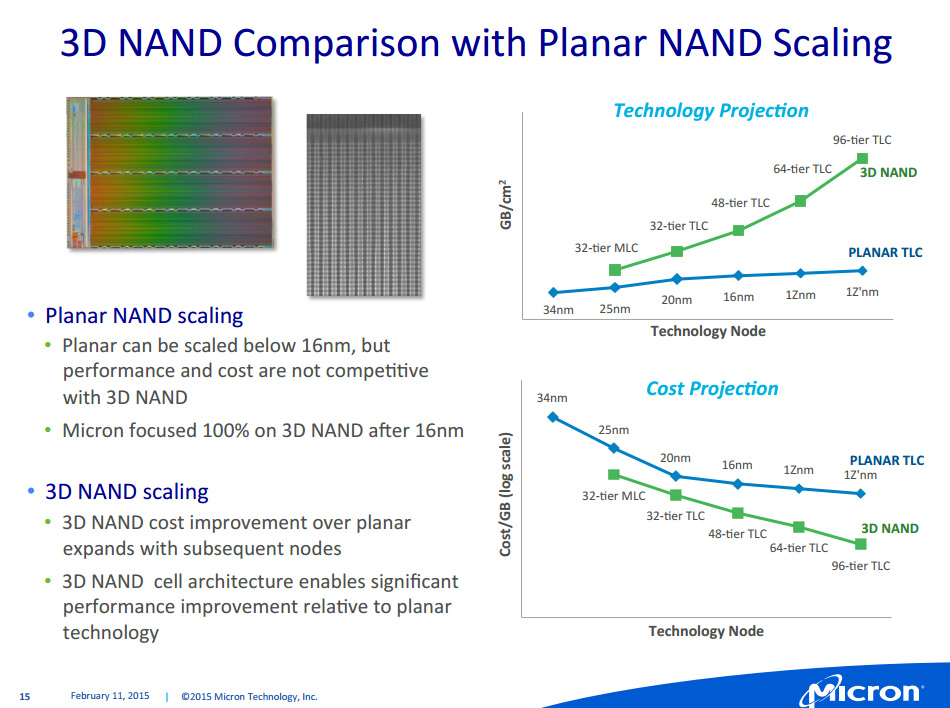

Côté NAND, Micron a confirmé que le 16nm serait son dernier node « traditionnel » et qu'il passait au delà à une gamme 100% 3D NAND. Cette variante de la NAND permet pour rappel de construire les cellules verticalement pour les empiler en augmentant la densité. Un avantage important qui permet d'utiliser des process plus anciens, et mieux maitrisés, autour de 50nm pour la première génération de Micron. La seconde génération de 3D NAND apparaitra en 2016.

3D XPoint a été peu évoqué, si ce n'est sur le fait qu'il y aura une seconde génération de cette mémoire en 2016. On notera que Micron parle toujours sur ses roadmaps d'une seconde nouvelle mémoire qui arriverait en 2017. Une variante de STTRAM (Spin Transfer Torque RAM) semble être l'une des possibilités, il faudra attendre un peu avant d'en savoir plus !

Intel et Micron annoncent aussi leur 3D NAND

Après l'annonce de Toshiba hier, Micron et Intel ont également annoncés leur version de mémoire NAND verticale, également appelée plus généralement 3D NAND.

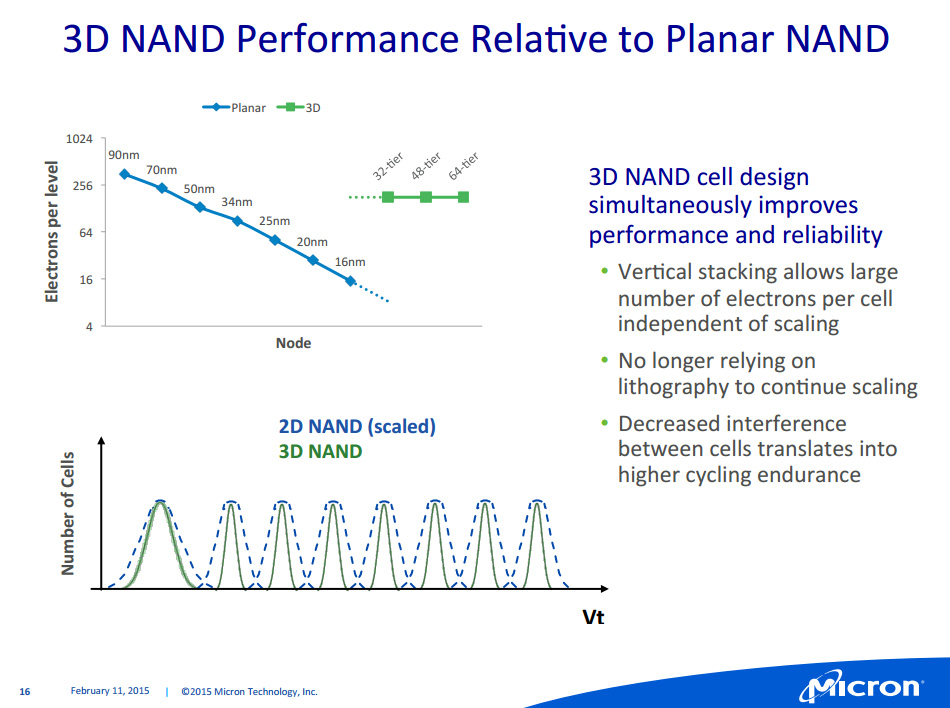

Le principe de base de la 3D NAND est de changer la structure des cellules mémoires en transformant la structure planaire classique en une structure verticale que l'on empiler pour augmenter massivement la densité (plus de détails ici. En contrepartie, les fabricants utilisent des processus de fabrications plus anciens (40 nm par exemple pour la V-NAND de Samsung), mieux maitrisés ce qui permet d'envisager des perspectives d'évolution pour les années à venir.

Des premiers échantillons ont été produits et les deux sociétés devraient lancer la production en volume au quatrième trimestre, indiquant que les SSD 3D NAND dans les deux sociétés arriveront plutôt en 2016. En pratique, Intel et Micron annoncent pouvoir atteindre avec ces puces 3.5 To dans un format M.2, et 10 To dans un format 2.5 pouces. Pour atteindre cette densité, les sociétés empilent 16 dies dans un même package.

3D NAND 48 couches chez Toshiba

Toshiba vient d'annoncer avoir produit des puces mémoires flash (NAND) à construction verticale (souvent appelée 3D NAND) à 48 couches. Pour rappel, en 2007 Toshiba avait été le premier à produire une technologie de mémoire ou l'organisation des cellules se fait non plus de manière horizontale comme traditionnellement, mais cette fois ci de manière verticale.

La mémoire NAND traditionnelle au milieu en haut peut être empilée (Stack), la stratégie classique que l'on voit à droite, ou bien transposée verticalement (le chemin de gauche) pour réaliser une structure appelée BiCS par Toshiba qui peut être vue comme le pendant du FinFET pour la NAND

En 2007, Toshiba ne précisait pas le nombre de couches qu'il avait réussi à superposer dans sa structure mais évoquait dans son communiqué de presse le nombre de 32 pour expliquer les difficultés de l'empilement. Presque huit années après, le constructeur indique aujourd'hui avoir produit des puces 48 couches de 128 Gbits (16 Go) qui sont disponibles dès aujourd'hui sous la forme d'échantillons.

Toshiba indique également qu'il commercialisera cette mémoire à partir de 2016, elle sera fabriquée en volume dans la nouvelle Fab2 située à Yokkaichi au Japon. En 2014, Toshiba avait annoncé remplacer cette ancienne usine par une nouvelle qui serait capable de produire de la mémoire NAND classique et « 3D » à compter de 2016. Le communiqué de la marque indique que la Fab2 devrait être opérationnelle durant la première moitié de 2016.

Cette structure de mémoire permet théoriquement d'augmenter fortement la densité même si pour l'instant, il faut se contenter de puces 128 Gbits pour ce premier échantillon. On rappellera que si Toshiba a été pionnier de cette technologie, Samsung avait été le premier à lancer la production de sa propre version de mémoire NAND verticale, baptisée V-NAND en 2013. Si l'agencement technique semblait légèrement différent du BiCS de Toshiba (voir notre article), le principe de base reste le même.

Cette V-NAND s'est ainsi retrouvée dans les SSD 850 Pro du constructeur sous la forme de puces empilant 32 couches. De son côté, si Toshiba met en avant l'empilement de 48 couches, on ne connait pas encore la finesse de gravure qui sera utilisée. Plus de détails seront probablement dévoilés d'ici à l'année prochaine. Pour le reste de la concurrence, Intel et Micron devraient proposer leur version 3D NAND 32 couches au second semestre 2015, tandis qu'il faudra attendre 2016 pour Hynix.

Micron affûte ses armes pour la NAND 3D

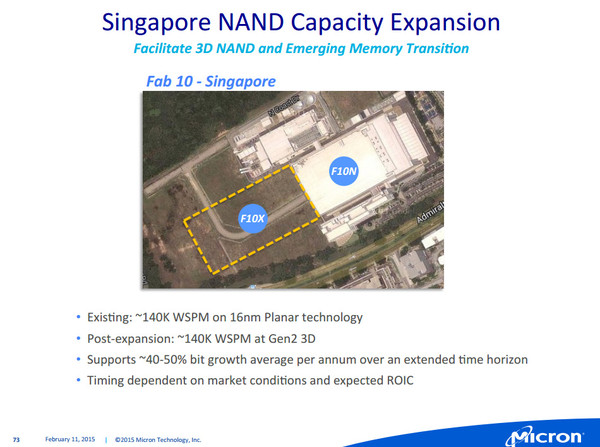

Micron vient d'annoncer que les travaux visant à doubler la capacité de production de sa Fab10 de Singapour avaient débutés. Avec 23 700m² supplémentaires, cette extension nommée F10X permettra à elle-seule de graver de la NAND 3D Micron de 2nde génération sur 140 000 wafers par mois, soit le niveau actuel de production de la Fab 10 qui produit pour l'instant de la NAND 16nm.

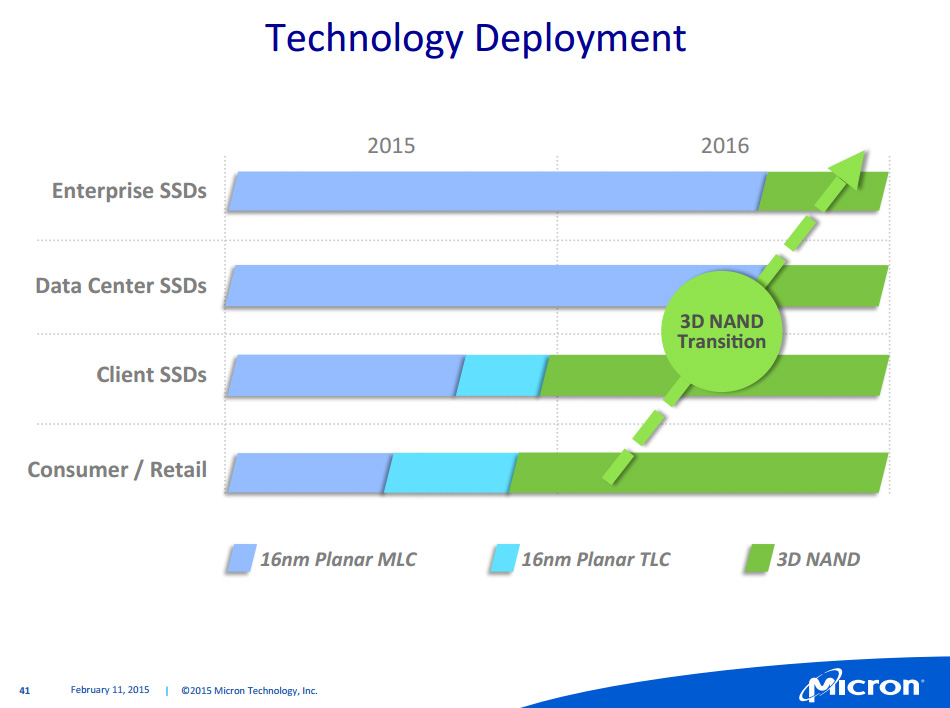

Micron a également donné quelques détails supplémentaires sur ses avancées côté NAND lors d'une conférence destinée aux analystes en février . On a notamment appris à cette occasion de la 16nm TLC était actuellement produite à Singapour et que le fabricant avait pour intention de lancer des SSD l'utilisant au second semestre. Pour la suite Micron mise à 100% sur la NAND 3D et la première génération devrait pour sa part être produite à compter de la mi-2015, pour une introduction sur des SSD en toute fin d'année.

Micron travaille pour rappel conjointement avec Intel sur cette NAND 3D, un domaine dans lequel ils accusent du retard sur Samsung. Ils ont toutefois l'intention de le rattraper ce retard avec une puce 256 Gb 32 couches qui offrira une meilleure densité par mm² que Samsung et un coût inférieur. On notera que si les projections de coût font état de versions MLC et TLC pour la NAND 3D 32 couches, pour les futures versions générations 48, 64 et 96 couches seule la TLC est mentionnée. Actuellement en développement, la NAND 3D de 2nde génération qui sera produite dans l'extension de F10X débarquera un an après la 1ère, suivie un an plus tard de la 3è génération.