Les derniers contenus liés aux tags SK Hynix et JEDEC

Samsung évoque la GDDR6

SK Hynix et Samsung parlent de HBM

CES: La GDDR5M victime des déboires d'Elpida

Samsung évoque la GDDR6

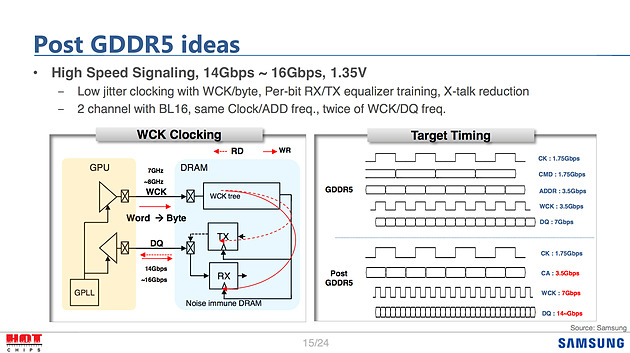

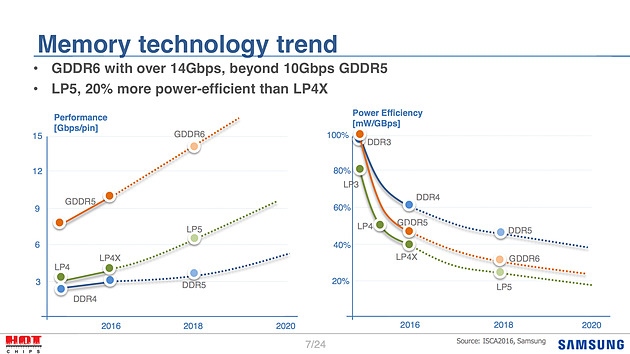

En parallèle à la mémoire HBM, Samsung à évoqué le futur de la GDDR5, ignorant quelque peu l'existence de la GDDR5X de Micron qui, bien que standardisée par le JEDEC, n'a pas été adoptée par ses concurrents.

Pour la GDDR6, Samsung évoque certaines des pistes de travail envisagées. Côté objectifs la mémoire visera dans un premier temps 14 à 16 Gbps, ce qui était la cible haute pour rappel de la GDDR5X lors de sa présentation par Micron. Lors de la certification de la GDDR5X par le JEDEC, 14 Gbps est devenu le maximum visé. On notera que la GTX 1080 utilise pour rappel de la GDDR5X 10 Gbps. Techniquement, la GDDR5X abaissait la tension de la GDDR5 à 1.35V et doublait la bande passante en doublant le prefetch.

Samsung donne ici quelques idées sur la GDDR6, reprenant par exemple l'idée de la tension à 1.35V. L'élaboration de la spécification finale se fera au sein du consortium JEDEC dans les mois à venir.

Côté timing, Samsung évoque 2018, aligné avec la DDR5 et la LPDDR5, et un gain d'efficacité énergétique autour des 30%. On notera au passage que Samsung continue lui aussi de pousser son propre standard "X" avec la LPDDR4X, une variante de la mémoire mobile LPDDR4 qui fait "seulement" baisser la tension VDDQ à 0.6V pour obtenir un gain d'efficacité de 20%. Si le JEDEC n'a pas encore ratifié la LPDDR4X, on notera que SK Hynix avait annoncé en juin qu'il produirait lui aussi ce type de mémoire.

SK Hynix et Samsung parlent de HBM

Comme tous les ans, c'est à la fin de l'été que se tient la conférence Hot Chips (28ème édition) ou les divers acteurs du milieu présentent leurs nouveautés. Parmi les attractions de cette année, on attendra, dans la nuit de mardi à mercredi, "A New, High Performance x86 Core Design from AMD" qui devrait probablement nous en dire un peu plus sur Zen.

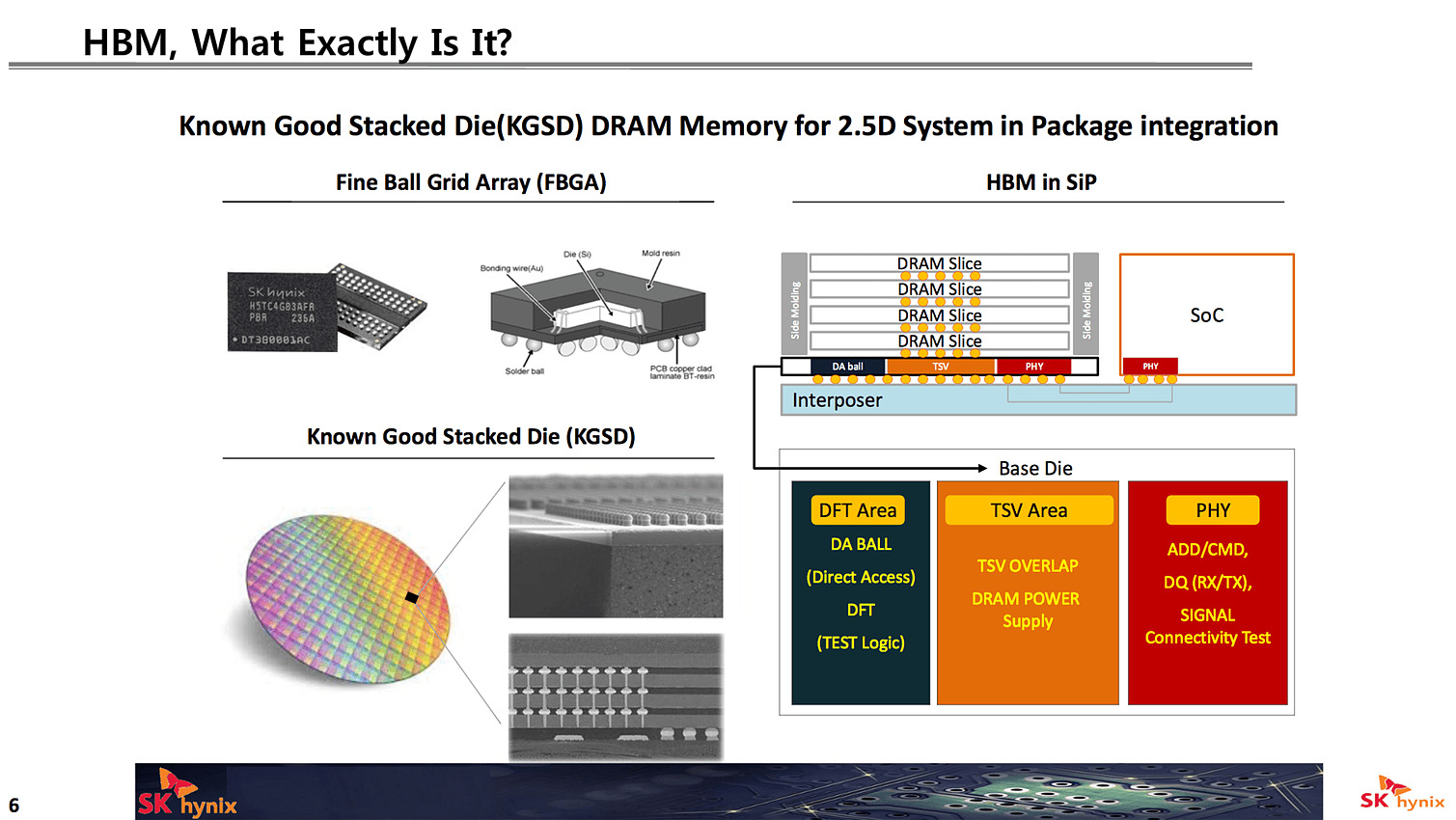

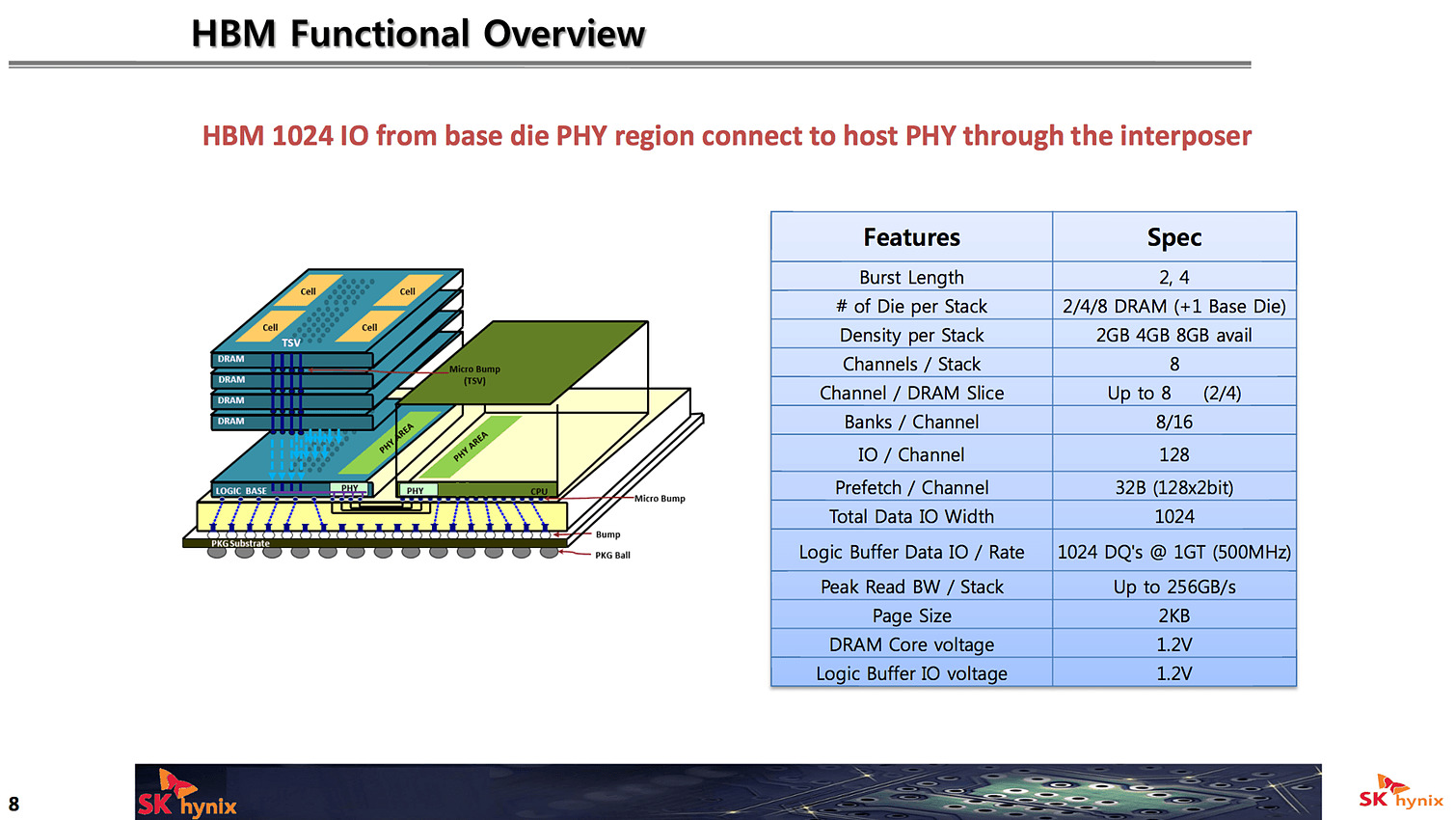

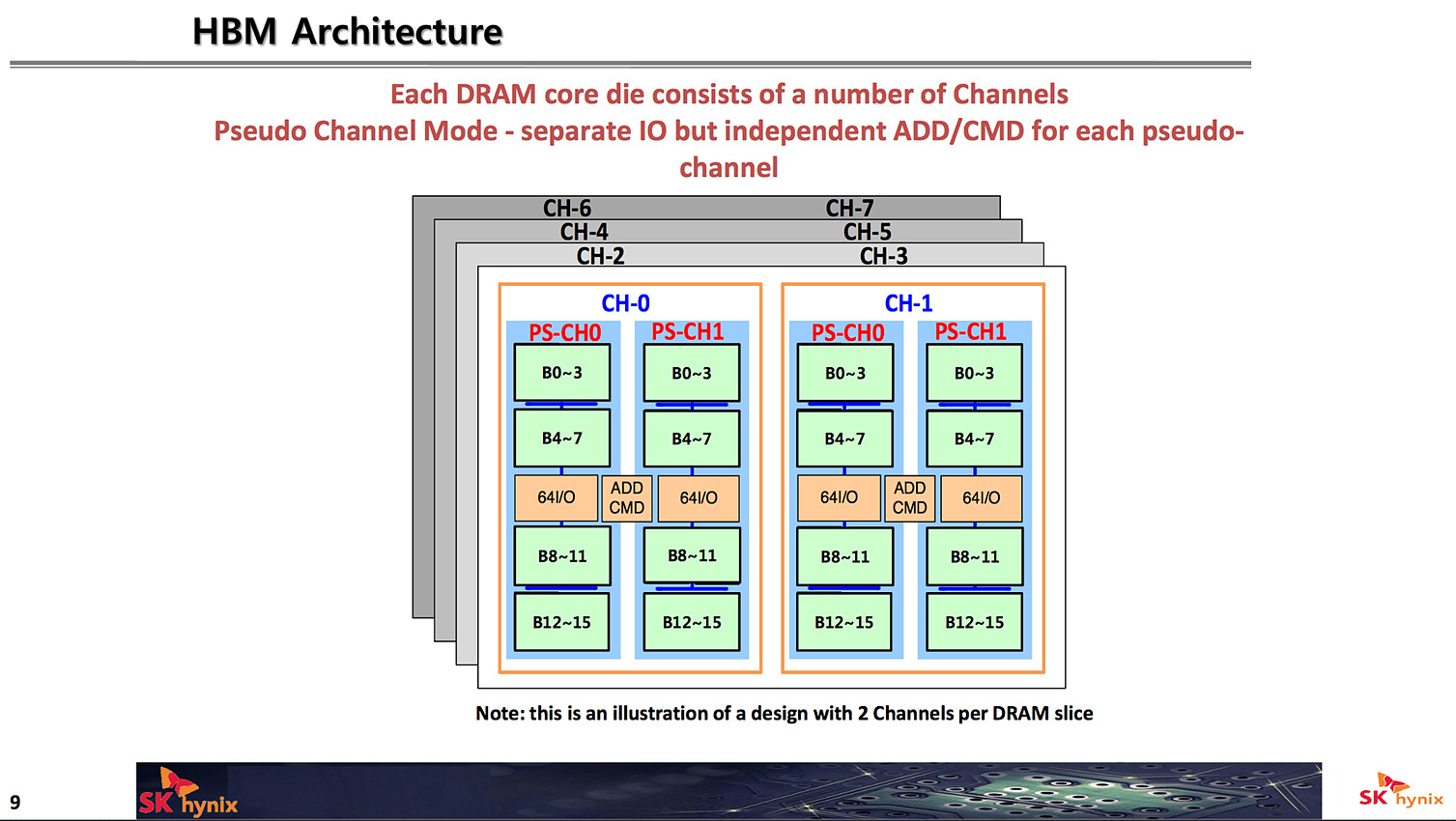

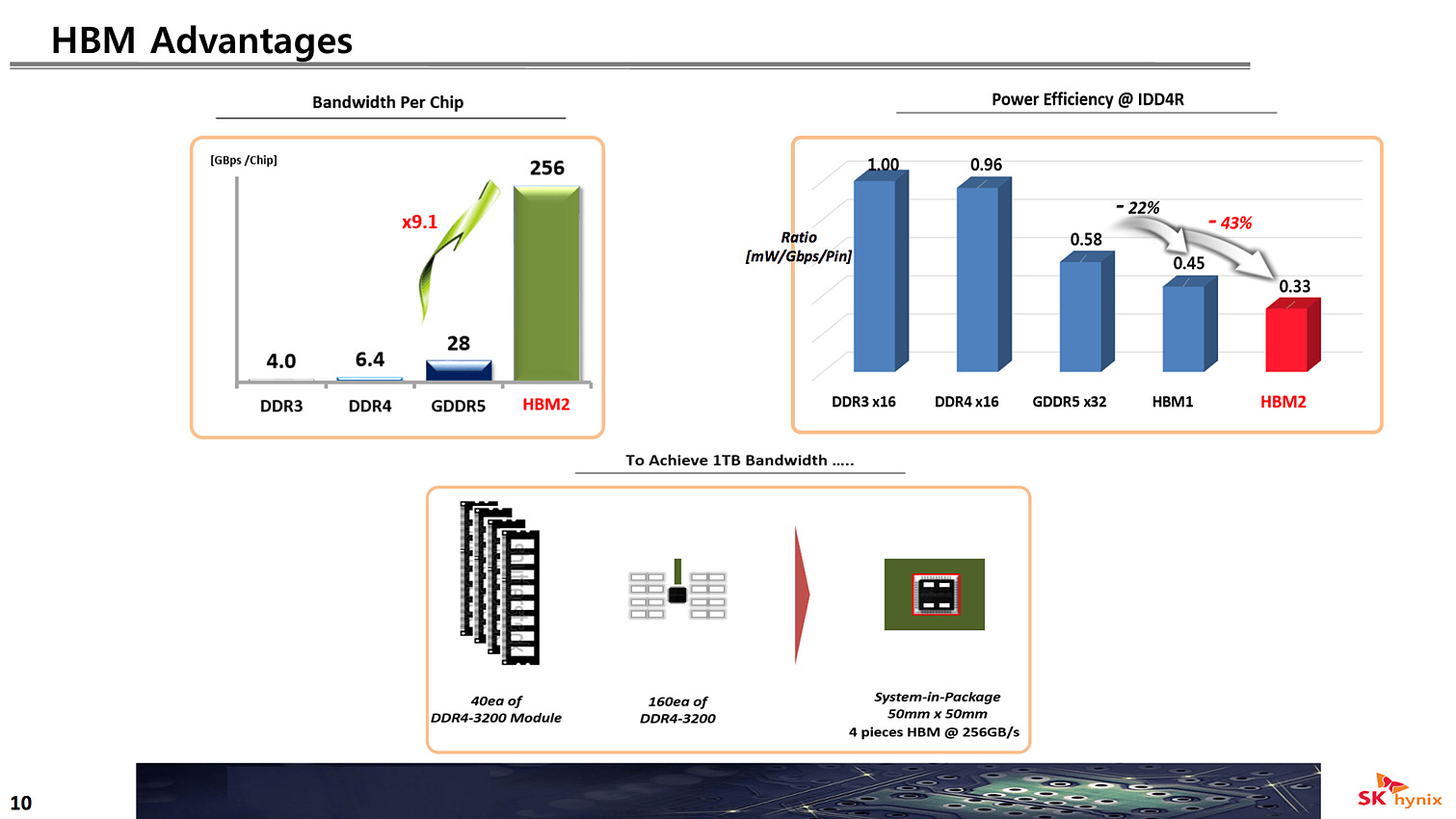

La première matinée de conférence avait lieu hier, dédiée à l'utilisation des nouvelles technologies mémoires. Chez SK Hynix et Samsung, la HBM était au programme. Pour rappel, la mémoire HBM est l'assemblage sur une même puce d'un die, en dessous, contenant les contrôleurs mémoires, et sur lequel on empile plusieurs dies de mémoire DRAM traditionnelle.

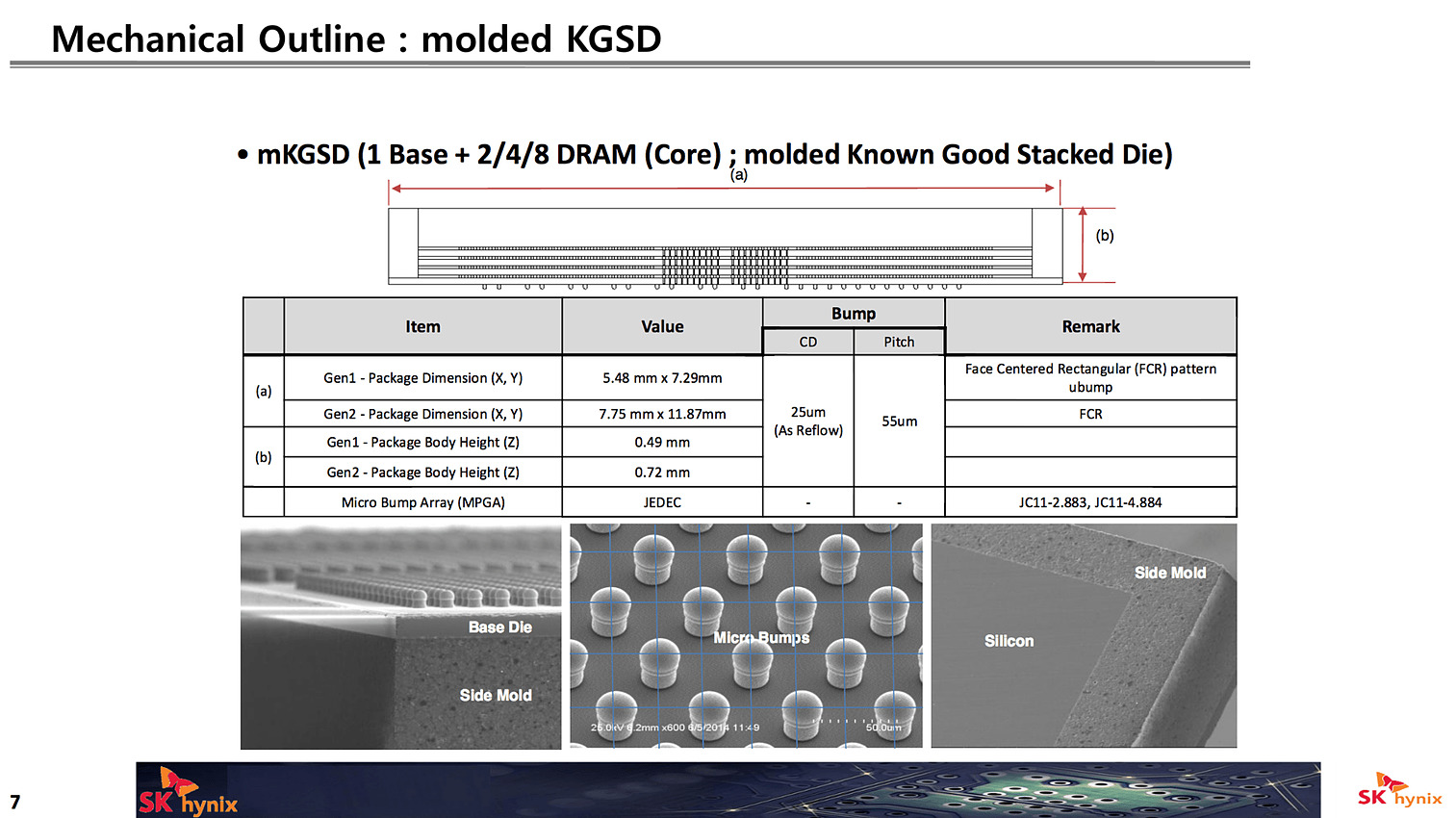

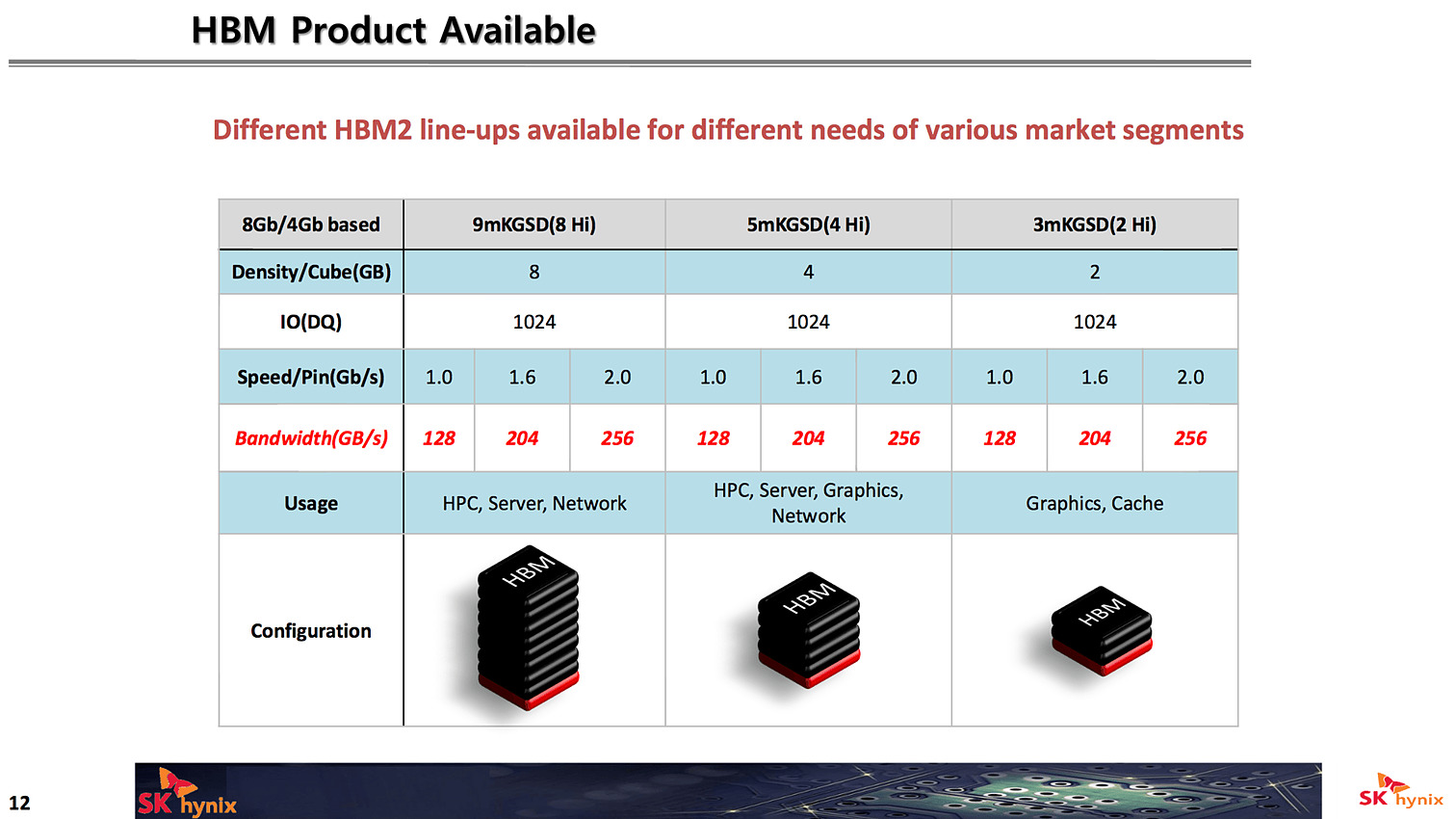

SK Hynix a confirmé ses ambitions sur la HBM2, qui pour rappel est standardisée par le JEDEC. Contrairement à la première version utilisée nottament par AMD sur les Fiji, la HBM2 utilise pour rappel des dies mémoire de 1 Go, empilés par deux, quatre ou huit. SK Hynix devrait lancer les premières puces, en version 4hi (quatre dies mémoire pour 4 Go au total) durant ce troisième trimestre.

Les versions 2Hi et 8Hi devraient suivre (soit 2 Go et 8 Go), et l'on notera qu'en plus des versions proposant 256 Go/s et 204 Go/s de bande passante, une version 128 Go/s sera également disponible au catalogue dans les différentes capacités.

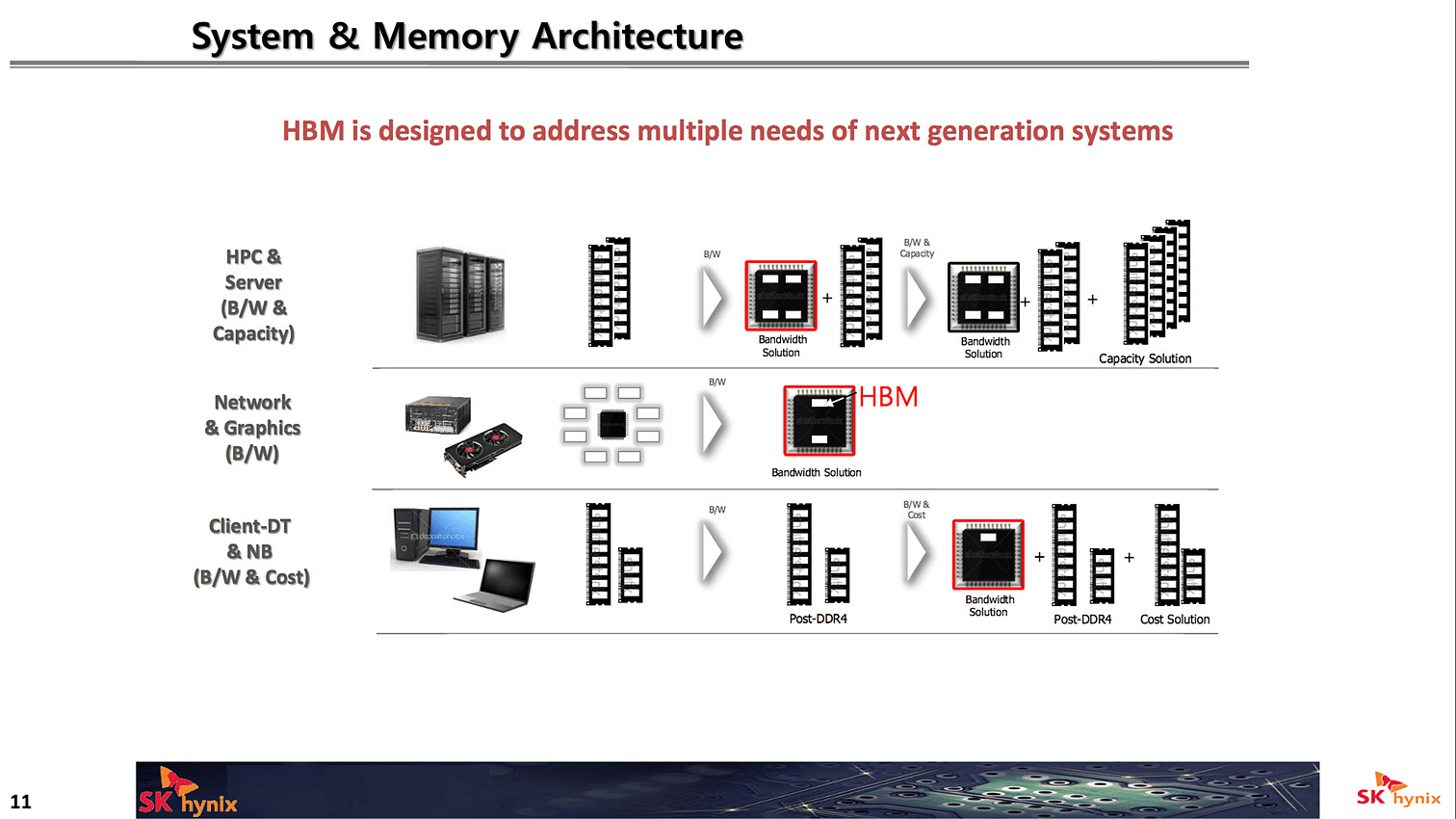

Côté utilisations, si les cartes graphiques ont été les premières à utiliser la HBM, SK Hynix envisage des utilisations dans le monde du HPC et des serveurs ou la HBM servirait de cache intermédiaire. Certaines déclinaisons de Zen pour serveurs devraient utiliser de la HBM, par exemple. SK Hynix voit également la HBM arriver en volume plus large dans les PC portables et desktop.

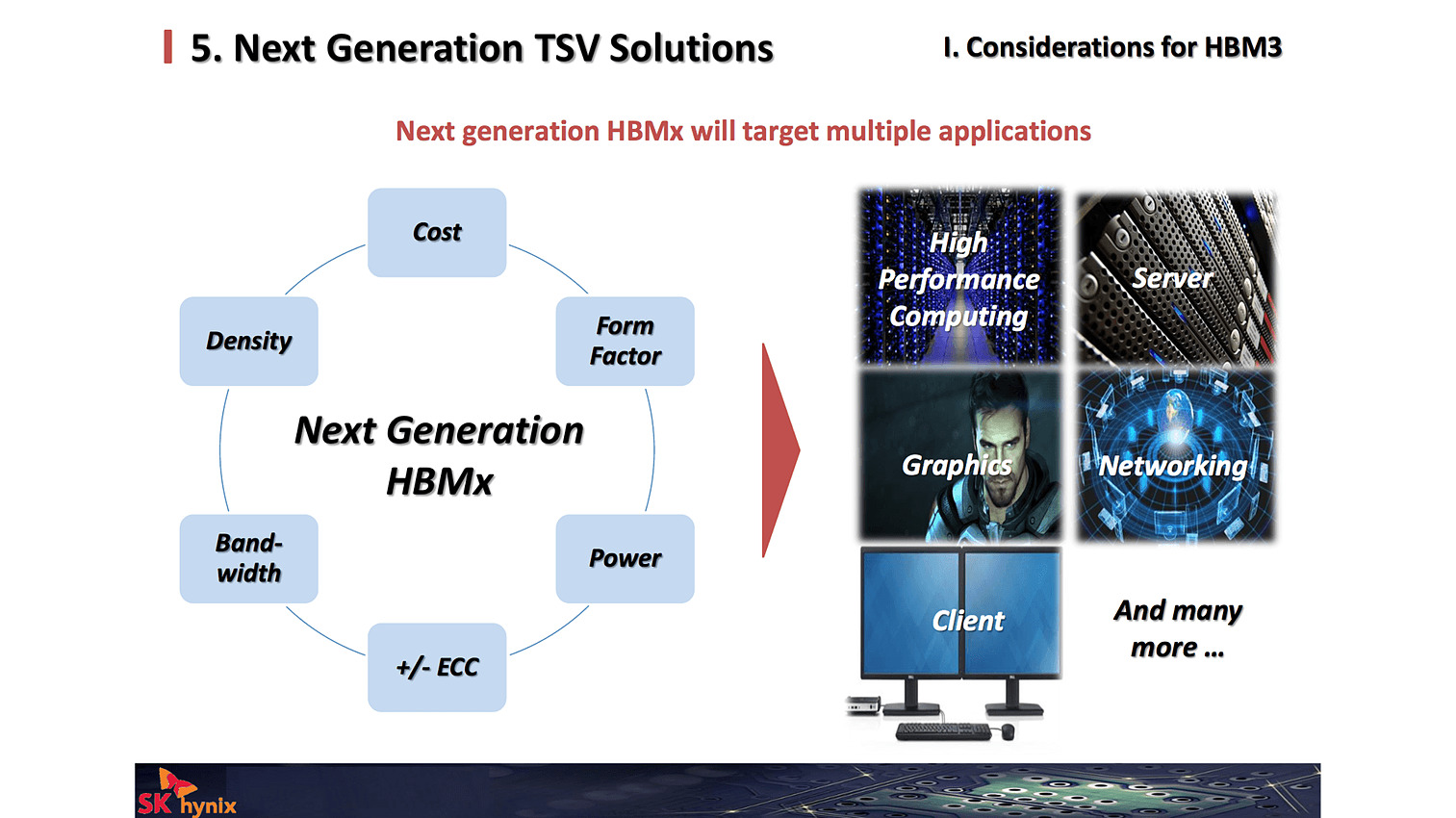

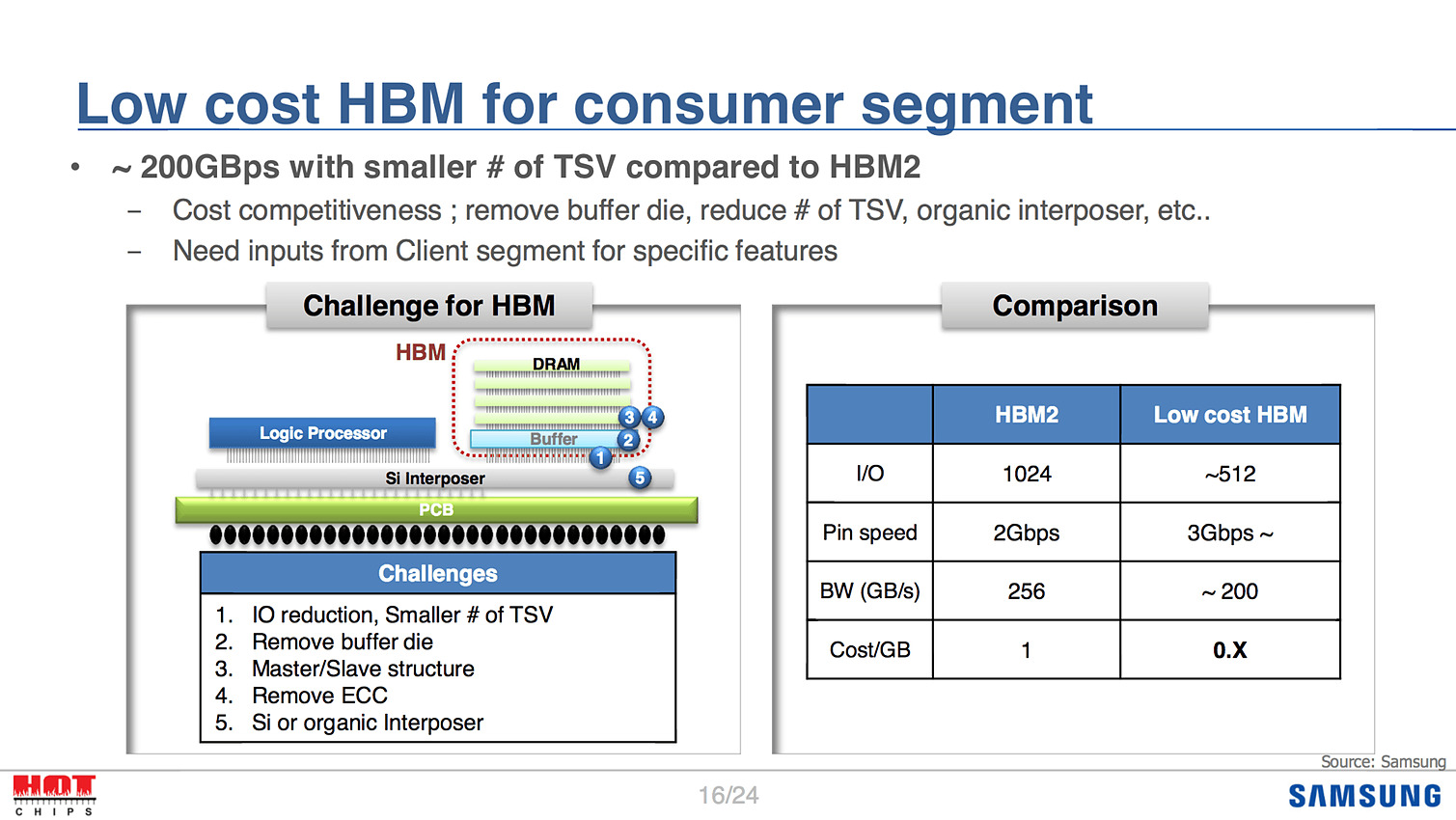

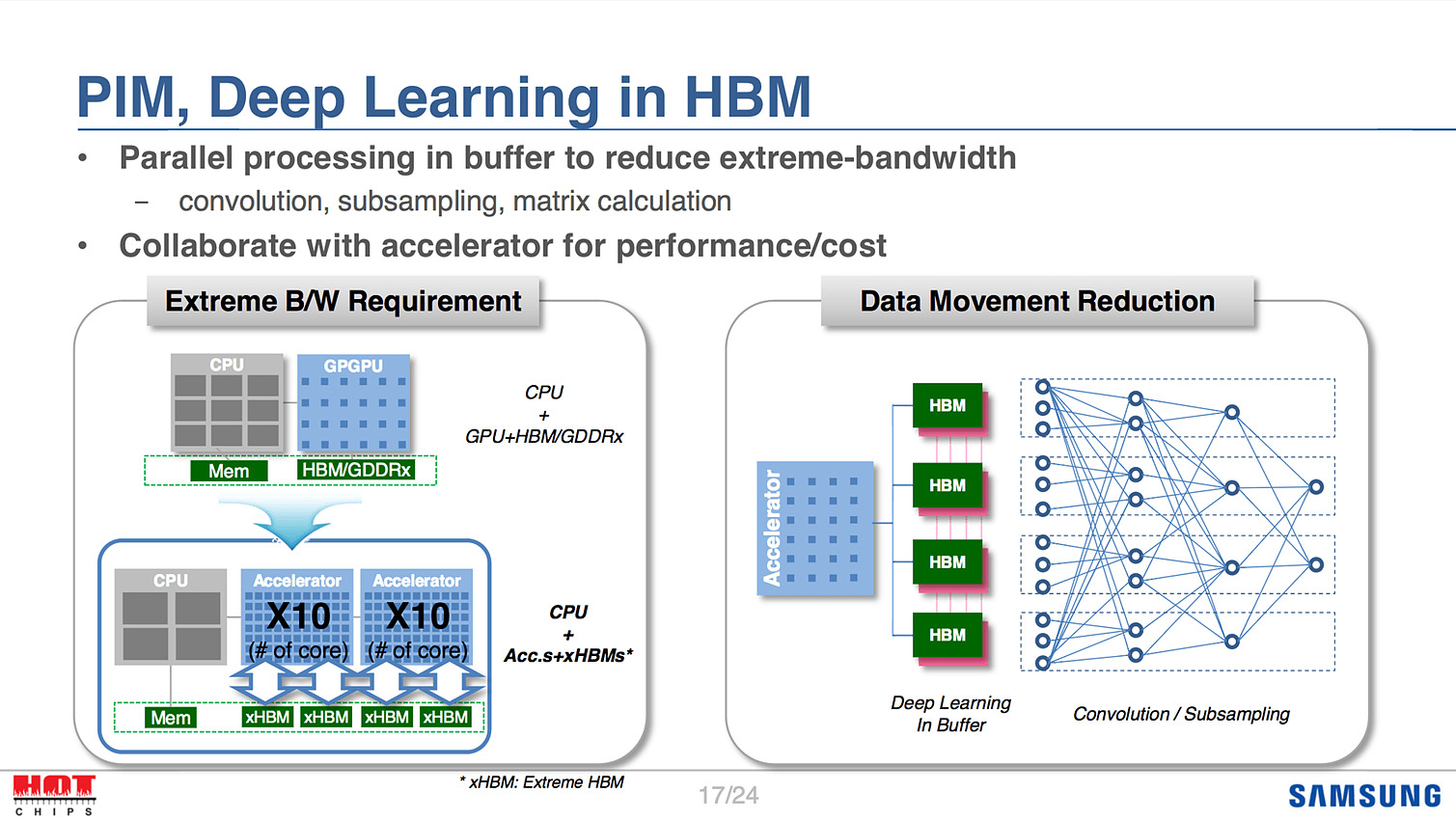

Côté Samsung, qui doit lancer aussi la HBM2 cette année, on parle surtout d'une version low cost de la HBM, qui ne serait pas de la HBM2 mais une variante plus abordable, en 512 bits (au lieu de 1024) et qui réduirait le nombre de TSV (Through Silicon Vias, les fils qui traversent les dies pour les relier les uns les autres). Le tout offrant tout de même 200 Go/s de bande passante. Un développement qui devrait s'effectuer en parallèle de celui de la HBM3 qui a pour objectif de doubler, sur le haut de gamme, la bande passante par rapport à la HBM2.

CES: La GDDR5M victime des déboires d'Elpida

Cet été, nous vous parlions de l'existence d'un type de mémoire qui était resté plus que discret et qui se présentait comme particulièrement bien adapté pour alimenter les APU : la GDDR5M. Il ne devrait finalement jamais voir le jour.

Pour rappel, la GDDR5M est un dérivé de la mémoire GDDR5, cette dernière étant avant tout destinée aux GPU (mais également exploitée sur la PS4). Si la base de la technologie est identique, la GDDR5M est optimisée pour autoriser un format "barrette mémoire" sans trop faire exploser les coûts, notamment à travers des puces de 4 Gbits interfacées en 16-bit, contre 32-bit pour la GDDR5 classique. De quoi permettre la mise en place de modules mémoire SO-DIMM de 2 Go et de 4 Go.

Durant la CES, nous avons eu l'opportunité de nous entretenir avec Joe Macri qui porte la double casquette de président du comité JEDEC en charge des mémoires DRAM et de Chief Technology Officer en charge des plateformes grand public chez AMD. Nous avons bien entendu voulu en profiter pour savoir ce qu'il était advenu de cette GDDR5M.

Les détails des futures APU A Series étant encore sous embargo, et l'abandon éventuel du support d'une technologie initialement prévue ayant peu de chances d'être discuté officiellement, nous n'avons bien entendu pas cherché à creuser le sujet en associant Kaveri à la GDDR5M. Nous estimons plus que probable qu'AMD avait prévu de l'utiliser pour Kaveri mais ceci reste de la spéculation de notre part.

Ce qui n'est plus de la spéculation par contre c'est que la GDDR5M est bel et bien morte et enterrée. Joe Macri nous a ainsi expliqué qu'il s'agissait d'une "superbe mémoire" qui se présentait extrêmement bien au départ. Très prometteuse, elle allait permettre de gagner du temps par rapport à l'arrivée des mémoires Wide I/O2, HBM ou encore HMC, et 2 industriels avaient pris la décision de la développer et de la produire.

C'est le point central du destin de cette GDDR5M puisque dans l'industrie de la DRAM, il est nécessaire qu'au moins deux sources d'approvisionnement soient confirmées pour qu'une technologie puisse évoluer vers une existence commerciale. Sans quoi les risques sont bien trop élevés au niveau la disponibilité ou encore de la tarification. C'est ce qui a tué dans l'uf le développement de la GDDR5M.

Les deux industriels qui s'étaient penchés dessus étaient Hynix et Elpida. Or, il y a presque deux ans, Elpida a dû annoncer sa banqueroute et sa mise sous protection par les autorités de régulation financières japonaises. Celles-ci ont mis fin à tous les nouveaux projets dont la GDDR5M. Ne restait alors que Hynix, et malheureusement aucun autre fabricant de DRAM, par exemple Micron, n'a voulu prendre le relais et se lancer dans l'aventure.

Si nos spéculations sont correctes, vous imaginerez sans difficulté que cette faillite d'Elpida a ainsi pu avoir des répercussions importantes pour AMD et Kaveri.