Intel parle du Nehalem et de l'après SSE

Intel a profité dune conférence téléphonique pour faire le point sur sa roadmap serveur et desktop. Premier point, lItanium nest pas mort et Intel lancera au cours du second semestre Tukwila, une nouvelle évolution gravée en 65nm qui sera dotée de pas moins de 2 milliards de transistors répartis entre 4 core et 30 Mo de cache. Intel estime que le gain de performances par rapport à la génération précédente sera supérieure à 2x, mais il ne faut pas perdre de vue que cette dernière nest « que » dual-core.

Le géant de Santa Clara a également officialisé le Dunnington, premier processeur 6 core. Destiné à la plate-forme quadri-socket Caneland, ce processeur dérivé de larchitecture Core sera composé de 1.9 milliards de transistors gravés en 45nm. Pas moins de 16 Mo de cache L3 seront intégrés, le tout devant voir le jour au cours du second semestre.

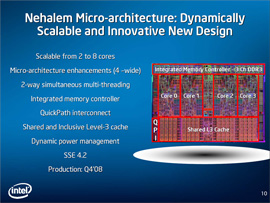

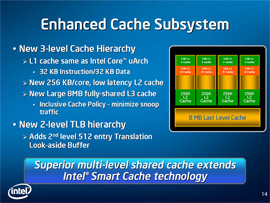

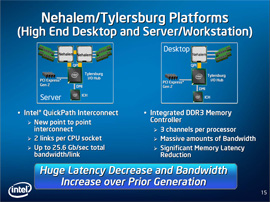

Le Nehalem était bien entendu de la partie, un an après les premiers détails officiels quIntel avait déjà donné. Cette nouvelle architecture qui entrera en production au quatrième trimestre 2008 disposera, cest confirmé, dun cache de niveau 3 partagé de 8 Mo, en sus de 256 Ko de L2 et de 64 Ko de L1 par core. Le SMT, permettant de faire tourner 2 thread par core, est également de la partie comme précédemment annoncé et le contrôleur mémoire intégré gérera 3 canaux DDR3-1333.

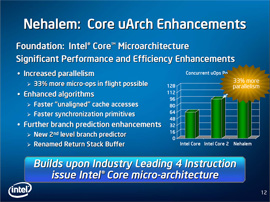

Nehalem est annoncé comme flexible en terme de nombre de core, c'est-à-dire que ces derniers peuvent varier de 2 à 8, même si dans un premier temps il semble que Intel se contentera de versions 2 et 4 core. Intel met en avant des avancées en termes dIPC (instruction par cycle dhorloge) par rapport à larchitecture Core, notamment grâce à la gestion de 128 micro-ops concurrentes contre 96 sur Core, mais aussi des améliorations des accès au cache et de la prédiction de branchement. De nouvelles instructions SSE4 seront également de la partie, spécifiquement destinées au traitement du texte (non, pas pour Word).

Si 2009 devrait voir larrivée de la déclinaison 32nm du Nehalem, le Westmere, la prochaine architecture Sandy Bridge qui utilisera la même finesse de gravure est pour sa part prévue pour 2010. Il intégrera lAVX (Advanced Vector Extension), qui nest ni plus ni moins que le successeur du SSE. Les registres passeront de 128 à 256 bits et permettra de travailler sur 3 opérandes, une idée qui sera également intégrée dans le SSE5 déjà annoncé par AMD. AVX contre SSE5, le combat de 2010 ?

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 04/05: Un Coffee Lake 8 coeurs en préparat...

- [+] 27/04: Le 10nm d'Intel (encore) retardé, l...

- [+] 26/04: Jim Keller rejoint... Intel !

- [+] 23/04: MAJ de notre test des Ryzen 7 2700X...

- [+] 20/04: MAJ de notre comparatif CPU géant

- [+] 19/04: AMD Ryzen 2700X et 2600X : Les même...

- [+] 19/04: 2008-2018 : tests de 62 processeurs...

- [+] 13/04: Les AMD Ryzen Pinnacle Ridge en pré...

- [+] 10/04: LGA4189 pour les Xeon Ice Lake !