Actualités informatiques du 13-08-2014

- Les connecteurs USB réversibles ratifiés !

- OCZ ARC 100, Barefoot 3 plus abordable

- Nvidia présente Denver

Archives

| Août 2014 | ||||||

|---|---|---|---|---|---|---|

| L | M | M | J | V | S | D |

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

Les connecteurs USB réversibles ratifiés !

Publié le 13/08/2014 à 16:28 par Guillaume Louel

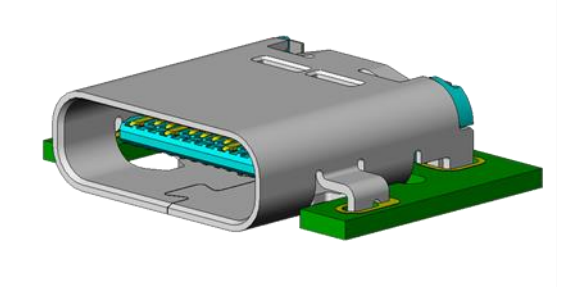

L'USB-IF vient d'annoncer la ratification de la spécification pour le nouveau type de connecteurs USB « Type-C ». Pour rappel, ces connecteurs sont inspirés du design des connecteurs « Lightning » d'Apple dans le sens ou ils sont réversibles, la prise pouvant s'insérer dans les deux sens.

Le nouveau connecteur interne que l'on retrouvera sur les cartes mères/PC

Outre l'aspect pratique, ce nouveau connecteur est, le communiqué l'indique, compatible à la fois avec les futurs standards USB 3.1 (qui doublent le débit théorique à 10 Gbps) ainsi qu'avec l'USB Power Delivery (jusqu'à 100 watts dans les deux sens). Une bonne nouvelle tant l'USB Power Delivery reposait jusqu'ici sur les connecteurs classiques.

Les nouveaux connecteurs externes (ici sur un câble).

La spécification est disponible en ligne sur le site de l'USB-IF , de nouveaux adaptateurs seront bien entendus disponibles pour assurer la transition, le Type-C devenant la solution unique pour l'avenir, tirant un trait sur tous les types précédents (Type A/B, mini /micro etc ). Ces nouveaux connecteurs devraient faire leur apparition dans les mois à venir, sans plus de précision.

OCZ ARC 100, Barefoot 3 plus abordable

Publié le 13/08/2014 à 16:15 par Marc Prieur

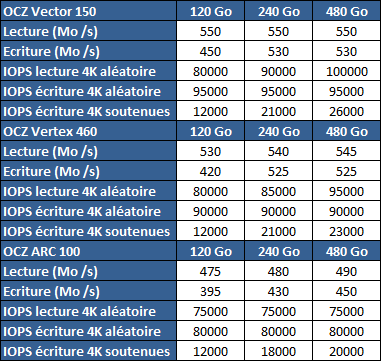

OCZ lance une nouvelle série de SSD, les ARC 100. Déclinés en versions 120, 240 et 480 Go, ils constituent la 5è gamme de SSD OCZ déclinée autour de du contrôleur Indilinx Barefoot 3 après le Vertex 460 lancé en début d'année.

Comme les Vector 150 et Vertex 460, il est associé à de mémoire MCL Toshiba 19nm toggle, chose on ne peut plus logique puisque la division SSD de OCZ a pour rappel été reprise par Toshiba. Il s'agit plus précisément de mémoire A19nm, disposant d'une densité accrue.

Histoire de trouver un point de différentiation, les performances sont revues légèrement à la baisse par rapport au Vertex 460 :

Les niveaux obtenus restent toutefois très bons, mais il faut noter que sur les Barefoot 3 les performances en écritures ne sont pas valables sur l'intégralité du SSD mais uniquement sur les pages Flash qui peuvent être écrites en mode "SLC" (cf. cette page), ce qui permet à OCZ de gonfler les chiffres en écriture sur les petites capacités.

Alors que les Vector 150 disposent d'une garantie de 5 ans, celle des Vertex 460 est de 3 ans et il est probable qu'il en soit de même pour les ARC 100. Côté tarif il est question d'environ 0.5 / Go.

L'arrivée des ARC 100 marque le retour d'OCZ sur un segment tarifaire plus agressif qui avait été abandonné suite au déboires passés de la marque. Reste qu'en l'état les différences entre les modèles ne justifient pas vraiment la présence de plus de deux gammes en Barefoot 3 + MLC Toshiba 19nm.

Nvidia présente Denver

Publié le 13/08/2014 à 13:10 par Guillaume Louel

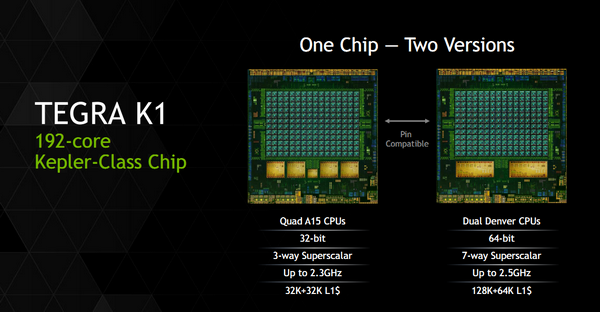

Après une annonce quelque peu confuse au CES d'un Tegra K1 en deux versions, Nvidia a profité de la conférence Hotchips pour donner quelques petits détails sur son architecture processeur Denver.

Pour rappel, Denver est une implémentation customisée de l'architecture 64 bits ARMv8. Il s'agira des premiers cores ARM custom proposés par Nvidia qui utilisait jusqu'ici des curs génériques ARM (Cortex-A9 dans Tegra 3, Cortex-A15 dans Tegra 4, etc ) dans ses puces Tegra. Il s'agit de la seconde architecture ARMv8 custom présentée pour l'instant, la première étant celle d'Apple (Cyclone) utilisée dans les ses SoC A7. En pratique, une version spéciale des Tegra K1 sera disponible avec deux curs Denver (contre quatre curs Cortex-A15 pour la version 32 bits du Tegra K1).

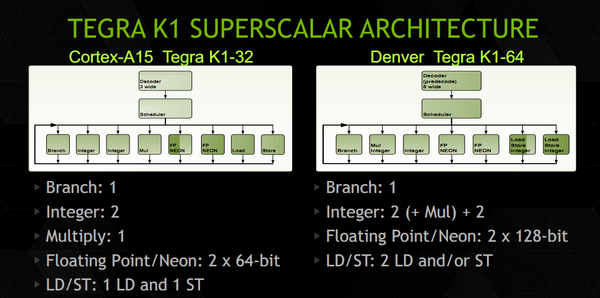

La présentation de Nvidia ne rentre pas forcément dans un très haut niveau de détails, mais l'on y trouve quelques grandes lignes intéressantes. D'abord sur les unités d'exécution :

Nvidia présente ce slide qui met face à face les unités d'exécution d'un cur Cortex-A15 et d'un cur Denver. On retrouve certains changements liés à ARMv8 comme le passage des unités Neon/FP (les instructions SIMD d'ARM) de 64 à 128 bits, et d'autres plus intéressants. On retrouve sept ports qui incluent un plus grand nombre d'unités, par exemple au lieu d'un seul port pour les Load et les Stores, les deux ports sont capables d'effectuer les deux types d'opération, et aussi des instructions entières. Le détail le plus important concerne surement le décodeur qui indique une phase de « prédécodage ».

De manière classique sur les Cortex-A, les instructions ARM sont décodés, réordonnées, (le principe de l'OoO, Out of Order), les registres sont renommés, puis les instructions sont dispatchées aux unités d'exécution. A l'inverse chez Intel, le jeu d'instruction x86 étant très large, les instructions x86 sont traduites en micro opérations - une sorte de jeu d'instruction réduit, interne aux unités d'exécutions avant de subir les mêmes opérations de changement d'ordre, renommage de registres et de dispatch. Le prédécodage laisse penser que Denver utilise lui aussi un jeu d'instruction interne différent. Plus surprenant, Denver pourrait être une architecture hardware in-order.

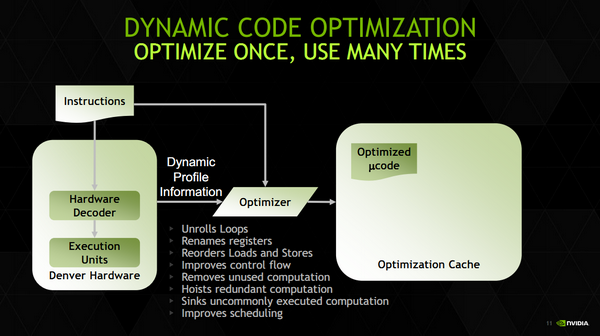

C'est en tout cas ce que laisse penser la fonctionnalité la plus originale de Denver, ce que Nvidia appelle « Dynamic Code Optimization ». En pratique, il s'agit d'une couche logicielle qui fonctionne dans un espace mémoire (128 Mo) protégé, géré directement par le firmware et qui n'est pas accessible au système d'exploitation. Ce code logiciel fait tourner des threads cachés du reste du système dans ce que Nvidia appelle des « hidden time slices », on suppose qu'il s'agit d'un contexte dédié à l'utilisation de DCO. Que fait donc cet optimiseur ?

La liste des opérations ne trompe pas, on retrouve ici toutes les opérations effectuées par les frontend des processeurs Out of Order modernes, comme le réordonnancement d'instructions ou le renommage de registre. On trouve même quelques fonctionnalités un peu plus avancées que l'on a déjà vues chez Intel et AMD comme le dépliage de boucles.

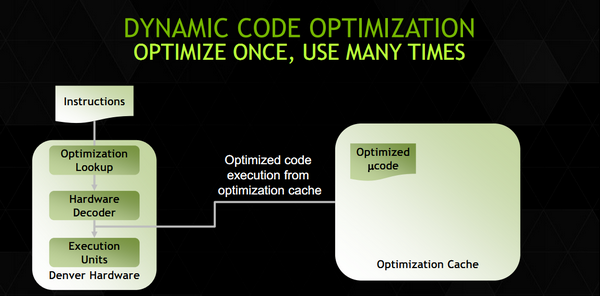

En pratique le fonctionnement est d'après les informations que nous avons - ainsi : le code ARM est décodé en micro instructions puis envoyé directement aux unités d'exécution. En parallèle, ce code est envoyé aux threads cachés DCO qui vont effectuer un décodage « OoO » optimisé du code ARM en micro instructions (l'optimisation est effectuée en profitant d'informations de profilage statique récupérées par l'exécution du code). Ce code est ensuite stocké dans le cache en mémoire principale de 128 Mo que nous évoquions plus tôt. La prochaine fois que ce segment de code se représentera, le code optimisé en micro instructions est récupéré du cache mémoire et exécuté directement à la place du code décodé en hardware.

Pour résumer tout cela en une phrase, Denver implémente de manière logicielle l'OoO d'habitude implémentée de manière matérielle dans les autres processeurs. Si cela vous dit quelque chose, c'est probablement parce que ce type de design avait été utilisé par Transmeta pour ses Crusoe. Une différence notable avec les Crusoe est que Denver peut exécuter directement le code ARM via un décodeur matériel (de manière moins performante, et nous le supposons, in-order). En supprimant un frontend couteux en transistors, on peut sur le papier disposer d'une plus grande marge de transistors à placer ailleurs (unités d'exécution ou même GPU), ou réduire la consommation. A l'inverse, une architecture « in-order » n'est pas, lorsqu'elle est en fonctionnement, particulièrement efficace d'un point de vue énergétique lorsqu'elle doit attendre après des instructions mémoires.

Reste que si ce genre d'architecture peut être très efficace dans des benchmarks arithmétiques, en pratique tout dépendra de la variété de code utilisée et de l'efficacité de cet « OoO » logiciel. DCO semble capable de travailler sur des blocs de taille variables pouvant aller jusqu'à 1000 micro opérations. Nvidia a ajouté un cache d'instruction de niveau 1 de 128 Ko qui peut contenir les blocs les plus utilisés, tandis que les autres seront stockés en mémoire (beaucoup plus lente) en attente d'être exécutés de nouveau.

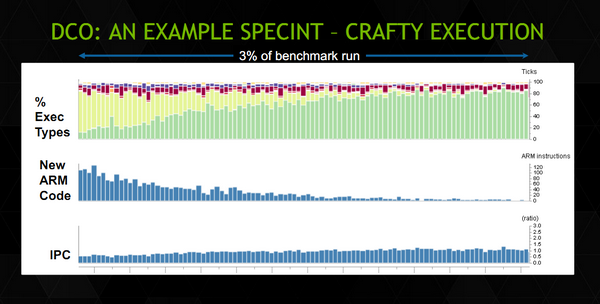

Nvidia donne un exemple du fonctionnement en pratique. Sur ce schéma, on peut voir en haut en vert le « type » d'exécutions qui ont lieu sur les curs Denver durant le début d'un benchmark SpecINT 2k. Malheureusement, il n'y a pas d'échelle de temps mais l'on note en vert les instructions optimisées, en vert pale les instructions décodées en hard, et en pourpre/violet les instructions exécutées par DCO. Leur nombre est non négligeable particulièrement en début de benchmark. La proportion d'instructions issues du décodeur matériel décroit au fur et à mesure, remplacées au fur et à mesure par des instructions « optimisées ». On peut voir l'augmentation de l'IPC au fur et à mesure en bas.

L'architecture de Denver est pour le moins originale et les quelques détails donnés durant la conférence Hot Chips ne permettent pas vraiment de se faire une idée des performances réelles de la puce. Nvidia avance quelques benchmarks ou il place, dans des tests arithmétiques (et donc répétitifs, le cas le plus avantageux pour ce type d'architecture), Denver au niveau d'un Celeron Haswell 2955U (1.4 GHz, 15 watts) sans préciser le TDP ou la fréquence du Denver utilisé. Les performances dans un environnement réel ou cohabitent de multiples applications dont le code n'est pas forcément fait de traitements répétitifs dépendront de l'efficacité de cet OoO logiciel. La taille du cache d'instruction et sa rapidité pouvant devenir une ressource critique pour les performances.

La disponibilité des K1 Denver n'a pas été précisée, indiquée simplement à « plus tard cette année » par le constructeur.