Actualités ssd

Samsung SSD 650, un 850 EVO allégé

SSD M6V chez Plextor

OCZ annonce les SSD Trion 100

Samsung 850 EVO et 850 Pro en version 2 To

JMicron prépare un contrôleur SSD PCIe abordable

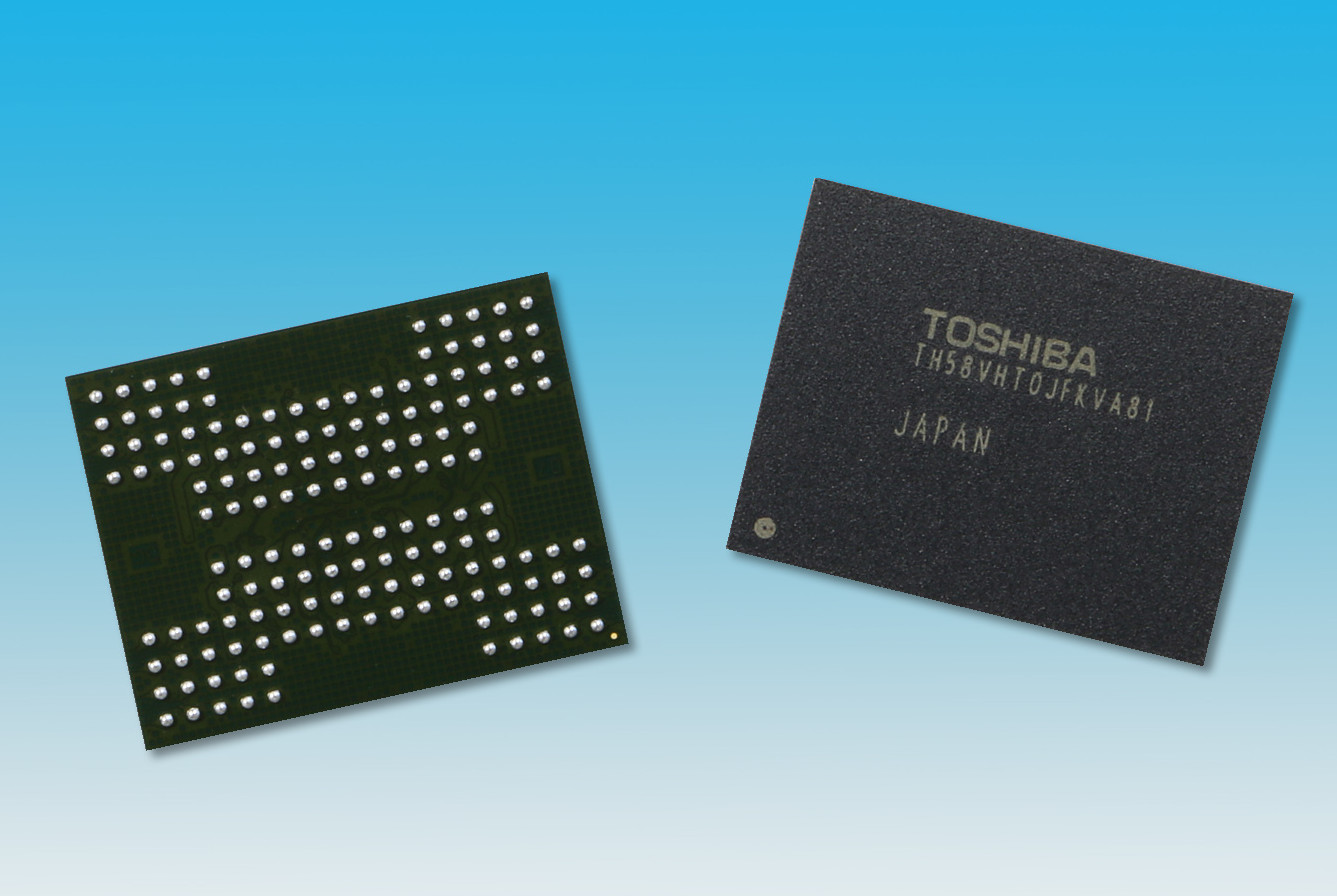

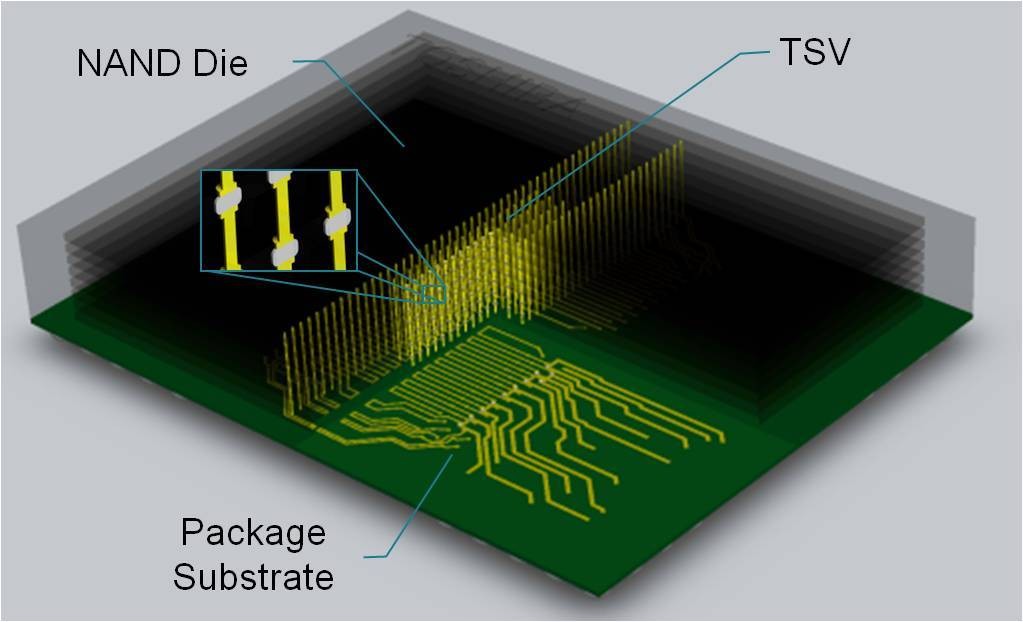

16 die NAND en TSV empilés par Toshiba

Toshiba vient d'annoncer une puce de Flash NAND intégrant pas moins de 16 die empilés et reliés via la technologie TSV (Through Silicon Via), une première. Pour rappel cette technologie également utilisée sur la HBM consiste en de petits trous creusés dans les dies et remplis de cuivre, de manière à créer une voie de communication directement à travers une puce.

Empiler autant de die Flash NAND est déjà possible, Sandisk par exemple l'avait déjà fait pour ses cartes SD 512 Go ou Samsung pour ses SSD de 2 To, mais en utilisant des connexions externes entre les dies. En permettant des connexions plus courtes, le TSV permet d'atteindre des débits plus rapides et/ou de baisser la consommation.

La version 16 die affiche une capacité de 256 Go dans 14x18x1.9mm, avec 8 die empilés on tombe à 1,35mm de hauteur.

3D NAND 32 Go TLC chez SanDisk et Toshiba

SanDisk et Toshiba, qui sont pour rappel associés pour la production de NAND au sein de la joint-venture Flash Forward, viennent d'annoncer une nouvelle étape côté NAND 3D. Après l'annonce en mars d'une puce de 128 Gbits (16 Go) en MLC, c'est au tour d'une puce 256 Gbits (32 Go) en TLC, soit avec 3 bits stockés par cellule au lieu de 2 en MLC, de voir le jour.

Dans les deux cas c'est une structure verticale de type BiCS (Bit Cost Scalable) qui est utilisée, avec 48 couches. Cette mémoire devrait arriver sur le marché en 2016 et sera produite dans la nouvelle Fab2 située à Yokkaichi au Japon qui sera terminée au premier semestre de cette même année.

Un bug de TRIM sous Linux pour les SSD Samsung ? Non

Mise à jour : Finalement il ne s'agissait pas d'un bug côté SSD mais d'un bug du noyau Linux pour lequel Samsung a soumis un patch . Tout est bien qui finit bien !

Spécialisée dans les moteurs de recherche, Algolia vient de publier un billet concernant une problématique qu'ils ont rencontrée sur leurs serveurs tournant sous Linux avec les SSD Samsung. La commande TRIM était en effet mal interprétée sur ces disques ce qui entrainait une corruption des fichiers.

Algolia utilise des Samsung 840 Pro, 850 Pro, ainsi que des SM843T et PM853T, tous présentent ce problème qui a contrario n'a pas été rencontré avec des Intel S3500, S3700 et S3710. Il est à noter qu'il ne s'agit pas du premier souci de TRIM rencontré sous Linux pour les SSD Samsung puisque libata avait été patché en mai par un développeur de chez Oracle afin d'empêcher l'utilisation du Queued Trim sur tous les Samsung SSD 8*, les Crucial/Micron M500, M550 et MX100 faisant également partis de la liste des bannis sauf si ils sont en firmware MU02 pour les deux derniers.

Pour rappel le Queued Trim a été introduit avec le SATA 3.1, cette fonction permet à la commande TRIM de faire partie d'une file d'attente de commande ce qui permet de réduire les pertes de performances lorsqu'elle intervient. Algolia précise pour sa part que le problème concerne bien la version classique (un-queued) de TRIM sous Linux, et être actuellement en contact avec Samsung afin de permettre une résolution du bug. En attendant, si vous avez des serveurs sous Linux tournant des SSD Samsung, il est donc plus prudent de désactiver le TRIM.

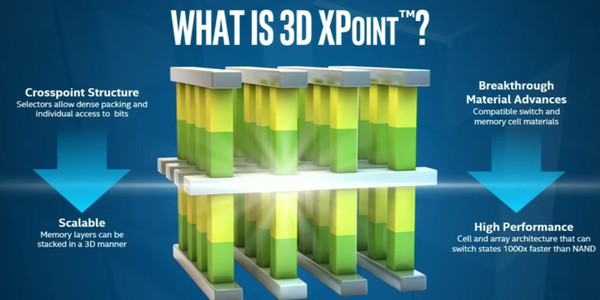

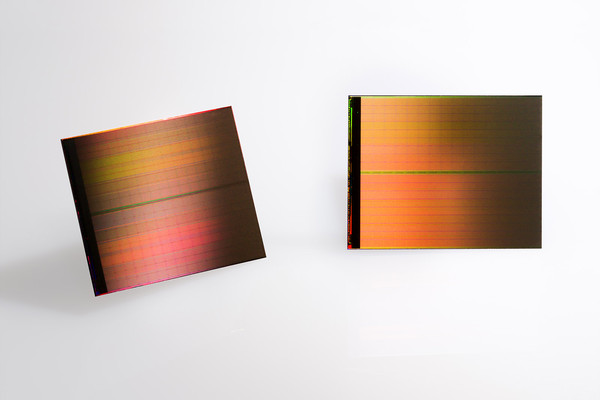

Intel et Micron annoncent la ReRAM 3D XPoint

Intel et Micron viennent d'annoncer conjointement une nouvelle technologie de mémoire baptisée « 3D XPoint » (à prononcer « 3D Crosspoint »). Les deux sociétés ont présenté cette technologie comme une nouvelle classe de mémoire, à mi-chemin entre la DRAM et la NAND. Il s'agit d'une technologie mémoire non volatile (comme la NAND) mais annoncée comme significativement plus rapide.

Les deux sociétés ont été relativement muettes sur les détails mais on peut tirer quelques informations des grandes lignes qui ont été révélées. Techniquement on peut considérer 3D XPoint comme une « variante » de la NAND dont elle modifie les deux éléments principaux, le switch et la cellule de stockage.

Au niveau de la cellule de stockage, et contrairement à de la NAND, on ne retrouve plus de transistor : les données ne sont plus stockées sous forme d'électrons mais en utilisant le changement de propriétés des matériaux utilisés pour créer les cellules (les blocs jaunes/verts sur le schéma). Le type de matériaux utilisés (deux, étant donné les deux couleurs ?) n'est malheureusement pas précisé et l'on n'aura pas eu plus de détails sur le fonctionnement exact durant la présentation, même si Intel a confirmé à nos confrères d'EETimes qu'il s'agissait bien de "changement de résistance", ce qui permet de classer 3D XPoint comme une variante de ReRAM. On sait que Micron s'intéresse à la ReRAM depuis un moment, par exemple avec cette recherche avec Sony, mais a l'époque le concept utilisé était différent, utilisant des transistors. D'un point de vue structurel, on semble s'approcher un peu plus de ce que proposait Crossbar, même si là encore l'absence de transistors est l'une des différences principale.

L'autre innovation se situe au niveau du switch qui permet de sélectionner les cellules auxquelles on souhaite accéder en faisant varier la tension, un mécanisme là aussi dénué de transistor. En pratique, exit le concept de blocs de la NAND, on peut lire et écrire les bits de données individuellement ! Qui plus est, il est possible de superposer ces structures switch/cellules en hauteur pour améliorer la densité.

Les deux sociétés se félicitent de gros chiffres qui malheureusement ne sont pas expliqués, avançant des performances 1000x supérieures à la mémoire NAND, sans préciser de quelle NAND il s'agit, ou même tout simplement du type d'opération concerné ! On suppose, à la lecture de certains documents qu'Intel ne parle pas de débits mais de latence puisqu'il annonce que contrairement à la NAND dont la latence est mesurée en microsecondes, la latence de XPoint est mesurée en nanosecondes (une affirmation bien floue !) [MAJ : Un document dédié aux équipes marketing d'Intel - voir en commentaires - semble confirmer qu'il s'agit bien de la latence qui est utilisée pour le facteur de 1000x évoqué. Un facteur de 10x entre la latence XPoint et DRAM est également sous entendu. Le même document évoque, par rapport aux offres NVMe actuelles, un avantage de 10x sans plus de détails ce qui est déjà plus raisonnable]. On imagine en pratique que l'écart sera surtout le plus visible sur les écritures aléatoires - ce qui a été vaguement sous-entendu lors de la session de questions/réponses - ou l'écart avec la NAND parait le plus élevé d'un point de vue technique. La question de l'écart de performance sur les opérations de lectures a été écartée par les représentants des sociétés. On se félicitera tout de même (avec les mêmes réserves) du fait que l'endurance est annoncée comme 1000x supérieure à la NAND.

Par rapport à la mémoire DRAM, les sociétés ne qualifient cependant pas le niveau de performances, indiquant juste que la densité est 10 fois plus élevée.

Pour le reste les détails sont minces, aucune information sur le process de fabrication utilisé n'a été donnée par exemple (certains de nos confrères indiquent un process 20nm, mais nous n'avons pas pu confirmer l'information). Pour ce qui est de produits en pratiques, le premier sera une puce de 128 Gbit qui à l'intérieur superpose deux couches de cette nouvelle structure switch/cellule. Des échantillons de ces puces devraient être disponibles « cette année » tandis que côté produits finaux il faudra attendre 2016.

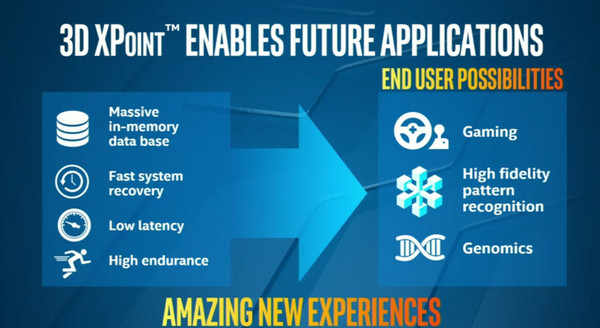

En pratique ces puces devraient pouvoir permettre de réaliser, côté grand public, des SSD PCI Express très rapides dans toutes les circonstances même si la question du prix a été éludée. Intel a cependant parlé de l'intérêt de cette mémoire pour le jeu en général, laissant penser qu'il y aura des applications grand public. Au-delà du stockage, c'est surtout côté serveur que cette mémoire devrait se présenter comme un tiers intermédiaire entre la DRAM classique et la NAND, autour des applications type « big data ». La manière dont ces produits se matérialiseront, ou s'interconnecteront, reste malgré tout floue. Intel et Micron proposeront chacun de leurs côté des produits issus de la technologie.

Sans plus de détails sur le cout de la technologie ou ses performances réelles il est difficile d'en tirer plus, d'autant que le représentant de Micron a indiqué que cette technologie ne remplacerait pas la NAND 3D en tant que produit (nous supposons que la NAND 3D gardera, au moins au début, un avantage de cout massif). Malgré tout, les innovations techniques semblent extrêmement intéressantes et pourraient remplacer à terme la NAND traditionnelle. Nous espérons qu'Intel dévoilera un peu plus de détails techniques lors son traditionnel Intel Developer Forum qui se tiendra cette année du 18 au 20 août.

Contrôleur NVMe x4 chez Phison

La marque de contrôleurs de mémoire flash vient de publier sur son site web les spécifications d'un nouveau modèle haut de gamme. Baptisée PS5007-E7, il s'agit d'un contrôleur SSD type NVMe (qui permet de connecter les SSD directement aux lignes PCI Express de la carte mère) qui s'interface en mode PCIe 3.0 x4. On pourra lui adjoindre 256 ou 512 Mo de cache DDR3.

Le contrôleur est annoncé comme compatible avec la version 1.1b de NVMe et est fabriqué en 28nm chez TSMC. Il supporte la mémoire MLC et TLC sur 8 canaux mémoires et 64 CE (jusqu'à 8 dies par canal via interleaving).

Côté performances, avec de la mémoire MLC, Phison annonce atteindre 2600 Mo/s en lecture (et la moitié en écriture) en performances séquentielles, et 300K/200K iops en lecture/écriture aléatoire. Des annonces de SSD PCIe tiers devraient donc arriver sous peu chez les partenaires de Phison, ce contrôleur devrait permettre de voir grossir l'offre des SSD NVMe qui se limite aujourd'hui principalement à Samsung et Intel. On notera que si JMicron a lui aussi annoncé travailler sur un modèle de contrôleur NVMe abordable, celui-ci se limite à une interface PCIe x2.