Intel Pentium 4 E « Prescott »

Publié le 02/02/2004 par Marc Prieur

La face visible du Prescott, suiteLa mémoire cache a également évolué au sein du Prescott. En effet, on passe de 8 à 16 Ko de cache de premier niveau dédié aux données, alors que le cache de second niveau passe pour sa part de 512 à 1024 Ko. Le doublement du cache L1 est annoncé comme très utile pour lHyperThreading, qui sest également vu améliorer en quelques points notamment via lajout de nouveaux types dinstructions pouvant être exécutées en parallèle ou encore via lamélioration de la co-gestion du cache L1 par les deux processeurs logiques.

Les instructions SSE3 sont la dernière évolution que nous traiterons dans cette partie. Ces dernières sont au nombre de 13. Il ne sagit pas dun nouveau jeu dinstructions à part entière mais plutôt dun complément aux jeux dinstructions existants :

- 1 instruction x87 (FPU) pour la conversion de flottants en entiers (fisttp)

- 3 instructions SIMD 128 bits pour la duplication de données (movsldup, movshdup, movddup)

- 1 instruction SIMD 128 bits pour le chargement de données non alignées (lddqu)

- 2 instructions SIMD 128 bits pour laddiction en calcul vertical (addsubps, addsubpd)

- 4 instructions SIMD 128 bits pour laddition / soustraction en calcul horizontal (haddps, hsubps, haddpd, hsubpd)

- 2 instructions dédiées à la synchronisation des threads (monitor, mwait)

Bien entendu, contrairement aux autres améliorations de la microarchitecture du Prescott, lexploitation des instructions SSE3 passe obligatoirement par de nouveaux programmes codés et compilés de manière à pouvoir en tirer partie. En labsence dapplications, on ne sait pas quel sera le gain de performances, toutefois Intel annonce un gain pouvant atteindre 10% en compression MPEG-4 via lutilisation de linstruction lddqu ... Wait & See !

La face cachée du Prescott, suite

Où sont passés les 125 Millions de transistors ? En effet, si ces améliorations sont coûteuses en terme de transistors, il nen reste pas moins quelles ne permettent pas datteindre un tel chiffre. En fait, le Prescott contient plusieurs fonctions qui ne sont pas activées dans la version commerciale actuelle, à savoir LaGrande dune part, qui est un processeur de sécurité TCPA (Trusted Computing Platform Alliance) qui servira de base au fameux projet Palladium de Microsoft, et Yamhill dautre part, qui est une extension 64 bits de lactuel jeu dinstructions x86 compatible avec lAMD64.

Où sont passés les 125 Millions de transistors ? En effet, si ces améliorations sont coûteuses en terme de transistors, il nen reste pas moins quelles ne permettent pas datteindre un tel chiffre. En fait, le Prescott contient plusieurs fonctions qui ne sont pas activées dans la version commerciale actuelle, à savoir LaGrande dune part, qui est un processeur de sécurité TCPA (Trusted Computing Platform Alliance) qui servira de base au fameux projet Palladium de Microsoft, et Yamhill dautre part, qui est une extension 64 bits de lactuel jeu dinstructions x86 compatible avec lAMD64.

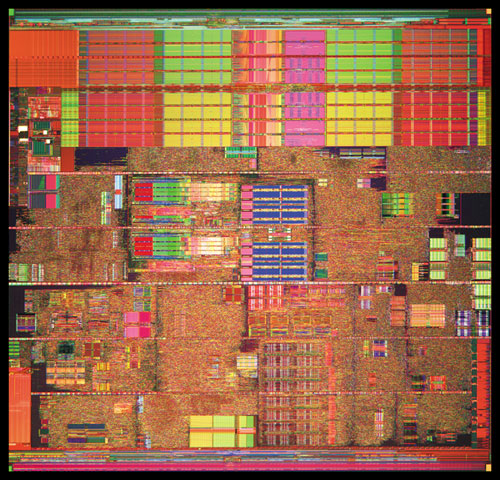

Selon les analyses du die du Prescott de Hans de Vries de Chip Architect datant de Mars 2003, ce dernier laisse apparaître quil dispose en fait de deux blocs dexécution dentiers, chacune disposant de 16 Ko de cache L1. Sagit-il dune amélioration de lHyperThreading basée sur deux blocs dexécutions dentiers, chacun pouvant exécuter deux threads (pour un total de 4), ou de deux unités qui fonctionnent de paire pour les calculs en 64 bits ? Chip Architect penche pour cette dernière hypothèse. De plus, ils ont également pu définir où se trouvait la partie du Prescott destinée à la technologie LaGrande. Enfin, contrairement à ce quindique Intel, le trace cache a été augmenté sur le Prescott, puisque selon sa taille il passe en fait de 80 à 128 Ko.

Selon les dernières rumeurs, la technologie Yamhill pourrait être activée au sein dun produit commercial dans les mois à venir, mais rien na encore filtré en ce qui concerne une éventuelle activation de la technologie LaGrande. Le Prescott cache-t-il dautres secrets ?

Sommaire

1 - Introduction

2 - La face visible et cachée du Prescott

3 - Les P4E, Compatiblité

4 - Température et Overclocking

5 - L'archi en pratique cache & instructions

6 - L'archi en pratique HyperThreading

7 - 3d Studio Max et Maya

2 - La face visible et cachée du Prescott

3 - Les P4E, Compatiblité

4 - Température et Overclocking

5 - L'archi en pratique cache & instructions

6 - L'archi en pratique HyperThreading

7 - 3d Studio Max et Maya

Vos réactions

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 04/05: Un Coffee Lake 8 coeurs en préparat...

- [+] 27/04: Le 10nm d'Intel (encore) retardé, l...

- [+] 26/04: Jim Keller rejoint... Intel !

- [+] 23/04: MAJ de notre test des Ryzen 7 2700X...

- [+] 20/04: MAJ de notre comparatif CPU géant

- [+] 19/04: AMD Ryzen 2700X et 2600X : Les même...

- [+] 19/04: 2008-2018 : tests de 62 processeurs...

- [+] 13/04: Les AMD Ryzen Pinnacle Ridge en pré...

- [+] 10/04: LGA4189 pour les Xeon Ice Lake !