Les contenus liés aux tags ASML et 7nm

Afficher sous forme de : Titre | FluxPremières puces en 7nm pour IBM !

Alors qu'IBM a revendu son activité fabrication de semi-conducteurs à Global Foundries en octobre dernier (un rachat qui s'est finalisé le premier juillet de cette année), IBM vient annoncer avoir produit une puce de test fonctionnelle en 7nm, une première que rapportent nos confrères d'EETimes .

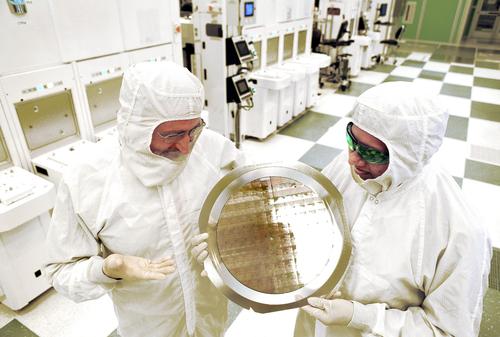

Si IBM réalise l'annonce, en pratique la puce a été fabriquée dans un centre de recherche du SUNY Polytechnic Institute financé en partie par l'état de New York et divers partenariats privés. Virtuellement toutes les sociétés du milieu participent puisque l'on retrouve dans la liste des sociétés, outre IBM, Intel, TSMC, Samsung, GlobalFoundries ou encore ASML. C'est à cet endroit que l'on retrouve par exemple l'effort de recherche du Global 450mm Consortium qui travaille sur la future transition aux wafers de 450mm (contre 300 actuellement, un mouvement qui a pris un coup d'arrêt ces dernières années).

Avant son rachat, IBM avait annoncé participer à hauteur de 3 milliards (sur 5 années) au développement de futures puces, tandis qu'en début d'année, suite au rachat par GloFo, IBM avait regroupé ses 220 ingénieurs restants sur le site de SUNY sous l'égide « IBM Research ».

Historiquement, IBM a toujours aimé jouer au jeu des annonces et continue ici dans sa tradition. En pratique il s'agit d'une première puce de test qui inclut transistors, cellules SRAM et interconnexions, les blocs essentiels même si, évidemment, on reste cependant très loin de la production en volume.

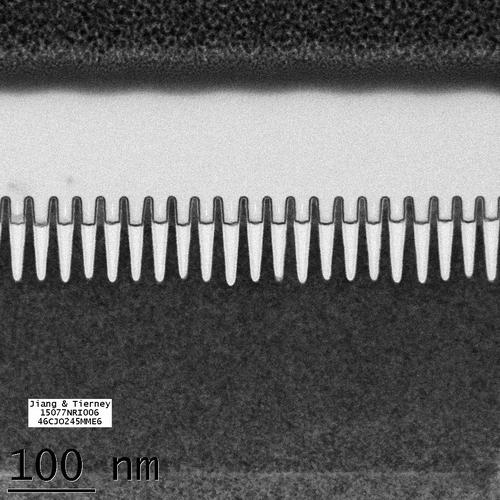

Les transistors FinFet 7nm vus au microscope

Au-delà de l'effort, on s'intéressera surtout aux choix réalisés par IBM pour son process, qui repose cette fois sur l'EUV. Nous avions eu l'occasion d'en parler, l'EUV va mieux et si une introduction est possible en cours de node pour le 10nm, TSMC et les autres visent une introduction ferme pour le 7nm et de ce côté IBM ne déroge pas.

Plus surprenant, les choix réalisés autour des structures et des matériaux. Alors que l'on s'attend probablement à voir d'autres structures que le FinFet introduites à 10 ou 7nm par Intel, IBM utilise ici des structures FinFet également, la différence s'effectuant sur les matériaux avec le retour du silicium-germanium (SiGe) étiré pour le canal, sur substrat en silicium. Ce n'est pas la première fois que le germanium apparait dans les process, même si aujourd'hui on le trouve principalement dans les process analogiques/radio . L'utilisation du SiGe étiré dans les semi-conducteurs est une innovation d'IBM et il est assez surprenant de le retrouver sur un process si avancé, qui plus est en EUV. D'autant que côté densité, les transistors peuvent être espacés de 30nm ce qui permettrait, par rapport au 10nm qui était en développement par IBM, d'augmenter la densité de 50%.

Développer un process « clef en main » - c'est comme cela qu'il est décrit par IBM qui dit avoir optimisé non seulement l'EUV, le dépôt du SiGe mais aussi les autres étapes du process comme l'interconnexion (BEOL) ne manque évidemment pas d'ironie mais nos confrères d'EEtimes notent qu'IBM fera profiter logiquement de ses travaux de recherche à GlobalFoundries qui pour rappel dispose d'une exclusivité de 10 années pour la production des processeurs serveurs d'IBM. Nos confrères sous entendent que Samsung pourrait également profiter de ces travaux, en se rappelant aux bons souvenirs de l'abandonnée Common Platform qui liait les trois sociétés.

Rien n'en est cependant moins sur puisque pour rappel, Samsung avait développé son propre process 14 nm sans IBM qui aura au final sauté ce node. Le fondeur coréen avait ensuite partagé son 14nm en intégralité avec GlobalFoundries. Pour le 10nm, IBM avait travaillé également sur son propre process que l'on retrouvera vraisemblablement tel quel chez GlobalFoundries. Les trois sociétés semblent cependant être restées en bons termes et l'on imagine que si la solution 7nm d'IBM est plus intéressante que les efforts développés en internes, ces sociétés continueront de mutualiser leurs efforts pour une éventuelle mise en production, que l'on n'attend pas de toute manière avant 2018 ou 2019. Ce que fera Samsung en 10 nm nous donnera peut-être un indice. Pour l'instant, si le constructeur a montré un wafer 10 nm, et indiqué qu'il s'attend à lancer la production en volume fin 2016, il n'a rien dévoilé sur la technique

ASML vend 15 machines EUV à Intel

La société ASML s'est fendu hier d'un communiqué de presse pour indiquer avoir signé un accord important pour la vente de machines de lithographie EUV. Nous étions revenus sur le sujet à la fin du mois dernier, après de long et multiples retards, cette technologie de lithographie nouvelle génération avait effectué quelques progrès substantiels, notamment chez TSMC, qui avait commandé deux machines NXE:3350B livrables cette année, des machines dédiées au 10nm.

Le communiqué d'ASML indique que la firme néerlandaise a trouvé un accord avec un de ses « gros client américain » pour livrer, dans un délai non précisé, 15 machines EUV. Deux de ces machines au moins seront de type NXE:3350B (10nm) et seront livrées cette année.

Il ne faut pas trop d'imagination pour deviner que le client en question est Intel. La société avait investi de manière importante dans ASML en 2012 même si elle restait prudente sur l'utilisation à venir de la technologie. Cet accord semble montrer un regain d'intérêt autour de l'EUV, même si à l'image de TSMC on s'attend probablement à un déploiement initial autour du 7nm.

La cadence de production des machines sera en effet étalée dans le temps. Six (à huit) machines NXE:3350 devraient être vendues cette année (deux à Intel, deux à TSMC et possiblement deux à Samsung qui était le troisième à avoir investi dans ASML en 2012). La production devrait s'intensifier progressivement puisque ASML table sur la production de douze machines en 2016, vingt-quatre en 2017 et 48 en 2018.

On notera enfin que si l'intérêt autour de l'EUV se porte aujourd'hui pour la fabrication de circuits logiques (processeurs), ASML compte également déployer l'EUV auprès des fabricants de mémoire DRAM dans un second temps. La production de mémoire flash NAND en EUV pourrait suivre avec un décalage de deux à trois ans selon le CEO d'ASML.

Quelques (bonnes !) nouvelles de l'EUV

Il y a quelques semaines se tenait le symposium « Advanced Lithography » du SPIE , une organisation internationale qui se focalise sur les challenges des technologies optiques et photoniques. Antony Ten de TSMC y a tenu une présentation ou il est revenu sur les avancées de la technologie de lithographie EUV (Extreme Ultraviolet Lithography).

L'EUV représente une évolution majeure, attendue depuis très longtemps dans le monde de la fabrication des semi-conducteurs. Déjà en 2002, Intel passait sa première commande auprès d'ASML pour une machine destinée à être livrée de 2005. 10 ans après cette échéance, l'avènement de l'EUV ne s'est toujours pas fait même si les dernières nouvelles rapportées par TSMC semblent plutôt prometteuses.

ASML est le fabricant d'outil qui a misé depuis le début sur les EUV, les autres acteurs ayant jeté l'éponge

Pour rappel, les processeurs sont fabriqués via ce que l'on appelle la photolithographie , un mécanisme qui permet, via de multiples opérations successives de transférer un masque sur une galette de silicium (communément appelé wafer) en utilisant une source lumineuse. Une version high tech d'une photocopieuse utilisée pour effectuer des réductions en quelque sorte. Actuellement la source lumineuse utilisée pose problème à l'industrie. D'une longueur d'onde de 193nm, elle est générée par des lasers à exciplexe (Argon/Fluor). Elle traverse une série d'éléments optiques pour la focaliser et sert à exposer des solutions photorésistantes qui ont été déposées préalablement pour dessiner sur le wafer. Des étapes qui prennent individuellement un certain temps et qui se multiplient pour chacune des couches qui composent les semi-conducteurs. De bout en bout (et cumulé à toutes les autres étapes de la chaine) il faut entre 2 et 3 mois pour obtenir un produit final.

Les réductions de géométrie successives (on atteint aujourd'hui 14/16nm et bientôt 10nm) complexifient les systèmes de réduction ce qui fait que chaque node apporte ses challenges depuis quelques années tant il devient impossible d'atteindre une netteté parfaite sous les 50nm. Pour compenser cela, des techniques (lithographie à immersion, multiple patterning, etc) sont utilisées ponctuellement pour les couches les plus importantes des puces. A l'approche du 10nm, une généralisation du multi patterning (qu'on pourrait simplifier à passer deux fois une feuille dans une photocopieuse quand on a un toner défaillant pour la rendre lisible) devient obligatoire ce qui augmente les temps, crée de nouveaux problèmes (d'alignement notamment), impose des règles de design strictes dans la manière dont les ingénieurs doivent placer les transistors, et donc augmente les couts.

Avec une longueur d'onde de 13.5 nm, l'EUV promet de simplifier les systèmes optiques (bien qu'elle engendre de nouveaux problèmes, évidemment !) mais c'est la génération de cette lumière qui pose problème. La technique en elle-même est très complexe puisque des goutes microscopiques d'étain sont envoyées dans une chambre sous vide avant d'être vaporisées individuellement par un laser extrêmement puissant pour produire cette lumière UV extrême qui est enfin collectée et focalisée avant de pouvoir être utilisée. Le tout à une cadence de 50000 goutes par seconde. Une complexité qui empêchait d'atteindre en production de manière constante il y a un an de cela - une puissance dépassant les 10 watts d'après TSMC durant le même symposium SPIE.

Le rachat de la société Cymer (qui fournit des sources lumineuses a l'industrie) par la société ASML (qui développe pour rappel les outils EUV) en 2013 semble cependant enfin porter ses fruits puisque ASML avait annoncé en juillet, puis en septembre que deux de ses clients avaient réussis à exposer plus de 500 wafers sur une durée de 24 heures via leur machine NXE:3300B, équipée alors d'une source d'une puissance de 40 watts.

Mieux, TSMC a annoncé durant le symposium SPIE avoir pu faire fonctionner pendant 24 heures d'affilée sa machine NXE:3300B équipée d'une source de 80 watts (la seule au monde équipée aujourd'hui de cette source puissante). Durant cette période elle a pu exposer 1022 wafers ce qui donne un rapport wafer/heure de 42.58, un chiffre qui s'approche fortement des « 50 à 100 par heure » qu'évoquait Mark Bohr en 2012 pour commencer à considérer l'EUV.

L'imposante NXE :3300B d'ASML

Des progrès importants qui ont valu à TSMC d'indiquer que l'utilisation de l'EUV pour le 7nm était une possibilité, et qu'introduire l'EUV dans un second temps dans son process 10nm, pour certaines couches critiques n'était pas impossible. La roadmap d'ASML promet d'augmenter la puissance à 125 watts à la fin du second trimestre avec la source de lumière du NXE:3350B et même 250 watts avant la fin de l'année.

Si ces nouvelles sont dans l'absolu très bonnes, et un pas en avant très important pour l'EUV, d'autres problèmes restent à régler. Le site SemiWiki rappelle que dans cette même présentation, TSMC indiquait que le taux de disponibilité de leur machine NXE:3300B version 40 watts, sur un test prolongé de 8 semaines n'était « que » de 55%. Un chiffre que l'on doit là encore à la source lumineuse, le générateur de goutes d'étain devant être remplacé tous les 4 jours. La prochaine version de la source lumineuse fournie par Cymer promet de résoudre ce problème même s'il faudra voir dans quelle mesure. Un système de nettoyage automatique de la partie optique devrait également améliorer la disponibilité.

Dans tous les cas cette avancée de l'EUV est importante et si d'autres problèmes périphériques seront à résoudre, une des plus grosses épines dans le pied de l'EUV semble enfin s'envoler, laissant penser que la technologie pourrait enfin s'approcher d'une mise en production possible ! Quelque chose que l'on pourra confirmer au milieu de l'année, TSMC ayant commandé deux machines NXE:3350B dédiées au 10nm. Ses deux machines existantes seront également mises à jour. Le tout dans le but de les aider à préparer une introduction éventuelle sur leur process 7nm, possiblement à l'horizon 2017.

Intel densifie sa SRAM 14nm et parle du 10 et 7nm

Intel profite de la conférence ISSCC (International Solid-State Circuits Conference) qui se tient cette semaine à San Francisco pour effectuer plusieurs annonces autour de ses process de fabrication. Le constructeur a donné à la presse un avant-goût de ses annonces, deux d'entre elles ont particulièrement retenu notre attention.

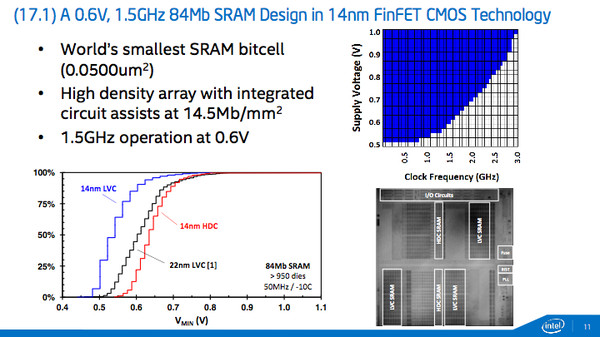

En premier lieu on retiendra la présentation d'un bloc de SRAM particulièrement optimisé pour la densité avec une taille de cellule de seulement 0.0500 µm², un record. Il s'agit d'une amélioration importante par rapport à la dernière présentation du constructeur qui évoquait des tailles de cellules de 0.0588 µm² lors du dernier IEDM fin 2014.

Il s'agit en pratique d'une puce de 84 Mbit (10,5 Mo) de SRAM optimisée pour un fonctionnement à 1.5 GHz à 0.6 Volts, même si en montant la tension d'activation à 1 Volt on peut atteindre 3 GHz. Si elle montre le bond en avant en densité lié au process, cette annonce tient surtout de la performance technique, le constructeur annonçant souvent des cellules de SRAM spécialisées et différentes de ce que l'on retrouve dans les produits commerciaux. Le constructeur avait ainsi annoncé pour le node 22 nm des cellules de 0.092 µm² optimisées pour la densités, mais ce sont des cellules de 0.108 µm² optimisées cette fois ci pour leur rapport performance/puissance qui sont utilisées dans les processeurs.

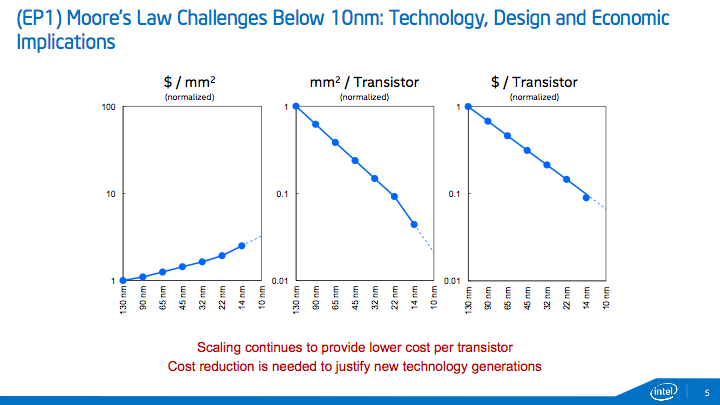

On retiendra enfin la description des challenges rencontrés au delà du 10 nm. Intel se félicite tout d'abord d'avoir atteint un coût par transistor plus faible qu'attendu sur le 14 nm, un chiffre toujours difficile à mettre en perspective qui plus est cette fois-ci avec les retards engendrés et les lancements décalés !

En ce qui concerne le 10nm, il semblerait que le constructeur ait - sans surprise - opté pour sa solution à lithographie à immersion « classique » en 193nm, et non pour une solution EUV comme Mark Bohr nous l'avait déjà indiqué en 2012 à l'occasion d'une interview. En fin d'année dernière TSMC avait également indiqué que l'EUV ne serait pas a l'heure pour leur propre process 10 nm.

Intel ne s'est pas encore étendu sur les changements techniques de son process 10 nm mais il avait été évoqué précédemment un recours plus fort au multiple patterning (exposition multiples). Déjà utilisé sporadiquement sur certaines couches critiques, son utilisation devrait être généralisée.

En ce qui concerne le 7 nm, un changement de la forme des structures (remplacer par exemple les FinFET par des microfils) et des matériaux utilisés (par exemple Arséniure de Gallium-Indium [InGaAs] ou Phosphure d'Indium [InP]) est envisagée mais Intel n'est pas encore prêt a livrer les détails de sa recherche.

On notera enfin que le constructeur indique avoir appris de ses problèmes concernant le 14 nm en ajoutant de nouvelles procédures internes pour détecter les problèmes rencontrés, particulièrement autour des masques qui semblent avoir posé beaucoup de problèmes au constructeur et être en partie coupable des retards. Le fondeur annonce qu'il a pour objectif d'avoir une transition vers le 10nm deux fois plus rapide que celle du 14nm, mais vu l'introduction de produits 14nm au compte-goutte 18 à 24 mois après le passage au 22nm on ne sait pas vraiment quels sont l'intervalle et la date de départ pris en compte pour le 14nm. Toujours est-il que le 10nm devrait pour sa part débarquer en 2016 !