Les contenus liés au tag AMD FX Next

Quelques infos sur Trinity et Vishera

AMD FX Next (Piledriver) sera FMA3

Quelques infos sur Trinity et Vishera

AMD vient de mettre à jour son guide d'optimisation logiciel pour la famille de processeur AMD 15h , c'est-à-dire les processeurs Bulldozer. Chose intéressante, ce guide donne quelques petites indications sur les améliorations intégrées dans la future APU Trinity (modèles 10h-1f) ainsi que le futur CPU Vishera (modèles 20h-2f).

AMD vient de mettre à jour son guide d'optimisation logiciel pour la famille de processeur AMD 15h , c'est-à-dire les processeurs Bulldozer. Chose intéressante, ce guide donne quelques petites indications sur les améliorations intégrées dans la future APU Trinity (modèles 10h-1f) ainsi que le futur CPU Vishera (modèles 20h-2f).

Au menu des nouveautés, on notera le support des jeux d'instructions FMA, F16C, BMI et TBM. Ce FMA là travaille en fait sur trois opérandes, comme celui qu'Intel utilisera sur Haswell, alors que le FMA4 supporté par les AMD FX actuels n'est pas compatible. Les instructions BMI et TBM permettent de simplifier les opérations de manipulations de bits alors que les instructions F16C (VCVTPH2PS and VCVTPS2PH) accélèrent la conversion d'une valeur en virgule flottante 32 bits vers 16 bits.

Le TLB du cache L1 d'instruction passe pour sa part de 32 à 64 entrées. Pour rappel les TLB (Translation Lookaside Buffers) sont les buffers qui stockent les correspondances entre les adresses virtuelles manipulées par les programmes, et les adresses physiques auxquelles elles se réfèrent.

Pour les processeurs AMD 10h-1f, soit les Trinity, AMD confirme la présence d'un maximum de 2 "compute units", soit 2 modules ou 4 curs. Sur les AMD 20h-2f, soit la génération de Vishera, il est question d'un maximum de 5 "compute units", soit 10 curs, une information qui avait déjà filtrée mais qui semble faire référence à Komodo qui a été annulé : Normalement Vishera reste à 8 curs. AMD fait état d'un contrôleur mémoire sur quatre canaux sur ce processeur, une information pour le moins étonnante puisqu'il ne serait pas possible de les utiliser sur un Socket AM3+ alors même que ce processeur est censé fonctionner sur cette plate-forme. Erreur de la documentation ou canaux uniquement accessible sur Socket G34 ? L'avenir nous le dira !

AMD FX Next (Piledriver) sera FMA3

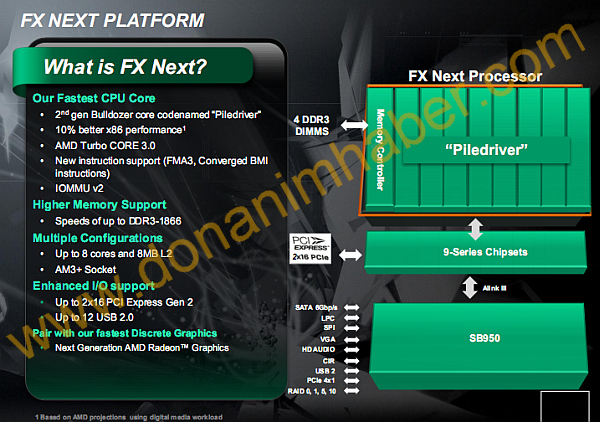

Alors que les AMD FX devraient pointer le bout de leurs broches la semaine prochaine, Donanimhaber dévoile quelques informations sur l'évolution de l'architecture Bulldozer, Piledriver, qui sera utilisée sur le processeur AM3+ Vishera prévu pour le troisième trimestre 2012.

Désormais dénommé "FX Next", Vishera disposerait grâce à Piledriver de performances améliorées de 10%, d'une nouvelle version du TurboCORE et de nouvelles instructions. Ces instructions seraient de type BMI (Bit Manipulation Instructions) et FMA3 (Fused Multiply Add sur 3 registres).

Le Bulldozer supporte pour rappel le FMA mais avec une implémentation de type FMA4, alors qu'Intel utilisera le FMA3 dans ces prochains processeurs Haswell prévus pour 2013. La différence entre les deux versions est que le FMA4 permet de stocker le résultat d'une opération dans un registre additionnel (d = a x b +c) là ou en FMA3, le résultat doit être stocké dans l'un des registres utilisés précédemment (par exemple : c = a x b + c).

En choisissant de repartir sur le FMA3, AMD s'aligne donc sur le choix d'Intel après de nombreux revirement de situation sur ce point puisque Intel et AMD avaient changé leur fusil d'épaule sur le sujet, Intel ayant présenté d'abord un FMA4 avant d'arriver au FMA3, AMD ayant fait l'inverse. A long termes cette unification des jeux d'instructions est une bonne chose mais Bulldozer pourrait pâtir d'un manque d'optimisations pour son FMA4.