Les contenus liés aux tags Intel et Process

Afficher sous forme de : Titre | FluxIntel ouvre son 22nm

Intel investit pour le 22nm

Intel grave en 22nm

Le 32nm d'Intel en route

Intel ouvre son 22nm

Achronix Semiconductor vient dannoncer un partenariat stratégique avec Intel selon lequel il aura accès aux usines 22nm du géant de Santa Clara. Achronix utilisera les usines dIntel afin de produire un nouveau FPGA (Field Programmable Gate Array) Speedster22i annoncé comme jusquà 300% plus performant, 50% moins gourmand et 40% moins cher que des FPGA concurrents gravés en 28nm.

Achronix Semiconductor vient dannoncer un partenariat stratégique avec Intel selon lequel il aura accès aux usines 22nm du géant de Santa Clara. Achronix utilisera les usines dIntel afin de produire un nouveau FPGA (Field Programmable Gate Array) Speedster22i annoncé comme jusquà 300% plus performant, 50% moins gourmand et 40% moins cher que des FPGA concurrents gravés en 28nm.

Intel se prépare-t-il à devenir une fonderie ouverte aux sociétés tierces ? Pour le moment, cet accès est limité à Achronix et Intel indique que moins de 1% de la capacité de production sera allouée à ce FPGA, le reste des capacités en 22nm étant réservées aux futurs CPU x86. La production en 22nm doit débuter au cours du second semestre 2011.

Intel investit pour le 22nm

Fort de ses résultats records, Intel vient dannoncer un nouvel investissement dans ses usines américaines pour un montant compris entre 6 et 8 milliards de $ (soit 2 trimestres de bénéfices). Les usines Fab 12 et Fab 32, situées en Arizona, et D1C et D1D, situées en Oregon, seront mises à niveau afin de pouvoir graver les futurs processeurs Ivy Bridge 22nm, dont la production doit débuter fin 2011. Une nouvelle usine de développement, D1X, verra pour sa part le jour en Oregon dici à 2013.

Fort de ses résultats records, Intel vient dannoncer un nouvel investissement dans ses usines américaines pour un montant compris entre 6 et 8 milliards de $ (soit 2 trimestres de bénéfices). Les usines Fab 12 et Fab 32, situées en Arizona, et D1C et D1D, situées en Oregon, seront mises à niveau afin de pouvoir graver les futurs processeurs Ivy Bridge 22nm, dont la production doit débuter fin 2011. Une nouvelle usine de développement, D1X, verra pour sa part le jour en Oregon dici à 2013.

Intel grave en 22nm

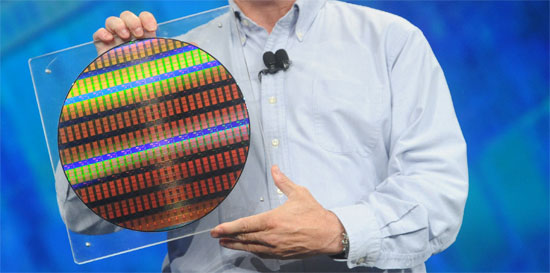

Intel a profité de lIDF pour montrer un wafer de puces SRAM gravées en 22nm. Il sagit des premières puces fonctionnelles au monde basées sur cette finesse de gravure, et comme dhabitude cest la SRAM qui est utilisée pour linaugurer. La puce intègres pas moins de 2.9 milliards de transistors.

Si tout se passe comme prévu, les premiers processeurs utilisant cette technologie devraient voir le jour courant 2011. Conformément au « tic-toc », il sagira dun die-shrink de larchitecture Sandy Bridge qui sera introduite lan prochain en 32nm.

Le 32nm d'Intel en route

Après avoir annoncé en juillet 2007 avoir gravé une puce de SRAM en 32nm, Intel indique quil est désormais arrivé au terme de la phase de développement de sa gravure en 32nm. Il sagit donc maintenant de passer à la phase de production, avec pour objectif de lancer la production en volume au quatrième trimestre 2009.

Après avoir annoncé en juillet 2007 avoir gravé une puce de SRAM en 32nm, Intel indique quil est désormais arrivé au terme de la phase de développement de sa gravure en 32nm. Il sagit donc maintenant de passer à la phase de production, avec pour objectif de lancer la production en volume au quatrième trimestre 2009.

Conformément au désormais célèbre « tic-toc » dIntel, le 32nm sera dans un premier temps utilisé pour un dieshrink de larchitecture actuelle. Le Nehalem 32nm, nom de code Westmere, devrait donc débarquer dans un an environ. Il sera suivi un an plus tard par une nouvelle architecture, toujours en 32nm, Sandy Bridge. Il intégrera lAVX (Advanced Vector Extension), qui nest ni plus ni moins que le successeur du SSE. Les registres passeront de 128 à 256 bits et permettra de travailler sur 3 opérandes, une idée qui sera également intégrée dans le SSE5 dAMD et qui permettra daller plus loin dans la fusion CPU/GPU.