Les derniers contenus liés aux tags Xeon et Skylake

CES: Cartes-mères Gigabyte pour Xeon LGA1151

Intel bloque les Xeon sur les chipsets classiques

Xeon Skylake pour 2017, 28 curs et 6 canaux

AVX3 et PCI Express 4.0 chez Intel

Microcode final pour Spectre chez Intel

La famille Xeon devient Scalable

Xeon Platinum pour accompagner les Xeon Gold

Intel : un Xeon Gold dans les tuyaux ?

Accélération SHA pour Cannonlake

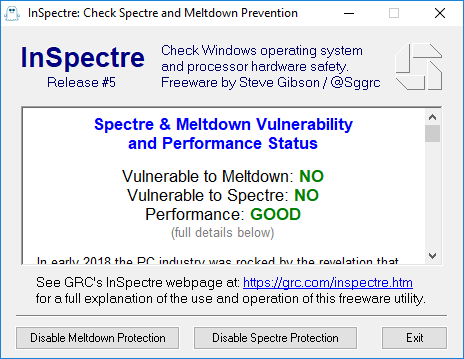

Microcode final pour Spectre chez Intel

Intel vient de publier quelques informations concernant les failles de sécurité Spectre et Meltdown. Après deux bons mois de développement, le constructeur a publié mardi soir une nouvelle version de ses microcode qui contient la version définitive des correctifs pour Spectre. On se souviendra que Microsoft avait désactivé fin janvier son patch pour la variante 2 de Spectre suite aux problèmes de stabilité rencontrés dans certaines situations avec le microcode d'Intel.

L'attente aura été assez longue et la communication d'Intel au compte goutte, mais ce microcode final résout les problèmes de stabilités. Le correctif a été déployé d'après Intel sur toutes les architectures lancées ces cinq dernières années. En pratique, le patch Spectre est désormais disponible pour tous les CPU à partir de Sandy Bridge (les Core "2nde génération" comme les Core i7 2600K) en version classique et HEDT. A ce que nous avons pu voir, l'impact sur les performances ne changerait pas réellement entre la version finale et la version beta de ce microcode que nous avions testé il y a plus d'un mois de cela.

En parallèle, Intel annonce avoir effectué des modifications pour ses prochaines architectures. Le prochain processeur serveur Xeon, connu sous le nom de code Cascade Lake sera protégé nativement contre Meltdown (une faille qui ne touche qu'Intel côté x86) et la variante 2 de Spectre. Intel dit avoir "ajouté des "murs protecteurs" entre les applications et les niveaux de privilèges utilisateurs pour créer un obstacle contre les mauvais acteurs". En plus des Cascade Lake, Intel dit que des processeurs Core 8eme génération attendus pour la deuxième moitié de l'année proposeront aussi ces correctifs. Intel ne précise pas quels CPU sont concernées exactement, la logique voudrait que le constructeur parle de Cascade Lake-X, la déclinaison HEDT de Cascade Lake, même si le constructeur n'a pas pu nous le confirmer.

Corriger de manière matérielle Spectre V2 sera particulièrement important pour les nouvelles architectures d'Intel puisque Skylake, la dernière architecture en date, est assez difficile à sécuriser autrement qu'avec la méthode utilisée par Microsoft pour Windows (communément appelé patch IBRS). Une solution alternative développée par Google, retpoline , est plus difficile à appliquer sur les Skylake dont les mécanismes d'exécution spéculative diffèrent. L'impact de l'IBRS est particulièrement important sur les changements de contextes et les IO pour rappel. Intel n'a pas précisé le coût éventuel sur les performances de ses "murs protecteurs".

Les BIOS incluant ces mises à jour vont être rendus disponibles par les constructeurs dans les jours à venir.

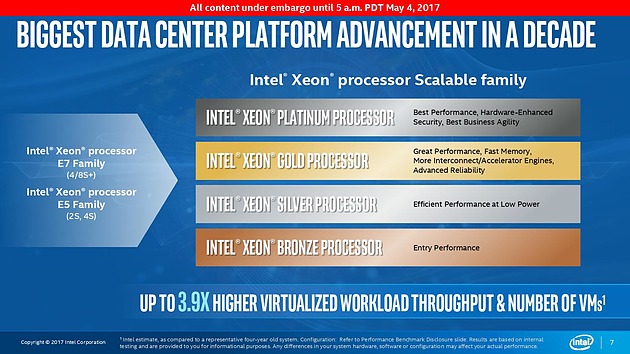

La famille Xeon devient Scalable

Intel vient de dévoiler quelques petits détails sur la future nomenclature de ses processeurs pour serveurs, les Xeon. Quelques informations avaient déjà filtrés la semaine dernière dans un PCN indiquant l'arrivée des marques Xeon Gold et Xeon Platinum pour les séries 6000 et 8000.

Intel proposera donc quatre gammes, les Xeon Bronze, Silver, Gold et Platinum pour remplacer les gammes Xeon E5 et E7. En pratique, Intel n'est pas très précis sur la manière dont il remplira ses gammes colorées, indiquant simplement qu'ils ne se baseront plus sur une segmentation autour du nombre de sockets gérés en simultané, ce qui était visiblement beaucoup trop simple et logique. Une seule nomenclature désormais, Skylake-SP remplacera les gammes E/EP/EX qui permettaient précédemment de distinguer les processeurs en fonction de leur socket/plateforme. Le nom commercial de la famille Xeon sera désormais Scalable.

Au delà de cette palette de couleurs métallisée, Intel ne donne aucune autre information, visiblement fier de présenter cette nouvelle innovation dans sa segmentation. On espère que le constructeur sera un peu plus clair au lancement des Xeon Skylake, prévu pour rappel fin juin/début juillet !

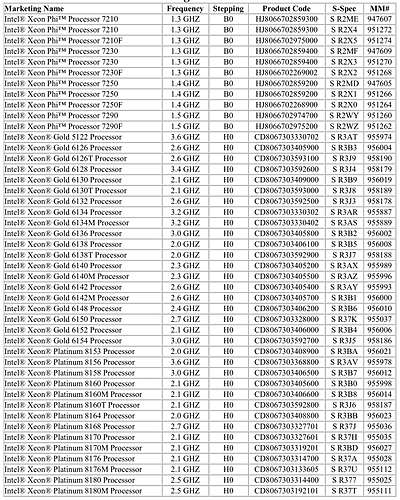

Xeon Platinum pour accompagner les Xeon Gold

Il y a quelques semaines de cela, nous vous indiquions que la nomenclature Xeon Gold devrait faire son apparition à l'occasion du lancement des Skylake-EP, nous faisant nous poser pas mal de question sur ce qui se cachait derrière.

On comprend un peu mieux la question du Gold aujourd'hui grâce à un PCN (PDF) . En pratique, ce PCN (Product Change Notification, un document qui indique un changement au niveau du produit) indique simplement l'ajout d'un marquage supplémentaire sur l'IHS pour pouvoir repérer plus facilement le sens dans lequel insérer ces (bien larges) puces dans les sockets.

Mais en donnant la liste des produits affectés, Intel nous dévoile en parallèle la liste de ses futurs Xeon :

Toutes ces puces utiliseront le futur socket LGA 3647 qui représentera l'offre serveur très haut de gamme du constructeur. Le nombre colossal de broches s'explique par le fait que chaque socket pourra gérer jusque 6 canaux mémoires (avec 3 DIMM par canal). On devrait retrouver des configurations jusque 8 sockets qui pourront accueillir ces nouvelles puces.

La marque Xeon Gold représentera donc les Xeon 6000 tandis qu'une nouvelle marque, Xeon Platinum (!) sera réservée aux modèles 8000. On ne connaît pas encore les différences de cette segmentation (le PCN n'indique que les numéros de modèles, pas encore les caractéristiques) mais historiquement le premier numéro permettait de distinguer le nombre de sockets gérés.

On peut supposer que les modèles 8000 seront réservés pour les modèles 8 sockets, et les 6000 possiblement pour les 4 sockets, même si Intel pourrait changer ses habitudes. Le plus gros des Xeon 8000 intégrera 28 coeurs, soit quatre de plus que l'actuel Xeon E7-8894 v4.

On notera que des Xeon Phi en version socket seront là aussi disponibles, mais ils n'ont pas droit à un métal, on imagine pour éviter toute confusion. Si Intel suit sa logique, on devrait voir arriver des Xeon Silver et Bronze, possiblement pour le socket LGA 2066 qui remplacera l'actuel LGA 2011v3 avec le lancement des Xeon Skylake-W.

La version desktop du LGA 2066 (Skylake-X) a vu son lancement avancé à fin juin/début juillet, avec une introduction probable aux alentours du Computex comme nous vous l'indiquions il y a quelques jours.

Intel : un Xeon Gold dans les tuyaux ?

On trouve dans un test réalisé sous Sandra trace d'un Xeon Gold 6150. Derrière cette dénomination se cache en réalité un Skylake-EP, qui est effectivement attendu pour cette année. Un processeur qui vise avant tout les stations de travail, grâce à ses (très) nombreux coeurs. Skylake-EP est en effet conçu pour en supporter jusqu'à 28.

Le Xeon Gold 6150 est pour sa part doté de 18 coeurs (avec HyperThreading) fonctionnant de 2,4 GHz à 3,7 GHz en Turbo. Ce processeur prend place dans le très encombrant socket LGA3647. Toujours d'après le test Sandra, le Xeon Gold dispose de 1 Mo de cache de niveau 2 par coeur et de 25 Mo de cache de niveau 3, la vitesse mesurée démontrant la présence de l'AVX-512.

Pour rappel, AMD a prévu de sortir un CPU orienté serveur au cours du second trimestre de cette année. Naples sera équipé de pas moins de 32 coeurs.

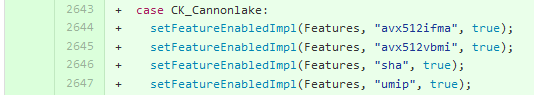

Accélération SHA pour Cannonlake

Quelques petites informations et confirmations sont apparues ce week-end à propos de Cannonlake, la future architecture processeur d'Intel prévue pour la seconde moitié de 2017, et qui sera la première du constructeur à être produite dans un procédé de fabrication 10nm.

Quelques petites informations et confirmations sont apparues ce week-end à propos de Cannonlake, la future architecture processeur d'Intel prévue pour la seconde moitié de 2017, et qui sera la première du constructeur à être produite dans un procédé de fabrication 10nm.

C'est par la publication d'un patch pour Clang, le compilateur C/C++/Obj-C de LLVM que l'on aura obtenu d'abord quelques confirmations sur le support d'AVX-512. Le patch en question que vous pouvez retrouver ici concerne l'énumération des fonctionnalités des familles de processeur. L'intérêt de ce code est de permettre aux développeurs, indépendamment de la machine qu'ils utilisent, de compiler des versions optimisées de leurs programmes pour une architecture donnée (par exemple, optimisée pour Skylake en ajoutant -march=skylake, plus de détails sur le sujet dans cet article).

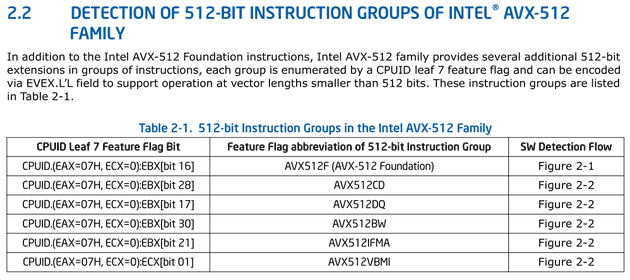

Le patch, en développement depuis début février , indique le support spécifique de certains jeux d'instructions en fonction des familles. On retrouve ainsi les deux déclinaisons de Skylake, la version "client" (celle disponible pour les PC portables et de bureau) et la version "serveur" pour les Xeon. Cette dernière se différencie pour rappel par son support d'une partie du jeu d'instruction AVX-512.

Pour ce patch, Intel ne spécifie qu'une seule version de Cannonlake et l'on retrouve, comme promis, le support des instructions AVX-512. De manière plus précise, en plus des instructions déjà supportées par la version Xeon de Skylake, deux autres extensions sont présentes, avx512ifma et avx512vbmi (une information que nous avions notée l'année dernière). L'extension avx512ifma concerne les instructions dites fused multiply add (par exemple A x B + C), appliquées cette fois ci à des nombres entiers (sur une précision de 52 bits). avx512vbmi rajoute des instructions de manipulation/permutations vectorielles d'octets (Vector Byte Manipulation Instructions).

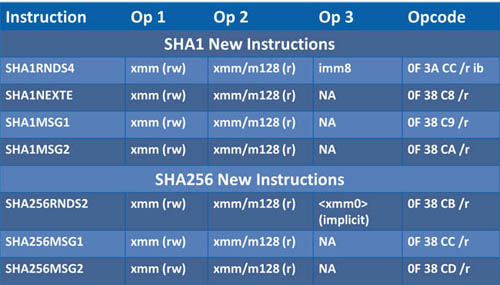

L'autre information est la confirmation de l'arrivée d'instructions dédiées aux calculs de hash cryptographiques. Les instructions sha font, sans trop de doute, référence à ces instructions présentées en 2013 par Intel , capables d'accélérer le calcul de hash aux formats SHA-1 et SHA-256 . Elles devraient être donc introduites pour la première fois sur Cannonlake.

On notera également dans le patch la mention d'une autre extension, umip pour laquelle nous n'avons pas encore trouvé de référence dans la documentation d'Intel !